estudio del filtro fir en presencia de seu

Anuncio

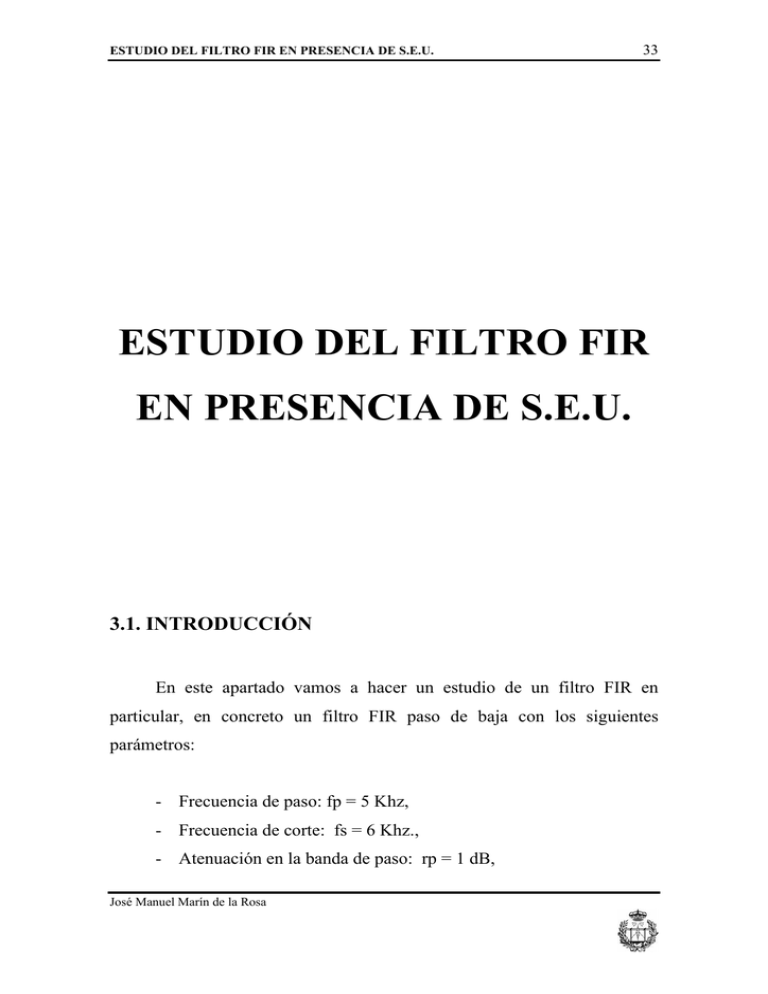

ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 33 ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 3.1. INTRODUCCIÓN En este apartado vamos a hacer un estudio de un filtro FIR en particular, en concreto un filtro FIR paso de baja con los siguientes parámetros: - Frecuencia de paso: fp = 5 Khz, - Frecuencia de corte: fs = 6 Khz., - Atenuación en la banda de paso: rp = 1 dB, José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 34 - Atenuación en la banda de rechazo: rs = 5 dB, - Frecuencia de muestreo: fsim = 48 Khz., Este filtro será el que tendremos que implementar en la FPGA para después estudiar su sensibilidad en presencia de SEU (Single Event Upset). Para implementarlo tendremos que saber sus coeficientes ya que como vimos en el apartado teórico, un filtro FIR se representa mediante tantos retrasos como orden tenga y estas muestras retrasadas de la entrada se van multiplicando por unos coeficientes para, una vez sumadas, obtener la respuesta final deseada. Una vez que sepamos el orden del filtro y los coeficientes, lo que tendremos que hacer es implementarlo en un lenguaje de descripción hardware (VHDL) en el que sólo tendremos que generar los sumadores, multiplicadores y los retrasos (estos se harán con flip-flops). Cuando tengamos implementado el filtro en la FPGA el siguiente paso será comprobar si efectivamente funciona como debe de funcionar, es decir si filtra lo que tiene que filtrar (en nuestro caso todas las componentes frecuenciales por encima de 6 Khz.), para ello lo que haremos será comprobar nuestro filtro “real” implementado en la FPGA con el mismo filtro “teórico” realizado en MATLAB, y comprobando que ambos filtros responde idénticamente (o al menos parecido) ante los mismos estímulos de entrada. José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 35 Llegados a este momento, ya tenemos nuestro filtro FIR implementado en la FPGA, ahora es cuando vamos a hacer un estudio exhaustivo sobre él realizándole diversas pruebas para ver como de sensible es en presencia de SEU. Todos estos pasos lo vamos a ir detallando paso a paso en los siguientes apartados. José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 36 3.2. CARACTERIZACIÓN DEL FILTRO FIR EN MATLAB Una vez que sabemos las especificaciones del filtro, el primer paso que debemos de dar será saber cual es el orden de dicho filtro y cuales son sus coeficientes. Para esto utilizamos MATLAB. Lo primero que tenemos que averiguar es el orden del filtro, para ello, hacemos uso por ejemplo de la aproximación de butterworth y escribiendo la siguiente función en MATLAB: rp=1; rs=5; fp=5000; fs=6000; fsim=48000; wp=2*fp/fsim; ws=2*fs/fsim; [N,Wn]=buttord (wp,ws,rp,rs); En la cual, definimos unas variables con las especificiaciones del filtro, calculamos las frecuencias discretas wp y ws y se las pasamos, junto a las atenuaciones de la banda de paso y de rechazo, como parámetros a la función buttor, y esta nos devuelve en N el orden del filtro, en nuestro caso N = 11. José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 37 Una vez que sabemos el orden del filtro para una aproximación en concreta, solo nos falta por saber los coeficientes del filtro FIR, para ello usamos la función de MATLAB “fir2”, a la cual se le pasa como parámetros el orden del filtro, y un vector de puntos de refenrencias frecuenciales normalizadas y otro vector con la amplitud de dichas frecuencias, por ejemplo: Fir2 (11, [0, 0.2, 0.3, 0.8, 1], [1, 1, 1e-5, 1e-5, 1e-5]); y nos devuelve los coeficientes de nuestro filtro, que son: Coeficiente Valor a0 -0.0033 a1 -0.0058 a2 0.0116 a3 0.0969 a4 0.2305 a5 0.2988 a6 0.2305 a7 0.0969 a8 0.0116 a9 -0.0058 a10 -0.0033 Tabla 1: Coeficientes del filtro FIR Estos son los coeficientes que tendremos que digitalizar para poder implementar el filtro en la FPGA. José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 38 Para comprobar que esto funciona bien, hacemos uso de la herramienta SIMULINK de MATLAB y hacemos el siguiente montaje: Figura 13: Montaje en simulink filtro FIR En la figura 13 lo que hemos realizado ha sido meter un bloque “Discrete filter” en el que le hemos pasado como parámetro, dentro de la variable a2(z) los coeficientes de la tabla 1. Para probarlo, le hemos metido 2 señales de entrada, un seno de gran amplitud a una frecuencia de 3.980 Hz y una señal de ruido de gran potencia, y comprobamos que a la salida se “filtra” la señal sinusoidal limpiándola de ruido. Si simulamos, lo que se obtiene es lo siguiente: José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 39 Figura 14: Salida del filtro FIR Como se observa en la figura 13, en el osciloscopio se mete tanto la entrada como la salida, para poder visualizar las dos señales a la vez. La entrada (señal sinusoidal más ruido) es la señal amarilla, y la señal de salida, la filtrada (que debe de ser solo la sinusoidal) es la señal rosa. Para ver mejor el resultado, vamos a hacer un zoom de la figura 14 y lo mostramos en la figura 15: José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 40 Figura 15: Zoom de la señal de salida del filtro Y en ella se ve claramente como el filtro funciona bien, y a la salida tenemos solamente la señal sinusoidal (discretizada claro está al tratarse de un filtro discreto) y hemos conseguido quitar el ruido. Si hacemos un análisis espectral de nuestro sistema, poniendo a la salida de nuestro filtro FIR un analizador de espectro obtenemos la imagen de la figura 16, en la que podemos ver la señal de salida en el tiempo, la densidad espectral de potencia y la fase. Como cabía de esperar tenemos una sampling centrada a la frecuencia del seno (3.980 hz). José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 41 Figura 16: Análisis espectral de la salida del filtro Si cambiamos el seno de entrada por otro seno de frecuencia 10 Khz. a la salida se tendría que tener un seno “casi” atenuado, ya que la frecuencia de corte de nuestro filtro era de 6 Khz. y la del seno esta por encima de esta frecuencia. Si simulamos, obtenemos la siguiente respuesta: Figura 17: Salida del sistema a 10 Khz. José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 42 El análisis espectral de la salida con una entrada de un seno de 10 Khz. más una componente de ruido es el siguiente: Figura 18: Análisis espectral de la salida con entrada de 10 Khz. En el que se observa claramente en la señal de salida en el tiempo que ya no se tiene un seno tan claro como antes, y que la densidad espectral de potencia no es tan “limpia” como en el caso en el que la señal de entrada era a una frecuencia por debajo de los 5 Khz. de frecuencia de paso de nuestro filtro. Así que con todo esto nuestro filtro queda perfectamente caracterizado. José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 43 3.3. IMPLEMENTACIÓN DEL FILTRO EN LA FPGA Una vez que ya tenemos nuestro filtro perfectamente caracterizado y definido ( El filtro es de orden 11, y sabemos todos sus coeficientes) el siguiente paso será implementarlo en una FPGA, y para ello habrá que escribirlo en lenguaje de programación hardware, que en nuestro caso será el VHDL. La estructura que tenemos que implementar en hardware es la siguiente: Figura 19: Estructura directa filtro FIR Que como vimos en los fundamentos teóricos, se trata de la estrutura directa I. En el dibujo, solo se han representado 8 etapas, pero sabemos que nuestro diseño debe de tener 11 etapas, siguiendo la estructura de la figura 19, que es fácil de implementar. Para nuestro diseño, hemos decidido, que la señal digital que entra en el filtro (X(n)) provenga de digitalizar la señal analógica con 18 bits, así que las muestras de la señal de entrada estarán codificadas con 18 bits, ya José Manuel Marín de la Rosa 44 ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. que así logramos tener una buena precisión. Y los 11 coeficientes de nuestro filtro los vamos a codificar con 9 bits. Lo primero que tenemos que realizar es codificar los coeficientes de la tabla 1 en 9 bits, como lo vamos a codificar con 9 bits, si cuantizamos (multiplicamos por 29) todos los coeficientes y redondeamos al entero más cercano (redondeamos por arriba si el número es positivo y por abajo si el número es negativo) obtenemos la siguiente tabla: Coeficiente Valor Codificación con 9 bits en CA2 a0 -2 111111110 a1 -2 111111110 a2 6 000000110 a3 50 000110010 a4 118 001110110 a5 154 010011010 a6 118 001110110 a7 50 000110010 a8 6 000000110 a9 -2 111111110 a10 -2 111111110 Tabla 2: Coeficientes del filtro Codificados en CA2 con 9 bits Para implementar en hardware la estructura de la figura 19 con N=11, lo que vamos a tener que hacer es modelar los retrasos con flipflops, en nuestro caso 11 flip-flops, a los que le entra un vector de 18 bits y sale otro vector de 18 bits retrasados un ciclo. La salida de cada biestable José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 45 que son las señales X(n-L) son multiplicadas por los coeficientes correspondientes h(L), para implementar dicha multiplicación, usaremos multiplicadores de 18X9 bits, y el resultado lo meteremos en un vector de 27 bits para evitar el overflow. Luego se hace la suma de todas las multiplicaciones (teniendo en cuenta el redondeo, según el resultado sea un número positivo o un número negativo) y por ultimo, el resultado se mete en un vector de salida de 18 bits (así que aquí hacemos truncado del resultado). Esto, a grosso modo, es lo que se ha realizado para implementar el filtro en la FPGA. El código en VHDL, queda de la siguiente manera: ------------------------------------------------------------------------------------------------- Filtro Fir: -Señal digital de entrada de 18 bits -Coeficientes de 9 Bits -Multiplicadores de 18X9 (tantos como coef. se tengan, o sea, tantos como retrasos halla) -Acumulador (sumador) de dichas multiplicaciones -Filtro paso de baja tipo Butterworth, con frecuencia de corte de 5 Khz. -Caso 1: Filtro fir sin redundar ------------------------------------------------------------------------------------------------- -- Bloque para describir los coeficientes del filtro FIR library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; package fir_coef is subtype coef_word is signed(8 downto 0);--coeficientes de 9 bits subtype coef_range is integer range 0 to 10; --numero de coeficientes que hay, o sea, retrasos José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. type coef_table is array (0 to 10) of coef_word; constant coef_rom: coef_table:= ( ("111111110"), ("111111110"), ("000000110"), ("000110010"), ("001110110"), ("010011010"), ("001110110"), ("000110010"), ("000000110"), ("111111110"), ("111111110")); end package fir_coef; -- Filtro Fir library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; use work.fir_coef.all; entity fir is port (clk,reset,load: in std_logic; data_in: in std_logic_vector(17 downto 0); -- señal digital de entrada de 20 bits data_out: out std_logic_vector(17 downto 0); ultima_etapa: out std_logic_vector(17 downto 0)); end fir; architecture a_fir of fir is type fifo_array is array (0 to 10) of signed (17 downto 0); signal fifo,p_fifo: fifo_array; signal data_outi: std_logic_vector(17 downto 0); component regTmr is Generic(N:integer:=18); Port ( clk : in std_logic; reset : in std_logic; d : in signed (N-1 downto 0); José Manuel Marín de la Rosa 46 ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 47 q : out signed (N-1 downto 0)); end component; component regSimple is Generic(N:integer:=18); Port ( clk : in std_logic; reset : in std_logic; d : in signed (N-1 downto 0); q : out signed (N-1 downto 0)); end component; begin sinc:process (reset,clk) begin if reset = '1' then data_out <= (others => '0'); elsif clk'event and clk = '1' then data_out <= data_outi; end if; end process sinc; r0: regSimple Generic map (N=>18) port map (clk => clk, reset => reset, d => p_fifo(0), q => fifo(0)); r1: regSimple Generic map (N=>18) port map (clk => clk, reset => reset, d => p_fifo(1), q => fifo(1)); r2: regSimple Generic map (N=>18) port map (clk => clk, reset => reset, d => p_fifo(2), q => fifo(2)); r3: regSimple Generic map (N=>18) port map (clk => clk, reset => reset, d => p_fifo(3), q => fifo(3)); r4: regSimple Generic map (N=>18) port map (clk => clk, reset => reset, d => p_fifo(4), q => fifo(4)); r5: regSimple José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 48 Generic map (N=>18) port map (clk => clk, reset => reset, d => p_fifo(5), q => fifo(5)); r6: regSimple Generic map (N=>18) port map (clk => clk, reset => reset, d => p_fifo(6), q => fifo(6)); r7: regSimple Generic map (N=>18) port map (clk => clk, reset => reset, d => p_fifo(7), q => fifo(7)); r8: regSimple Generic map (N=>18) port map (clk => clk, reset => reset, d => p_fifo(8), q => fifo(8)); r9: regSimple Generic map (N=>18) port map (clk => clk, reset => reset, d => p_fifo(9), q => fifo(9)); r10: regSimple Generic map (N=>18) port map (clk => clk, reset => reset, d => p_fifo(10), q => fifo(10)); regs: process(load,fifo,data_in) begin if load = '1' then for i in 1 to 10 loop p_fifo(i) <= fifo(i-1); end loop; p_fifo (0) <= signed (data_in); else for i in 0 to 10 loop p_fifo(i) <= fifo(i); end loop; end if; end process regs; firstruct: process (fifo) variable prod: signed (26 downto 0); variable idata_tmp: signed (19 downto 0); variable data_tmp: signed (17 downto 0); begin data_tmp := (others => '0'); for i in 0 to 10 loop José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 49 prod := fifo(i) * coef_rom(i); if (prod(26)='1') then prod:=prod+255; --redondeo end if; idata_tmp := (data_tmp(17)&data_tmp(17)&data_tmp) + (prod(26)&prod(26)&prod(26 downto 9)); if idata_tmp(19 downto 18) = "01" then -significa que desborda por arriba data_tmp:=(17=>'0',others=>'1'); elsif idata_tmp(19 downto 18) = "10" then -significa que desborda por abajo data_tmp:=(17=>'1',others=>'0'); - else data_tmp:=idata_tmp(17 downto 0); end if; end loop; data_outi <= std_logic_vector (data_tmp); end process firstruct; ultima_etapa <= (others =>'0'); end a_fir; Este código, junto con la descripción de los componentes, y los sucesivos códigos que debemos de generar para realizar las pruebas oportunas se adjuntan al final de la documentación en el apartado “Anexos”. Una vez que ya tenemos implementado nuestro filtro FIR en la FPGA, lo que tenemos que hacer es probar si realmente funciona bien, para ello, como dijimos anteriormente, lo que vamos a hacer es compararlo con el filtro “teórico” que caracterizamos en MATLAB, para ello, a los dos le vamos a meter la misma entrada, y por lo tanto deberíamos de obtener “parecidas” salidas. Para meterle al filtro que tenemos en la FPGA la misma entrada que al que tenemos generado en MATLAB, tenemos que meter la entrada en un José Manuel Marín de la Rosa 50 ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. fichero, para hacer eso, como vemos en la figura 12 la señal de entrada la hacemos pasar por un cuantizador para cuantizarla, después la hacemos pasar por un convertidor, para convertirla a un entero, y posteriormente ese resultado lo guardamos en una variable con nombre “Entrada1”, el contenido de esa variable lo pasamos a un fichero, para que, generando el código VHDL oportuno, se le pase dicho fichero como parámetro de entrada a nuestro filtro, y genere otro fichero, que se llame “fichero_de_salida” el cual debemos de comparar con el contenido de la variable “Salida” que se genera a la salida del filtro fir de MATLAB. Si vemos un “trocito” de dichos ficheros (los ficheros completos se expondrán en el anexo) podemos ver los resultados. El contenido de la variable “Entrada1”,que se obtuvo haciendo la simulación en SIMULINK, y que será el contenido de el “fichero_de_entrada” que se le va a pasar al filtro fir de la FPGA es el siguiente: 55232 131071 -19665 131071 131071 6925 -131072 -42095 -22712 -91978 -36006 8165 -25592 131071 30943 -131072 -123440 José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 51 131071 -60393 -131072 -131072 -131072 -131072 -131072 -41356 131071 120188 131071 131071 125974 -80548 -127333 -131072 -131072 131071 77463 -117338 -97165 82961 131071 77966 -122143 -127018 -56718 74885 -131072 22310 . . . . . En la variable “Salida” obtenida en SIMULINK se tiene los siguientes datos: José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. -215 -727 212 6494 24274 45896 62441 73451 77939 57781 10047 -36816 -55662 -55306 -47519 -32944 -6155 21507 26957 -2367 -35016 -38912 -29105 -45700 -85468 -117894 -127643 -117936 -79567 -13482 58438 107103 123037 104276 49421 -26336 -85322 -91846 -47561 -834 3607 -17750 José Manuel Marín de la Rosa 52 ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 53 . . . . . Que si lo comparamos con el “fichero_de_salida” que genera la FPGA: -216 -728 211 6492 24274 45895 62439 73448 77936 57778 10044 -36821 -55665 -55308 -47519 -32946 -6158 21503 26954 -2372 -35020 -38916 -29108 -45702 -85471 -117896 -127644 -117938 -79569 -13484 58435 José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 54 107099 123034 104274 49418 -26338 -85325 -91849 -47564 -837 3604 -17754 . . . . Como se observa, la salida de ambos filtros son prácticamente idénticas, los errores que se tienen son errores difíciles de evitar debido a los redondeos y truncamientos que se hacen en el filtro digital para obtener la salida. José Manuel Marín de la Rosa 55 ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 3.4. ESTUDIO EXHAUSTIVO DEL FILTRO FIR. PRUEBAS REALIZADAS. Llegados a este punto, empezamos, ahora sí, a estudiar el verdadero propósito de ésta investigación, que no es otro sino que estudiar el comportamiento de filtros en presencia de SEU. Vamos a comenzar estudiando el filtro FIR, para después, hacer lo propio con un filtro IIR y así poder comparar los resultados obtenidos. Como sabemos, cuando un circuito electrónico se encuentra en presencia de SEU, éste puede hacer que varíe algunas de las propiedades físicas de dicho circuito, haciendo que el resultado obtenido a la salida no sea el esperado. Nosotros, para “simular” ese SEU, vamos introducir errores en distintas partes de nuestro filtro (como si esos errores fueran provocados por el SEU) y vamos a ver como se comporta nuestro filtro, comparando la salida “ideal” que daría sin introducir fallos con la salida que se obtiene introduciendo estos fallos “voluntariamente”. Para introducir estos “errores” vamos a hacer uso de una herramienta diseñada en la Universidad de Sevilla por AICIA-GTE, ESA en un proyecto denominado “FT-UNSHADES” más en concreto de las publicaciones: “FT-UNSHADES Design Preparation Tools” y “FT-UNSHADES Design Test and Analysis Tools” cuya documentación está incluida en los anexos de esta memoria. A grosso modo esta herramienta lo que hace es crear en la FPGA 2 copias del sistema a estudiar y unos vectores para testearlas. Una de las José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 56 copias será la ide., sin fallos, y metiéndole los vectores de entrada, obtenemos las salidas correspondientes a esos vectores. En la otra copia es en la que se introduce fallos en distintos sitios (como si esos fallos fuesen producidos por el SEU) se le meten los mismos vectores de entrada y compara la salida de esta con la anterior, si es la misma es que el fallo introducido no ha producido errores, si la salida es distinta, quiere decir que el fallo que se ha introducido (y sabemos dónde) produce fallo. Los fallos que se meten en la copia del diseño, se introducirán muchas veces en distintos tiempos, por eso algunas veces introducir un error en un registro en concreto de nuestro diseño puede dar fallos o no, dependiendo de el ciclo de reloj en el que se encuentre. Con ésta información vamos a intentar hacer un “mapa” de nuestro filtro viendo donde si se produce fallo en ese sitio es mas “grave” para nuestro sistema, ya que como veremos, habrá bits en los cuales, aunque se introduzca un fallo, la salida no lo notará y será igual que la “ideal”, mientras que habrá otros bits, en los cuales si se tiene un fallo en ese bit, será crítico para nuestro filtro, ya que un fallo en ese bit puede que siempre produzca un fallo en la salida. Esa será nuestra primera misión, después, una vez realizado eso vamos a introducir triple redundancia modular en nuestro filtro y elección por mayoría, o sea, replicar nuestro diseño tres veces y elegir la salida mediante “votación” de los tres. Veremos que si redundamos todos los registros de nuestro filtro, aunque se produzcan fallos dentro de algún registro, nunca se tendrá error a la salida, o sea, esto sería lo ideal, ya que tendríamos un 0% de fallos a la salida en presencia de SEU, pero claro está José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 57 también es la solución mas cara, ya que redundar todo el sistema, es 3 veces mas caro que el circuito original. Por todo esto, lo q vamos a intentar es hacer un estudio que consistirá en ver que registros internos del filtro “merecen la pena” redundar, y cuales no. Redundaremos aquellos en los cuales un error en ese registro tenga un alto porcentaje de que produzca un error a la salida, y no redundaremos aquellos registros en los cuales un error en ellos tenga un porcentaje muy bajo de que se produzca error a la salida. Para hacer esto creamos en VHDL 2 módulos, uno que será el registro simple, que será un registro normal (biestable) con un vector de entrada y de salida de 18 bits, y un registro que llamaremos registroTmr, el cual tendrá triple redundancia modular, ya que será un registro que está triplicado. (los códigos están en el anexo). Y “jugaremos” poniendo en nuestro filtro algunos registros como registros simples y otros como registrosTmr y viendo los resultados. José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 58 3.4.1. PRUEBAS REALIZADAS El siguiente paso que dimos, una vez realizado todo lo anterior, fue la realización de diversas pruebas, redundando partes de nuestro circuito, y comparar los recursos (biestables) consumidos con la eficiencia del filtro, ya que como dijimos antes, si se redunda todo el sistema estamos seguros de que se tendrá un 100% de eficiencia, pero claro está pagando el mas alto precio en recursos. Habrá aplicaciones, en las que claro está, se requerirá que el sistema tenga un 100% de eficiencia, por ejemplo en sistemas integrados en aplicaciones críticas como pueden ser sistemas para proyectos espaciales, circuitos electrónicos de láser para operaciones oculares (imaginad por un instante que ese láser falla por un momento, sería un desastre para la operación y podría dejar ciega de por vida a la persona en cuestión), etc,…. Está claro que para estas aplicaciones no se repara en recursos y se redundaría el sistema un 100% para evitar desastres. Sin embargo, hay otras muchas aplicaciones, como por ejemplo contadores de surtidor de gasolina, circuitos de electrodomésticos, y de propósito general, en los que no se requieren un 100% de eficiencia, son en estos circuitos en los que se busca una mejor relación eficiencia-precio y para ello se estudia que es lo que merece la pena redundar y que no. José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 59 Para estudiar nuestro filtro FIR, hemos realizado diversas pruebas, en concreto 11, para ver donde se producen más fallos, y estudiar la mejor relación eficiencia-precio de nuestro sistema. Las pruebas consisten en introducir 10.000 errores en distintos lugares y en distintos momentos en nuestro diseño y ver si esos errores producen fallos en la salida o no. PRUEBA 1: La primera prueba que realizamos fue ver como funcionaba nuestro filtro sin protección, o sea, sin redundar nada, en presencia de SEU, y los resultados fueron los siguientes: - Recursos utilizados : 204 flip-flops, - Eficiencia: 18 % Como se observa, se tienen muchos errores, se consigue una eficiencia muy baja. Si se observa el fichero resultante de realizar la prueba 1 (en CD adjunto) se ve que los errores son más críticos cuanto más cerca de la entrada se produce, o sea, que los registros más críticos son los las cercanos a la entrada, el registro0, el registro1, el registro2… y así sucesivamente, y dentro de los registros son mucho mas críticos los errores que se producen en los bits altos, ya que un error en un bit alto produce error seguro a la salida. A modo de resumen, detallo donde alguna vez no se produce fallos, aunque se introduzca ahí un error (otras veces sí): Registro 0, reigstro 1, registro 2, registro 3, registro 4, registro 5: En estos registros no siempre se tiene fallo en la salida si se introduce un error en los bits 0 y 1. Si se introduce el error en los otros bits, siempre se tiene fallo en la salida. José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 60 Registro 6: No siempre se tiene fallo en la salida si se introduce un error en los bits 0, 1 y 2. Si se introduce en los demás si. Registro 7: No siempre se tiene fallo en la salida si se introduce un error en los bits 0, 1, 2 y 3. Si se introduce en los demás si. Registro 8: No siempre se tiene fallo en la salida si se introduce un error en los bits que van del 0 al 6, en los demás si. Registro 9 y registro 10: No se produce fallo en la salida si se introduce un error en los bits que van del 0 al 7 en los demás sí. En conclusión, los bits mas significativos son críticos!, ya que un error en ellos da lugar a fallo seguro en la salida, y mirando los registros, los registros mas cercanos a la entrada son más críticos que los que están mas cercanos a la salida. (Código VHDL en anexos) PRUEBA 2: La siguiente prueba que hicimos fue redundando todo el sistema. Como cabría de esperar tuvimos un 100 % de eficiencia por eso no anexo el fichero de salida de esta prueba, ya que es obvio como sería. - Recursos utilizados: 612 flip-flops, - Eficiencia: 100% Como se observa, se tiene 3 veces mas de recursos que en el caso anterior. (Código en Anexos) José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. PRUEBA 3: 61 Visto el resultado de la primera prueba, lo primero que debemos de hacer es empezar a redundar los registros mas bajo, y así vamos a empezar. En esta tercera prueba lo que vamos a hacer es lo siguiente: Registro 0: Totalmente redundado (ya que es el más importante) Registro 1: Totalmente redundado menos el bit menos significativo Registro 2: Totalmente redundado menos los 2 bits menos significativos. Registro 3: Totalmente redundado menos los 3 bits menos significativos. Registro 4: Totalmente redundado menos los 4 bits menos significativos. Registro 5: Totalmente redundado menos los 5 bits menos significativos. Registro 6: Totalmente redundado menos los 6 bits menos significativos. Registro 7: Totalmente redundado menos los 7 bits menos significativos. Registro 8: Totalmente redundado menos los 8 bits menos significativos. Registro 9: Totalmente redundado menos los 9 bits menos significativos. Registro 10: Totalmente redundado menos los 10 bits menos significativos. José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 62 Realizamos esta prueba en VHDL (código en Anexos) y la analizamos, obteniendo los siguientes resultados: - Recursos utilizados: 502 flip-flops - Eficiencia 93.56% Como vemos, hemos conseguido quitar un número considerable de flip-flops (110) y seguimos teniendo un elevado porcentaje de eficiencia que es de mas del 93%. (El fichero con el resultado en CD adjunto). Viendo el fichero de salida, se observa, como cabría esperar, que los fallos se tienen en los bits más significativos de cada registro, que son los que no están redundados. Y como en esos bits eran en los que menos fallos se tenían sin redundar por esa razón baja nuestra tasa de fallos. PRUEBA 4: En esta prueba vamos a intentar utilizar menos recursos, o sea redundar un poco menos, pero intentando mantener el porcentaje de eficiencia. La prueba que vamos a realizar es la siguiente: Registro 0: Totalmente redundado (ya que es el más importante) Registro 1: Totalmente redundado menos los 2 bits menos significativos. Registro 2: Totalmente redundado menos los 3 bits menos significativos. Registro 3: Totalmente redundado menos los 4 bits menos significativos. José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 63 Registro 4: Totalmente redundado menos los 5 bits menos significativos. Registro 5: Totalmente redundado menos los 6 bits menos significativos. Registro 6: Totalmente redundado menos los 7 bits menos significativos. Registro 7: Totalmente redundado menos los 8 bits menos significativos. Registro 8: Totalmente redundado menos los 9 bits menos significativos. Registro 9: Totalmente redundado menos los 10 bits menos significativos. Registro 10: Totalmente redundado menos los 11 bits menos significativos. Realizamos esta prueba en VHDL (código en Anexos) y la analizamos, obteniendo los siguientes resultados: - Recursos utilizados: 482 flip-flops - Eficiencia 91.28% Hemos reducido los recursos utilizados con respecto a la prueba anterior en 20 flip-flops con apenas notarse la eficiencia, ya que sigue siendo bastante alta con más del 91% de eficiencia. José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 64 PRUEBA 5 : En esta prueba vamos a seguir intentando utilizar menos recursos que en la anterior, siempre manteniendo el porcentaje de eficiencia relativamente alto. En esta haremos lo siguiente: Registro 0: Totalmente redundado (ya que es el más importante) Registro 1: Totalmente redundado menos los 3 bits menos significativos. Registro 2: Totalmente redundado menos los 4 bits menos significativos. Registro 3: Totalmente redundado menos los 5 bits menos significativos. Registro 4: Totalmente redundado menos los 6 bits menos significativos. Registro 5: Totalmente redundado menos los 7 bits menos significativos. Registro 6: Totalmente redundado menos los 8 bits menos significativos. Registro 7: Totalmente redundado menos los 9 bits menos significativos. Registro 8: Totalmente redundado menos los 10 bits menos significativos. Registro 9 : Totalmente redundado menos los 12 bits menos significativos. Registro 10: Totalmente redundado menos los 13 bits menos significativos. José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 65 Realizamos esta prueba en VHDL (código en Anexos) y la analizamos, obteniendo los siguientes resultados: - Recursos utilizados: 462 flip-flops - Eficiencia: 88.33% Hemos vuelto a reducir los recursos utilizados, en concreto en 20 flip-flops con respecto a la prueba anterior, y la eficiencia la podemos seguir considerando bastante alta (según para la aplicación que se quiera claro está) con un 88.33% PRUEBA 6: En esta prueba haremos: Registro 0: Totalmente redundado (ya que es el más importante) Registro 1: Totalmente redundado menos los 4 bits menos significativos. Registro 2: Totalmente redundado menos los 5 bits menos significativos. Registro 3: Totalmente redundado menos los 6 bits menos significativos. Registro 4: Totalmente redundado menos los 7 bits menos significativos. Registro 5: Totalmente redundado menos los 8 bits menos significativos. Registro 6: Totalmente redundado menos los 9 bits menos significativos. José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 66 Registro 7: Totalmente redundado menos los 10 bits menos significativos. Registro 8 : Totalmente redundado menos los 12 bits menos significativos. Registro 9: Totalmente redundado menos los 13 bits menos significativos. Registro 10: Totalmente redundado menos los 14 bits menos significativos Realizamos esta prueba en VHDL (código en Anexos) y la analizamos, obteniendo los siguientes resultados: - Recursos utilizados: 442 flip-flops - Eficiencia: 85.02% Como se sigue observando, seguimos reduciendo los recursos, y la eficiencia sigue siendo relativamente alta. PRUEBA 7: En esta prueba vamos a cambiar un poco nuestra forma de actuar hasta ahora. Hasta el momento hemos visto que si vamos dejando sin redundar los bits LSB de los registros, vamos ahorrando en recursos y conseguimos mantener la eficiencia bastante alta (siempre por encima del 85%, por lo visto hasta ahora). En esta prueba y la siguiente vamos a investigar otra cosa, y es ver que registro son los más importantes, si los registros pares o los registros impares. José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 67 En esta prueba vamos a redundar los registros pares y no los impares y vamos a ver que resultados se obtiene, mientras que en la siguiente vamos a hacer lo contrario, o sea, redundar los impares y no los pares, y veremos en cual de las dos se obtiene mejores resultados. Registro 0: Totalmente redundado Registro 1: Totalmente sin redundar Registro 2: Totalmente redundado Registro 3: Totalmente sin redundar Registro 4: Totalmente redundado Registro 5: Totalmente sin redundar Registro 6: Totalmente redundado Registro 7: Totalmente sin redundar Registro 8: Totalmente redundado Registro 9: Totalmente sin redundar Registro 10: Totalmente redundado Realizamos esta prueba en VHDL (código en Anexos) y la analizamos, obteniendo los siguientes resultados: - Recursos utilizados: 432 flip-flops - Eficiencia: 80.89% José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. PRUEBA 8: 68 Y ahora hacemos lo contrario, redundamos los registros impares totalmente, y dejamos sin redundar los pares Registro 0: Totalmente sin redundar Registro 1: Totalmente redundado Registro 2: Totalmente sin redundar Registro 3: Totalmente redundado Registro 4: Totalmente sin redundar Registro 5: Totalmente redundado Registro 6: Totalmente sin redundar Registro 7: Totalmente redundado Registro 8: Totalmente sin redundar Registro 9: Totalmente redundado Registro 10: Totalmente sin redundar Realizamos esta prueba en VHDL (código en Anexos) y la analizamos, obteniendo los siguientes resultados: - Recursos utilizados: 396 flip-flops - Eficiencia: 72.60% A vista de los resultados obtenidos, parece mejor redundar los registros pares que los impares, esto más o menos se esperaba por dos motivos: 1.- Hay mas registros pares que impares, si se redundan los pares, se redundan más registros que cuando redundamos los impares, eso se ve en los recursos usados, ya que para la prueba 7 se usan 432 flip-flops, mientras José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 69 que para la 8 sólo 396. Así que si se tiene más redundancia, claro está que se tendrá mejores resultados. 2.- El segundo motivo es porque como vimos en la prueba 1, los registros que están más cerca de la entrada son más importantes y más sensible a los errores introducidos. Al tomar el registro 0 como registro par lo redundamos en la prueba 7 y no en la 8 y por eso en la 7 se obtienen mejores resultados que en la prueba 8. Si queremos comprobar si es mejor redundar los pares que los impares, lo que podemos hacer es realizar una nueva prueba en la que se redundan solo los registros impares y no los pares pero además también redundamos el registro 0 totalmente. Eso es lo que haremos en la siguiente prueba. PRUEBA 9: Redundamos todos los registros impares y además el registro 0, y los demás los dejamos sin redundar. Registro 0: Totalmente redundado Registro 1: Totalmente redundado Registro 2: Totalmente sin redundar Registro 3: Totalmente redundado Registro 4: Totalmente sin redundar Registro 5: Totalmente redundado Registro 6: Totalmente sin redundar Registro 7: Totalmente redundado Registro 8: Totalmente sin redundar José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 70 Registro 9: Totalmente redundado Registro 10: Totalmente sin redundar Realizamos esta prueba en VHDL (código en Anexos) y la analizamos, obteniendo los siguientes resultados: - Recursos utilizados: 432 flip-flops - Eficiencia: 83.09% Ahora si podemos comprobar los resultados de esta prueba, con los obtenidos en la prueba 7, ya que tenemos el mismo número de flip-flops en las dos. Pues bien, se observa que por muy poco, apenas el 3% es mejor redundar los impares (más el registro 0) que los pares (más el registro 0). Esto también puede tener una explicación, y es que, como dijimos en la prueba 1, los registros más sensibles son los más cercanos a la entrada, si en las dos pruebas tenemos redundado el registro 0 que es el más cercano, el siguiente en importancia es el registro 1, y ese se redunda por completo en los impares (prueba 9) y no en los pares (prueba 7) de ahí los resultados obtenidos. Por último, vamos a comprobar que es más útil redundar, si los 9 bits más significativos o los 9 bits menos significativos de cara registro. Para ello vamos a hacer 2 pruebas, 1 en la que vamos a redundar los 9 bits más significativos de todos los registros dejando si redundar los 9 LSB, y después haremos la prueba complementaria, es decir redundar los 9 bits menos significativos y dejar sin redundar los 9 MSB de cada registro. José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 71 PRUEBA 10: Redundaremos los 9 bits MSB de cada registro, y dejar sin redundar los 9 bits LSB. Registro 0: 9 MSB redundados y los 9 LSB sin redundar. Registro 1: 9 MSB redundados y los 9 LSB sin redundar. Registro 2: 9 MSB redundados y los 9 LSB sin redundar. Registro 3: 9 MSB redundados y los 9 LSB sin redundar. Registro 4: 9 MSB redundados y los 9 LSB sin redundar. Registro 5: 9 MSB redundados y los 9 LSB sin redundar. Registro 6: 9 MSB redundados y los 9 LSB sin redundar. Registro 7: 9 MSB redundados y los 9 LSB sin redundar. Registro 8: 9 MSB redundados y los 9 LSB sin redundar. Registro 9: 9 MSB redundados y los 9 LSB sin redundar. Registro 10: 9 MSB redundados y los 9 LSB sin redundar Realizamos esta prueba en VHDL (código en Anexos) y la analizamos, obteniendo los siguientes resultados: - Recursos utilizados: 414 flip-flops - Eficiencia: 81.78% RUEBA 11: Redundaremos los 9 LSB de cada registro y dejaremos sin redundar los 9 MSB. Registro 0: 9 LSB redundados y los 9 MSB sin redundar. Registro 1: 9 LSB redundados y los 9 MSB sin redundar. Registro 2: 9 LSB redundados y los 9 MSB sin redundar. José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 72 Registro 3: 9 LSB redundados y los 9 MSB sin redundar. Registro 4: 9 LSB redundados y los 9 MSB sin redundar. Registro 5: 9 LSB redundados y los 9 MSB sin redundar. Registro 6: 9 LSB redundados y los 9 MSB sin redundar. Registro 7: 9 LSB redundados y los 9 MSB sin redundar. Registro 8: 9 LSB redundados y los 9 MSB sin redundar. Registro 9: 9 LSB redundados y los 9 MSB sin redundar. Registro 10: 9 LSB redundados y los 9 MSB sin redundar. Realizamos esta prueba en VHDL (código en Anexos) y la analizamos, obteniendo los siguientes resultados: - Recursos utilizados: 414 flip-flops - Eficiencia: 76.02% Como podemos observar se obtiene mejores resultados si redundamos los 9 bits MSB que si redundamos los 9 bits LSB, esto ya era algo previsible, pues como hemos ido observando en las pruebas anteriores, los bits MSB son más sensibles que los LSB, ya que si uno de ellos falla por cualquier motivo con una gran probabilidad se va a tener error en la salida de nuestro filtro. Así que es mucho más importante redundar los bits más significativos que redundar los bits menos significativos. José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. 73 3.4.2. CONCLUSIONES FILTRO FIR Tras haber realizado todas estas pruebas para intentar estudiar la sensibilidad de un filtro FIR en presencia de SEU, llegamos a las siguientes conclusiones: 1.- Los registros más sensibles, o sea con mayor porcentaje de que al introducir en ellos un fallo se tenga un error en la salida, son los registros más cercanos a la entrada. Algo que puede ser comprensible, ya que si se produce un fallo en la primera etapa del filtro ese error se va a ir “multiplicando” en las demás etapas y casi con toda probabilidad va a producir un error en la salida de nuestro sistema. A la vez que nos vamos acercando a la salida, un fallo en un registro más cercano a ella es menos problemático. 2.- Los bits más sensibles de cada registro, o sea los que tienen mayor porcentaje de que al provocar un fallo en ellos se tenga un error en la salida, son los bits más significativos (los MSB). 3.- Si queremos un filtro que sea bastante tolerante a los SEU los más importante de redundar son siempre los registros más cercanos a la entrada, o sea las primeras etapas del filtro y también redundar siempre los bits más significantes de las etapas. Ya que haciendo esto, hemos visto que podemos obtener filtros bastante eficientes y ahorrando gran cantidad de recursos. José Manuel Marín de la Rosa ESTUDIO DEL FILTRO FIR EN PRESENCIA DE S.E.U. José Manuel Marín de la Rosa 74