Descargar archivo adjunto

Anuncio

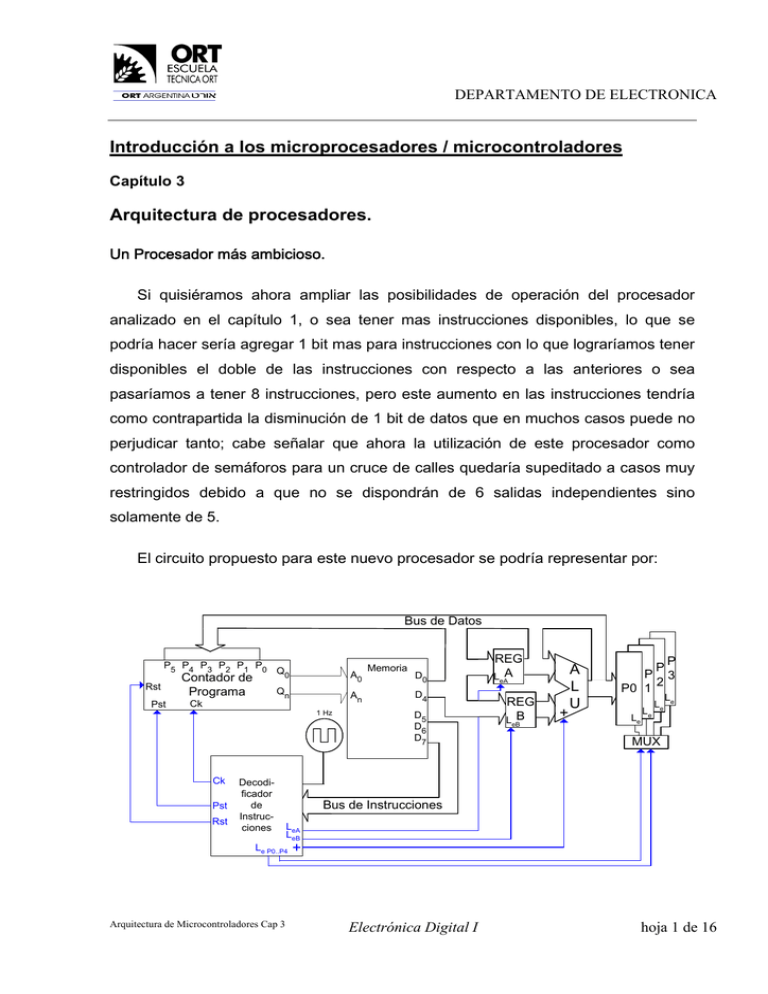

DEPARTAMENTO DE ELECTRONICA Introducción a los microprocesadores / microcontroladores Capítulo 3 Arquitectura de procesadores. Un Procesador más ambicioso. Si quisiéramos ahora ampliar las posibilidades de operación del procesador analizado en el capítulo 1, o sea tener mas instrucciones disponibles, lo que se podría hacer sería agregar 1 bit mas para instrucciones con lo que lograríamos tener disponibles el doble de las instrucciones con respecto a las anteriores o sea pasaríamos a tener 8 instrucciones, pero este aumento en las instrucciones tendría como contrapartida la disminución de 1 bit de datos que en muchos casos puede no perjudicar tanto; cabe señalar que ahora la utilización de este procesador como controlador de semáforos para un cruce de calles quedaría supeditado a casos muy restringidos debido a que no se dispondrán de 6 salidas independientes sino solamente de 5. El circuito propuesto para este nuevo procesador se podría representar por: Bus de Datos Rst P5 P4 P3 P2 P1 P0 Q0 Contador de Pst Programa A0 Qn An Ck 1 Hz Ck Pst Rst Decodificador de Instrucciones D0 D4 D5 D6 D7 REG L A eA REG L B eB + A L U P P P 3 2 P0 1 Le Le Le Le MUX Bus de Instrucciones LeA LeB Le P0..P4 Arquitectura de Microcontroladores Cap 3 Memoria + Electrónica Digital I hoja 1 de 16 DEPARTAMENTO DE ELECTRONICA Este circuito permite realizar la operación suma mediante el bloque que hemos denominado ALU ( Unidad Aritmético Lógica ), aunque para nuestro caso alcanzaría solamente con un circuito sumador. Se denominó con el término Bus de Instrucciones a las líneas por las cuales circula la información correspondiente a los bits D5 ... D7 , estos datos son tomados por el decodificador de instrucciones que activará las distintas líneas de comando las cuales irán habilitando tanto sean las que controlan al contador como las que habilitan los registros, puertos o la entrada + de la ALU. Por el Bus de Datos circulará la información correspondiente a los datos con los que este procesador operará, estos datos pueden ser de varios tipos, ya sean los de la operación a realizar, los que correspondan a la dirección a la cual se quiera producir un salto de programa, o al puerto por el cual se quiera mostrar el resultado de la operación suma que sale de la ALU. El decodificador de instrucciones cada vez que deba realizar la operación suma, ejecutará distintas operaciones, primero habilitar el comando suma que realizará la operación referida entre el Registro A y el Registro B, luego y dentro del mismo ciclo de máquina se deberá accionar el latch enable LeA para que el resultado de la operación quede almacenado en el registro A al cual llamaremos acumulador. Como puede observarse la operación suma engloba a varias sub-operaciones que se realizan dentro del mismo ciclo de máquina; esto ocurrirá también con otro tipo de instrucciones. Como ahora se disponen de 3 bits para las instrucciones se podrán realizar 8 posibles operaciones diferentes con este procesador. Estas operaciones las podemos sintetizar el el juego de instrucciones detallado a continuación. Arquitectura de Microcontroladores Cap 3 Electrónica Digital I hoja 2 de 16 DEPARTAMENTO DE ELECTRONICA El nuevo “set” de instrucciones será: D7 D6 D5 Abreviaturas 0 0 0 STOP 1 0 0 CONT 0 1 0 RST 1 1 0 JMP 0 0 1 CARGA A 1 0 1 CARGA B 0 1 1 SUMA AB 1 1 1 OUT Operación que se realiza El contador de programa se bloquea, deteniéndose la ejecución del programa. El contador de programa queda habilitado para continuar ejecutando el programa El contador de programa (PC) se resetea reiniciándose la ejecución del programa. El “ PC ” se presetea con el valor a donde saltará y proseguirá con la ejecución del programa. Se habilita el LeA para que el dato que acompaña a la instrucción, sea cargado en el registro A. Se habilita el LeB para que el dato que acompaña a la instrucción, sea cargado en el registro B. La ALU realiza la operación suma el registro A con el registro B y carga el resultado en el registro A. Se habilita el puerto P0 ... P3 correspondiente, por dónde saldrá el valor del registro acumulador A. Como se podrá observar, las cuatro primeras instrucciones son iguales a las del procesador de 2 bits de instrucciones, por lo que si se pone el bit D5 en “0” un programa hecho para funcionar con el procesador anterior puede utilizarse en este procesador sin realizar ningún cambio en el programa, a esto se lo denomina compatibilidad hacia atrás, por lo que los programas anteriores siguen manteniendo su vigencia. Este caso se presentó por ejemplo al realizarse el cambio de las computadoras personales PC XT (procesador de 8 bits ) a las PC AT ( procesador de 16 bits ). Arquitectura de Microcontroladores Cap 3 Electrónica Digital I hoja 3 de 16 DEPARTAMENTO DE ELECTRONICA Se mostrará el uso de este procesador con tres ejemplos: El programa debe tener las instrucciones necesarias para que el procesador • realice la suma del número 2 con el número 3 y muestre el resultado por el puerto 1. Para el desarrollo de este programa realizaremos primero un diagrama de flujos que muestre el proceso a seguir, aunque para programas muy sencillos resulta muy obvio. C A 2 B 3 A A+B P1 A F Las instrucciones de este programa podrían escribirse de la siguiente manera: PC 00 01 02 03 04 05 D7 0 1 0 1 0 D6 0 0 1 1 0 D5 1 1 1 1 0 Arquitectura de Microcontroladores Cap 3 D4 0 0 X 0 X D3 0 0 X 0 X D2 0 0 X 0 X D1 1 1 X 0 X D0 0 1 X 1 X Comentario Carga A con el número 2 Carga B con el número 3 Suma A con B “Sale” por puerto 1 Stop Electrónica Digital I hoja 4 de 16 DEPARTAMENTO DE ELECTRONICA • El siguiente programa muestra por el puerto 3 un contador que iniciándose en 0 se incremente de 1 en forma sucesiva. El programa debería organizarse mediante el siguiente diagrama de flujos: C A 0 B 1 P3 A A A+B Las instrucciones para este programa serían las siguientes: PC 00 01 02 03 04 05 D7 0 1 1 0 1 D6 0 0 1 1 1 D5 1 1 1 1 0 Arquitectura de Microcontroladores Cap 3 D4 0 0 0 X 0 D3 0 0 0 X 0 D2 0 0 0 X 0 D1 0 0 1 X 1 D0 0 1 1 X 0 Comentario Carga A con el número 0 Carga B con el número 1 “Sale” por puerto 3 Suma A con B Salta a Dirección 02 Electrónica Digital I hoja 5 de 16 DEPARTAMENTO DE ELECTRONICA • Programa que muestra por el puerto 2 un contador que iniciándose en 5 se incremente de 3. Para este caso podríamos basarnos en el programa anterior y sólo habría que realizar muy pocos cambios para lograr el objetivo. Estos cambios corresponden al valor inicial con que se quiere que inicie el contador, el valor de incremento para cada estado distinto del contador y el puerto por el cual se quiere mostrar el resultado del mismo. Ya que la estructura como puede imaginarse es exactamente la misma a la del programa anterior, el programa actual quedará: PC 00 01 02 03 04 05 D7 0 1 1 0 1 D6 0 0 1 1 1 D5 1 1 1 1 0 D4 0 0 0 X 0 D3 0 0 0 X 0 D2 1 0 0 X 0 D1 0 1 1 X 1 D0 1 1 0 X 0 Comentario Carga A con el número 5 Carga B con el número 3 “Sale” por puerto 2 Suma A con B Salta a Dirección 02 Suele ser engorroso recordar los códigos correspondientes a cada una de las instrucciones, al realizar un programa para ser utilizado con los distintos procesadores, para evitar esto, se desarrollaron “programas ensambladores” que tienen la finalidad de traducir ( ensamblar ) un archivo de texto con instrucciones cortas y sencillas de recordar (lenguaje nemotécnico), a los valores determinados de unos y ceros que corresponden al código de cada instrucción (lenguaje de máquina). Arquitectura de Microcontroladores Cap 3 Electrónica Digital I hoja 6 de 16 DEPARTAMENTO DE ELECTRONICA Suele utilizarse una forma organizada para escribir estos programas. Como se dijo estos programas se realizan mediante un archivo de texto y constan de cuatro columnas: Etiquetas: Instrucción Operando ; Comentario • La primera corresponde a las llamadas etiquetas o labels (nombres de fantasía), seguidos del símbolo “ : “ , estas etiquetas le indican al programa ensamblador, informaciones tales como direcciones de memoria, valores de referencia, etc. que serán reemplazados en el momento del ensamblado por el valor correspondiente, y si es necesario, calcular dicho valor, por ejemplo la dirección de memoria a donde se produciría un salto. • La segunda corresponde a las instrucciones que estarán escritas por abreviaturas o nombres cortos ( nemónico) que representan a estas instrucciones, que luego serán traducidas al código de máquina correspondiente. • La tercera a los operandos, Registros, direcciones, valores ,etc. con los cuales las instrucciones realizarán los cálculos, transferencias, reemplazos, etc necesarios para la operación . • La cuarta a los comentarios que pueden o no escribirse, los cuales deben ir precedidos con un “ ; “ . Arquitectura de Microcontroladores Cap 3 Electrónica Digital I hoja 7 de 16 DEPARTAMENTO DE ELECTRONICA Veamos como quedaría escrito el programa anterior con este método de escritura, utilizando el set de instrucciones dado anteriormente. Etiquetas: Instrucción PEPE: Operando ORG 0000 CARGA CARGA OUT SUMA JMP A,#5 B,#3 #2 AB PEPE ; Comentario ; Carga A con el número 5 ; Carga B con el número 3 ; Mostrar por puerto 2 el valor de A ; Suma A con B y lo guarda en A ; Salta a PEPE para repetir la operación END Al programa se le agregaron 2 líneas con respecto a la programación, estas líneas son información que utiliza el Programa Ensamblador como referencia , la primera línea le indica a partir de que dirección de memoria debe cargar el programa ( ORG 0000 ) y la última le indicará la terminación del programa ( END ). Como puede observarse, resulta mucho más fácil escribir un programa utilizando los nemónicos de las instrucciones, que el propio código de máquina debido a que como el nombre lo indica ayudan a la memoria a reconocer la función de la instrucción y no un simple código numérico el cual el más difícil de asociar. Arquitectura de Microcontroladores Cap 3 Electrónica Digital I hoja 8 de 16 DEPARTAMENTO DE ELECTRONICA Supongamos ahora que se quiere realizar un programa para contar la cantidad de alumnos aprobados en un curso. Para realizar este programa será necesario tener información sobre el valor de las notas del curso, en que lugar de memoria se encuentran ubicadas dichas notas y la cantidad total de alumnos o dónde se encuentra ubicada la última nota a considerar. El diagrama de flujos C Inicializar Cantidad de Aprobados Leer Dirección inicial de Notas Leer Nota No Aprobó Si Incrementar Cantidad de aprobados Incrementar Dirección de Notas No Se Consideró todo el curso Si Guardar Cantidad de Aprobados F Arquitectura de Microcontroladores Cap 3 Electrónica Digital I hoja 9 de 16 DEPARTAMENTO DE ELECTRONICA El procesador que se necesitaría para realizar estas operaciones, debería poseer mas instrucciones que el planteado anteriormente, pero si se sigue aumentando la cantidad de instrucciones en base a aumentar el número de bits correspondiente a las mismas, se deberá disminuir la cantidad de bits correspondientes a los datos por lo que el valor del dato máximo que podría manejar este nuevo procesador sería menor o igual a la mitad del número máximo actual que es el 31, debido a que se dispone de 5 bits para los datos. Teniendo en cuenta que el decodificador de instrucciones tiene la propiedad de realizar varios pasos para cada instrucción, debido a que por cada ciclo de máquina hay varios pulsos de clock, se podría pensar en escribir las instrucciones en una dirección de memoria y el dato asociado a ella en la dirección siguiente, con lo que se lograría trabajar con valores desde 0 a 255 pues se dispondrían de los 8 bits para dichos datos; pero esto no ocurriría en todos los casos, pues habría instrucciones que no requerirían de un dato asociado o también podría darse el caso de querer direccionar una memoria externa con una cantidad total de datos mucho mayor a los 256 datos que se pueden direccionar con los 8 bits originales, pero se podría utilizar por ejemplo un número formado por dos datos ubicados en direcciones sucesivas por lo que se llegaría a un valor de 65536 datos distintos; en este caso la instrucción asociada con este dato debería ser tomada por el decodificador de instrucciones y este saber que los datos escritos en las dos direcciones siguientes del programa no corresponderán a instrucciones sino al dato de 16 bits que se quiere manejar. Para realizar esto se propone el siguiente circuito: Arquitectura de Microcontroladores Cap 3 Electrónica Digital I hoja 10 de 16 DEPARTAMENTO DE ELECTRONICA Bus de Instrucciones y de Datos P7 P0 Contador de Programa Q0 A0 Qn An Ck Pst Rst Memoria D0 D7 X Hz REG A Le REG TMP Le Decodificador de Instrucciones A L U -+ N Z P P P 3 2 P0 1 Le Le Le Le BAN CO REG Bus de Control Este diagrama presenta algunos cambios con respecto al diagrama anterior, el registro B se cambió por un registro temporal y se agregó un banco de registros que incluye al registro B y también a un grupo de registros que será utilizado por el procesador para realizar algunas operaciones en forma directa: la ALU puede realizar operaciones de suma, resta, operaciones lógicas, y devolver información referida a si el resultado de la operación es 0 o negativo. También se puede observar que el bus de datos es el mismo que el bus de instrucciones, por lo que puede inferirse que en la memoria estarán escritas las instrucciones y los datos alternadas de manera conveniente para que el decodificador de instrucciones las interprete correctamente. Además se muestra un nuevo Bus denominado Bus de Control y es el encargado de llevar todas las señales de control que manejarán los distintos elementos que constituyen este procesador ya sean los puertos, los registros, la ALU, el contador. etc. También podría eliminarse el registro temporal asociado a la ALU ya que el dato a procesar por la misma podría tomarse desde cualquier registro del banco u un dato propiamente dicho escrito en el programa que está almacenado en la memoria. Y para generalizar aún más el diagrama se podrían unificar los buses de datos e Arquitectura de Microcontroladores Cap 3 Electrónica Digital I hoja 11 de 16 DEPARTAMENTO DE ELECTRONICA instrucciones con el bus de control ya que el decodificador de instrucciones es una unidad que controlaría las operaciones que sean necesarias para procesar una determinada instrucción considerando lo que es instrucción, lo que es dato y lo que son las acciones de control. La arquitectura que tiene este procesador recibe el nombre de Arquitectura von Neumann. Es una arquitectura fundamentalmente secuencial con las siguientes características básicas: • Las operaciones se realizan en forma secuencial. • Unicidad del microprocesador. • Procesamiento de las instrucciones y los datos en forma conjunta. • Todo el programa está almacenado en una memoria. La arquitectura von Neumann caracteriza a las arquitecturas de computadoras que utilizan una única memoria para almacenar las instrucciones y los datos, no ocurre así en los procesadores con “arquitectura Harvard” que poseen memorias separadas. Los ordenadores con arquitectura Von Neumann constan de cinco partes: • La ALU, (unidad aritmético-lógica). • La unidad de control, (decodificador de instrucciones). • La memoria. • Dispositivos de entrada/salida. • BUS de datos (datos instrucciones y control), proporciona un medio de transporte de los datos entre las distintas partes. La ejecución de un programa en un procesador con arquitectura von Neumann, está basada en los siguientes pasos realizados en forma secuencial: Arquitectura de Microcontroladores Cap 3 Electrónica Digital I hoja 12 de 16 DEPARTAMENTO DE ELECTRONICA 1. Obtener la próxima instrucción desde la memoria, en la dirección apuntada por el contador de programa y guardarla en el registro de instrucción. 2. Incrementar el contador de programa en la “longitud” de la instrucción para apuntar a la siguiente, recordar que hay instrucciones que poseen datos asociados escritos en las direcciones de memoria sucesivas y otras que no. 3. Descodificar la instrucción mediante la unidad de control. Ésta tiene el propósito de organizar las operaciones con el resto de componentes del procesador para realizar una acción específica. 4. Al ejecutar una instrucción, ésta si es necesario, puede cambiar el valor del contador del programa, permitiendo así operaciones repetitivas. El contador puede cambiar también cuando se cumpla una cierta condición aritmética, haciendo que el ordenador pueda 'tomar decisiones', que pueden alcanzar cualquier grado de complejidad, mediante la aritmética y lógica anteriores. 5. Vuelve al paso 1. La mayoría de los procesadores están basados en esta arquitectura, aunque pueden incluir otros dispositivos adicionales, (por ejemplo, para gestionar las interrupciones de dispositivos externos como ratón, teclado, etc), una interrupción es una acción que realiza el procesador dependiendo, no de una instrucción u operación lógica, sino de una detención del programa para atender a una operación por hardware o de un reloj externo, etc. Al recibir una petición de interrupción, las acciones que se realizan, pueden sintetizarse en los siguientes pasos: 1. Terminar de ejecutar la instrucción en curso. 2. Guardar en una memoria tipo pila la dirección de memoria siguiente a la instrucción en curso, para ser utilizada al retornar de la interrupción. 3. Saltar a la dirección de memoria asignada por el fabricante del procesador para la interrupción. Arquitectura de Microcontroladores Cap 3 Electrónica Digital I hoja 13 de 16 DEPARTAMENTO DE ELECTRONICA 4. Ejecutar las instrucciones que el programador destinó para esta interrupción a partir de la dirección de memoria asignada o realizar un salto a otra zona de memoria libre donde se encontrarán escritas estas instrucciones. 5. Al terminar de ejecutar las instrucciones correspondientes a la interrupción, se debe sacar de la memoria pila la dirección de la próxima instrucción para cargarla en el contador de programa, dicha instrucción es la que correspondía ejecutar al momento de producirse la interrupción, por lo que se proseguirá con la ejecución normal del programa. Tradicionalmente los microprocesadores se basan como se dijo, en la estructura de Von Neumann, que se caracteriza por disponer de una única memoria principal en la que se almacenan los datos y las instrucciones. A esta memoria se accede a través de un sistema de buses único: • Bus de datos • Bus de direcciones • Bus de control En cambio el modelo basado en la arquitectura Harvard, dispone de dos memorias: • • Memoria de datos Memoria de Programa Además cada memoria dispone de su respectivo bus, lo que permite, que la CPU pueda acceder de forma independiente y simultánea a la memoria de datos y a la de instrucciones. Como los buses son independientes éstos pueden tener distintos contenidos en la misma dirección . Arquitectura de Microcontroladores Cap 3 Electrónica Digital I hoja 14 de 16 DEPARTAMENTO DE ELECTRONICA El término Arquitectura Harvard originalmente se refería a las arquitecturas de computadoras que utilizaban dispositivos de almacenamiento físicamente separados para las instrucciones y para los datos (en oposición a la Arquitectura von Neumann). El término proviene de la computadora Harvard Mark I, que almacenaba las instrucciones en cintas perforadas y los datos en interruptores. Todas las computadoras constan principalmente de dos partes, la CPU que procesa los datos, y la memoria que guarda los datos. Cuando hablamos de memoria manejamos dos parámetros, los datos en sí, y el lugar donde se encuentran almacenados (o dirección). Los dos son importantes para la CPU, pues muchas instrucciones frecuentes se traducen a algo así como "toma los datos de ésta dirección y añádelos a los datos de ésta otra dirección" , sin saber en realidad qué es lo que contienen los datos. En los últimos años la velocidad de las CPUs ha aumentado mucho en comparación a la de las memorias con las que trabaja, así que se debe poner mucha atención en reducir el número de veces que se accede a ella para mantener el rendimiento. Si, por ejemplo, cada instrucción ejecutada en la CPU requiere un acceso a la memoria, no se gana nada incrementando la velocidad de la CPU - este problema es conocido como 'limitación de memoria'. Se puede fabricar memoria mucho más rápida, pero a costa de un precio muy alto. La solución, por tanto, es proporcionar una pequeña cantidad de memoria muy rápida conocida con el nombre de caché. Mientras los datos que necesita el procesador estén en la caché, el rendimiento será mucho mayor que si la caché tiene que obtener primero los datos de la memoria principal. La optimización de la caché es un tema muy importante de cara al diseño de computadoras. La arquitectura Harvard ofrece una solución particular a este problema. Las instrucciones y los datos se almacenan en cachés separadas para mejorar el rendimiento. Por otro lado, tiene el inconveniente de tener que dividir la cantidad de caché entre los dos, por lo que funciona mejor sólo cuando la frecuencia de lectura Arquitectura de Microcontroladores Cap 3 Electrónica Digital I hoja 15 de 16 DEPARTAMENTO DE ELECTRONICA de instrucciones y de datos es aproximadamente la misma. Esta arquitectura suele utilizarse en DSP, o Procesador de Señales Digitales, usados habitualmente en productos para procesamiento de audio y video como así también en distintos electrodomésticos. Arquitectura de Microcontroladores Cap 3 Electrónica Digital I hoja 16 de 16