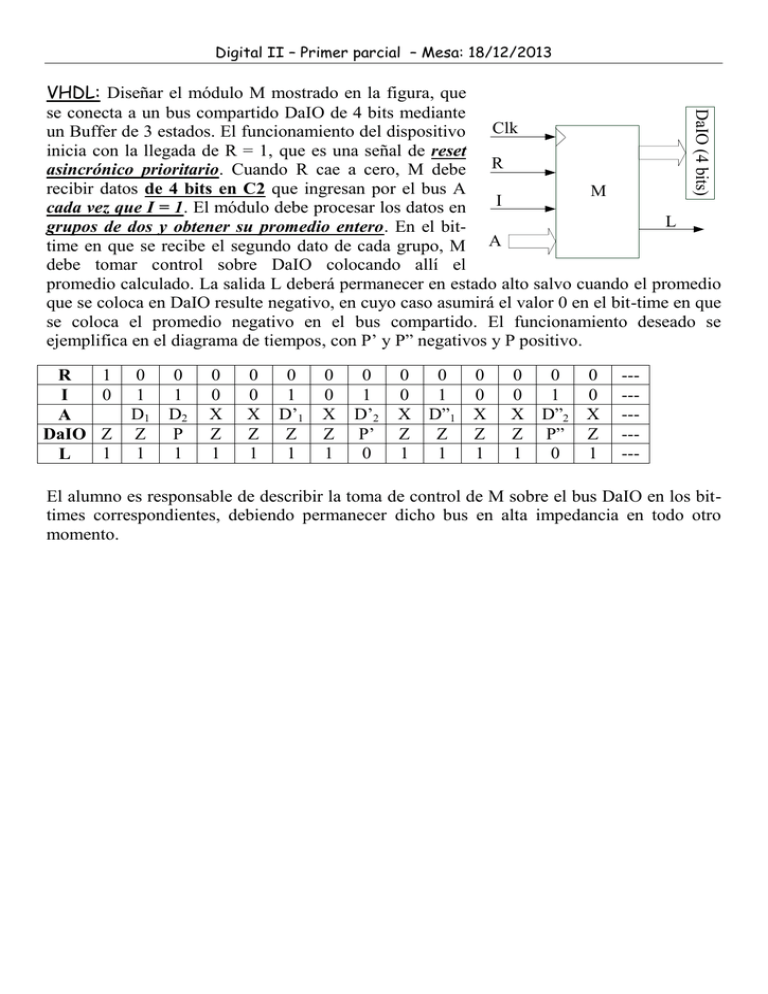

VHDL: Diseñar el módulo M mostrado en la figura, que

Anuncio

Digital II – Primer parcial – Mesa: 18/12/2013 DaIO (4 bits) VHDL: Diseñar el módulo M mostrado en la figura, que se conecta a un bus compartido DaIO de 4 bits mediante un Buffer de 3 estados. El funcionamiento del dispositivo Clk inicia con la llegada de R = 1, que es una señal de reset asincrónico prioritario. Cuando R cae a cero, M debe R recibir datos de 4 bits en C2 que ingresan por el bus A M I cada vez que I = 1. El módulo debe procesar los datos en L grupos de dos y obtener su promedio entero. En el bittime en que se recibe el segundo dato de cada grupo, M A debe tomar control sobre DaIO colocando allí el promedio calculado. La salida L deberá permanecer en estado alto salvo cuando el promedio que se coloca en DaIO resulte negativo, en cuyo caso asumirá el valor 0 en el bit-time en que se coloca el promedio negativo en el bus compartido. El funcionamiento deseado se ejemplifica en el diagrama de tiempos, con P’ y P” negativos y P positivo. R I A DaIO L 1 0 Z 1 0 1 D1 Z 1 0 1 D2 P 1 0 0 X Z 1 0 0 X Z 1 0 1 D’1 Z 1 0 0 X Z 1 0 1 D’2 P’ 0 0 0 0 0 1 0 X D”1 X Z Z Z 1 1 1 0 0 0 0 1 0 X D”2 X Z P” Z 1 0 1 ----------- El alumno es responsable de describir la toma de control de M sobre el bus DaIO en los bittimes correspondientes, debiendo permanecer dicho bus en alta impedancia en todo otro momento.