UNIDAD IV Circuitos Secuenciales

Anuncio

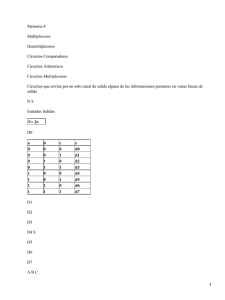

UNIDAD IV Circuitos Secuenciales OBJETIVOS PARTICULARES DE LA UNIDAD Al término de la unidad el alumno: - Interpretará conceptualmente los principios de memoria diferenciándola de la evocación para comprender sus funciones de almacenamiento y retención, así como la representación de datos, su agrupamiento y dimensiones, los cuales requieren que se describan en términos de lógica secuencial. CIRCUITOS SECUENCIALES Los circuitos secuénciales, de la misma forma que los combinacionales, están constituidos por puertas lógicas, y como en estos últimos, la escala de integración de la mayoría de los circuitos disponibles por los fabricantes en es la MSI El concepto de circuito secuencial es una expresión que se aplica a aquellos circuitos lógicos en los que sus valores en el estado presente dependen del estado anterior y a su vez condicionan los del estado siguiente. Lo que se ilustra en la figura 4.1 ANTERIOR PRESENTE SIGUIENTE Figura 4.1 Estados para un circuito secuencial Expresado de otra forma: Los circuitos secuenciales son aquellos en que los valores de las salidas depende del valor de las entradas y del estado anterior. Es importante señalar que los valores que podemos observar y medir siempre serán únicamente los del estado presente. Según su funcionamiento existen dos tipos de circuitos secuencial; Asíncronos, los que no dependen de una señal o reloj de sincronía y los Sincronos, los que si dependen de una señal o reloj de sincronía. 4.1.2 Flip-flops, contadores y registros. Como ya se dijo el circuito fundamental en que se basa la construcción de circuitos secuenciales es el Flip-flop o circuito basculante. Existen tres circuitos clasificados según la forma en que retienen o memorizan el estado que adoptan sus salidas, estos son... *Circuitos Monoestables: Estos circuitos cambian de estado sólo si se mantiene la señal de entrada (nivel alto o bajo), cuando ésta se quita, la salida regresa a su estado anterior, es decir poseen un sólo estado estable y otro metaestables. *Circuitos Astables o Aestables: Son circuitos gobernados por una red de tiempo R-C (Resistencia-Capacitor) y un circuito de realimentación, a diferencia de los anteriores se puede decir que no poseen un estado estable sino dos metaestables *Circuitos Biestables o Flip-Flop (FF): Son aquellos que cambian de estado cada vez que reciben una señal de entrada (ya sea nivel bajo o alto), es decir retienen el dato de salida aunque desaparezca el de entrada, poseen dos estados estables. Flip-flop asincronos Son aquellos circuitos que carecen de impulso de reloj y, por lo tanto, la salida basculara en la medida en que cambien las entradas. En la unidad 3 ya se han tratado desde el punto de vista de construcción de los circuitos a los flip-flops,, en este apartado se hará desde la perspectiva de la aplicación, en el diseño de circuitos secuenciales. Flip –flop RS Dispositivo de almacenamiento temporal de dos estados (alto y bajo), cuyas entradas principales, R y S, a las que debe el nombre, permiten al ser activadas: R: La puesta a cero (reset en inglés), pone a 0 ó a nivel bajo la salida. S: El poner a uno (set en inglés), pone a 1 ó a nivel alto la salida. Si no se activa ninguna de las entradas, el biestable permanece en el estado que poseía tras la última operación de borrado o grabado. En ningún caso deberían activarse ambas entradas a la vez, pues no se podría determinar el estado en el que quedaría la salida. Su tabla de verdad es la siguiente (Q representa el estado actual de la salida y q el estado anterior a la última activación): Tabla de verdad biestable RS S Q Q’ 0 0 X X. 0 1 0 1 1 0 1 0 1 1 X. X R X.= Estado no determinado Tabla 4.1 Tabla de excitación del FF RS Flip – flop D Dispositivo de almacenamiento temporal de dos estados (alto y bajo), cuya salida adquiere el valor de la entrada D cuando se activa la entrada de sincronismo de relog. La ecuación característica del biestable D que describe su comportamiento es: Q siguiente= D y su tabla de verdad: D Q Qsiguiente 0 X 0 1 X 1 X=no importa Tabla 4.2 Tabla de excitación flip-flop D De la tabla de excitación se puede observar que el estado siguiente es un reflejo del valor de la entrada D, por lo que también se le denomina comúnmente como Flip-flop espejo. Biestable JK Es un dispositivo de almacenamiento temporal de dos estados (alto y bajo), cuyas entradas principales, J y K, a las que debe el nombre, permiten al ser activadas: J: Puesta a uno (set en inglés), pone a 1 ó nivel alto de la salida. K: limpiado o puesta a cero (reset en inglés), pone a 0 ó nivel bajo de la salida. Si no se activa ninguna de las entradas, el biestable permanece en el estado que poseía tras la última operación de borrado o grabado. A diferencia del biestable RS, en el caso de activarse ambas entradas a la vez, la salida adquirirá el estado contrario al que tenía. La ecuación característica del biestable JK que describe su comportamiento es: Q siguiente = JQ’+K’Q Y su tabla de verdad es: J K Q(t+1) 0 0 Q(t) Sin cambio 0 1 0 Restablecer 1 0 1 Estableser 1 1 Q’( ) t Complementar Tabla 4.3 Tabla de excitación del FF tipo JK Flip/flop JK activo por flanco Junto con las entradas J y K existe una entrada C de sincronismo o de reloj cuya misión es la de permitir el cambio de estado del biestable cuando se produce en el un flanco de subida o de bajada, según sea su diseño. Su denominación es JK Flip-Flop disparado por flanco. Flip-Flop tipo T Símbolo normalizado: Biestable T activo por flanco de subida. Dispositivo de almacenamiento temporal de dos estados (alto y bajo). El FF T cambia de estado (“toggle” en inglés) cada vez que la entrada de sincronismo o de reloj se dispara. Si la entrada T está a nivel bajo, la báscula retiene el nivel previo. Puede obtenerse al unir las entradas de control de un biestable JK, unión que se corresponde a la entrada T. La ecuación característica del biestable T que describe su omportamiento es: Q siguiente= T o bien Q y la tabla de verdad: T Q Qsiguiente 0 0 0 0 1 1 1 0 1 1 1 0 Tabla 4.3 Tabla de excitación del FF tipo T Unos de los circuitos secuenciales mas comúnmente empleados por sus múltiples aplicaciones son los circuitos contadores y los circuitos de registros CONTADORES Un contador es un circuito secuencial de aplicación general, cuyas salidas representan en un determinado código el número de pulsos que se presentan a la entrada. Están constituidos por una serie de flip-flops conectados entre si de modo que las salidas de estos cambian de estado cuando se aplican impulso. a la entrada. (para un estudio detallado de estos circuitos se recomienda el libro de R Tocci Sistemas Digitales, principios y aplicaciones, Prentice Hall 8ª Edicion 2004) La capacidad de un contador es el número mas elevado, expresado en cualquiera de los códigos binarios, que puede ser representado en sus salidas es decir pueden ser Binarios, decimal o modulo M En los contadores binarios el número de estados es múltiplo de dos, decimales el número de estados es múltiplo de 10, y módulo M se refiere a un número m de estados, en otras palabras a la base M en que se desea que cuente. Cuando el contador llega al valor máximo de su capacidad, comienza a contar de nuevo desde cero al aplicarle el siguiente impulso. Dependiendo del modo de operación, los contadores pueden ser ascendetes si su cuenta se incrementa con cada impulso, descendentes, si su cuenta disminuye. Por otro lado, los contadores se dividen en sincronos y asíncronos. Los primeros, son aquellos en los que los pulsos de reloj se aplican simultáneamente a todos los biestables, y por tanto, todas las salidas cambian la mismo tiempo. En los asíncronos, la señal de reloj se aplica a la entrada del primer biestable, la salida de éste a la entrada de reloj del siguiente, y así sucesivamente el tiempo de propagación de estos dispositivos, es superior al de los síncronos (la señal tiene que pasar por todos los bits menos significativos hasta llegar a un determinado bit). Además en todos los casos anteriores, la cuenta no tiene por qué empezar a terminar en 0, el diseño de contadores síncronos se hace de igual forma que para cualquier circuito secuencial. REGISTROS Son dispositivos para el almacenamiento de información binaria. Existen diversos tipos de registros, dependiendo de la función que desarrollen Registros de almacenamiento simple. Su funcion es basicamente la de almacenar una información. Registros de conversión serie-paralelo. Son registros que realizan la conversión de datos que accede a ellos en serie, a un formato en paralelo Registros conversion paralelo-serie. Son registros que realizan la función inversa a los anteriores, es decir, los datos que accede a ellos en paralelo, le dan formato serie Registros de desplazamiento. Son registros que permiten desplazamiento de la información que almacenan También suelen servir para las funciones anteriores En la unidad III anterior se hicieron ejemplos con contadores comerciales, en muchas ocasiones se requiere de un circuito que cuente en una secuencia en forma particular o que se requiera diseñar el circuito empleando compuertas de FF y no precisamente circuitos contadores comerciales. Para efectuar el diseño se requiere del concepto de diagrama de estados, tema que se trata en el siguiente apartado. 4.2 Procesos y máquinas secuenciales. MÁQUINAS DE ESTADO DE MEALY Y MOORE Los circuitos secuenciales se clasifican dentro de una categoría conocida como máquinas de estado, de la cual se distinguen comúnmente dos tipos: Máquina de Mealy: En esta máquina de estados las salidas se encuentran determinadas por el estado interno del sistema y por las entradas no sincronizadas con el circuito. El diagrama de bloques representativo de esta máquina se muestra en la el circuito. El diagrama de bloques representativo de esta máquina se muestra en la figura donde se observa que las salidas del sistema son tanto sincrónicas como asincrónicas. figura 4.3 Maquina de estados de Mealy Máquina de Moore: Las salidas solo dependen del estado interno y de cualquier entrada sincronizada con el circuito, las salidas del sistema son únicamente sincrónicas. Un ejemplo de este tipo de máquinas de estado son los contadores. figura 4.4 Maquina de estados de Moore MAQUINA DE ESTADOS DE MOORE Se distinguen dos tipos circuitos secuenciales sincronos y asíncronos Los síncronos, requieren una señal de control procedente de un generador externo al propio circuito, que funciona, de modo que si no se aplica dicha señal no se hacen efectivos los valores presentes en las entradas. Este método se emplea cuando el sistema electrónico es complejo y los tiempos de conmutación de los diversos dispositivos que lo constituyen son distintos . La señal de control, también denominada reloj (Clock, o Clock Pulse), se aplica a las entradas del mismo nombre de cada bloque integrado para sincronizar la transmisión de datos o información a través del sistema. La frecuencia de la señal eléctrica debe adaptarse a la velocidad de conmutación del dispositivo más lento del circuito. En cambio, los sistemas secuenciales asíncronos no poseen entrada de reloj, y los cambios en las variables de estado interno y los valores de salida se producen al variar los valores de las entradas del circuito. DIAGRAMAS DE ESTADO Un diagrama de estados es una representación gráfica que indica la secuencia de los estados que se presentan en un circuito secuencial, teniendo en cuenta las entradas y salidas. El diagrama se forma con círculos y líneas. Los circulos representan los estados del circuito secuencial y cada uno de ellos contiene un número que identifica su estado. Las líneas indican las transiciones entre estados y se marcan con dos números separados por un (/), estos dos números corresponden a la entrada y salida presentes antes de la transición. figura 4.5 diagrama de estados TABLAS DE ESTADO Una tabla de estado es un listado que contiene la secuencia de los estados de entradas, estados internos y salidas del sistema, considerando todas las posibles combinaciones de estados actuales y entradas. Las tablas de estado por lo general se dividen en cinco partes: estado presente, entradas, estado siguiente, salidas y excitacion. Estado presente Entrada Estado siguiente Salidas Excitación A B X A B Y DA 0 0 0 0 0 0 0 0 0 0 1 0 1 0 0 1 0 1 0 0 0 0 0 0 0 1 1 1 1 1 1 1 DB 1 0 0 0 0 0 0 0 1 0 1 1 0 1 1 0 1 1 0 0 0 0 0 0 1 1 1 1 0 1 1 0 Figura 4.6 Tabla de estado La variables del estado presente mas las de entrada definen el número de combinaciones posibles, esto es: La tabla de estado para un circuito secuencial con m flip-flops y n entradas tiene 2m+n filas. El estado siguiente tiene m columnas, y el número de columnas depende del número de salidas. Las ecuaciones del circuito se establecen con los valores de las columnas de salidas y excitación que dependen del flip flop a emplear. 4.3 Diseño de circuitos sincronos de lógica secuencial. 1. DISEÑO DE CIRCUITOS Para la realización de un circuito secuencial es conveniente seguir los cuatro pasos siguientes: 1. Definición del problema. 2. Establecer el diagrama de estados que de solución al problema. 3. Construir Tabla de Verdad de diagrama propuesto y realizar la reducción de ecuaciones. 4. Dibujar el diagrama esquemático del circuito lógico 1.Definición del problema. En este punto conviene definir y entender perfectamente el problema propuesto, para ello , como resultado final de este punto tendremos definidos Si existen valor inicial y valor final Es decir si el circuito deberá iniciar en algún valor determinado o si también tendrá un valor en que termine la secuencia Numero de entradas de control Se refiere a que si el sistema tendrá señales de entrada que dependiendo de su valor modifiquen la secuencia que el circuito deberá ejecutar, es importante tener en cuenta que Una sola entrada tiene dos valores diferente es decir para la entrada unica E1 se tendra E1=0 y E1= 1. Para dos entradas E1 y E2 se tendrán 4 valores; 00, 01, 10, y 11 Numero de Estados requerido Se refiere a cuantos estados resuelven el problema propuesto Numero de FF a emplear Determinar el Numero de FF necesario para generar los estados, se determina con la relacion 2No de FF ≥ No de Estados. Por ejemplo para cuatro estados, sera el No de FF = 2, pues 2 2 ≥4. Para 9 estados se requieren 4 FF, pues 24≥9. Numero de bits salidas Es definir el numero bits que permitirán tener la salida requerida. Por ejemplo para una secuencia que tenga como numero mayor 111101 se requieren 6 bits de salida. Determinar si será una maquina de estados tipo More o Mealy Finalmente conviene definir con que tipo de maquina de estados se propondrá la solución. Comentario: es posible emplear los dos tipos de maquina para resolver un mismo problema, el decidir cual conviene, depende del contexto general de donde se desprende el problema a resolver. Ilustrarlo queda fuera del propósito de este polilibro. 2. Establecer el diagrama de estados que de solución al problema. Dependiendo del tipo de maquina a emplear se propone una solución en diagrama de estados, se deberá verificar a detalle y cubriendo todas las posibilidades posibles que verdaderamente sea una solución al problema a resolver. Tener en cuenta que si se tienen por decir 2 entradas de control cada estado deberá tener cuatro posibles salida hacia el mismo u otro estado. También existen técnicas para reducir estados redundantes o repetidos, se recomienda ver el libro de R. TOCCI o el de T. Floyd señalados en la bibliografía. 3.- Construir Tabla de Verdad de diagrama propuesto y realizar la reducción de ecuaciones. A partir del diagrama de estados se obtiene la información para determinar la tabla de verdad, llenando los campos que se proponen. En la figura se muestra una tabla de estados para 2 FF y una entrada E 1 con un solo bit de salida Y y empleando FF tipo D Estado presente Entrada Estado siguiente Salidas Excitación A B E1 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 A B Y DA DB Debemos notar que las columnas de estado presente y entrada definen el tamaño de la tabla, para este ejemplo es 23 por tener 2 estados + 1 bit de salida. Las ecuaciones que se buscan las definen las columnas de salidas Y y excitación DA y DB 4.- Dibujar el diagrama esquemático del circuito lógico Se recomienda que en el dibujo esquemático, además de dibujar las compuertas con su símbolo, se indiquen los números correspondientes de la compuerta a utilizar. El procedimiento de diseño se ilustra con los siguientes ejemplos: Ejemplo 43 Diseñar un circuito contador que siga la secuencia … 0, 2, 4, 8,… que no tenga valor inicial ni valor final. SOLUCION: Para este problema en particular en que se requiere generar la secuencia 0,2,4,8 en binario, tendremos: Si existen valor inicial y valor final R.- no existen Numero de entradas de control R.- no existen Numero de Estados requerido R.- se necesitan 4 estados, para generar cada uno de los valores de 0, 2, 4y8 Numero de FF a emplear R.- se usaran 2 FF para generar los 4 estados necesarios. Numero de bits salidas R.- Se definen X, Y, Z, y W como bits de salida Para poder tener el mayor numero 810 = (1 0 0 0)2 Determinar si será una maquina de estados tipo More o Mealy R.- Para este ejemplo se propone usar una maquina tipo More, puesto que la salida esta directamente relacionada con el estado. 2.- Diagrama de estados (maquina de Moore) 3.- Construir Tabla de Verdad de diagrama propuesto y realizar la reducción de ecuaciones. Para este ejemplo la tabla de estados no contiene la columna de entradas por lo tanto el tamaño de la tabla sera de 22 Estado presente Estado siguiente Salidas Excitación A B A B X Y Z W DA DB 0 0 0 1 0 0 0 0 0 1 0 1 1 0 0 0 1 0 1 0 1 0 1 1 0 1 0 0 1 1 1 1 0 0 1 0 0 0 0 0 Figura del ejemplo 43. Tabla de verdad Del diagrama se observa que del estado 00 se va al 01 y que su salida es 0000, del estado 01 se va al 10 con salida 0010, del 10 al 11 con 0100 de salida y finalmente del 11 se va al 00 con salida 1000. lo que se refleja en la tabla. Finalmente en la columna de excitación se contempla el uso de FF tipo D por lo que para DA y DB se pondrán los valores de A y B de la columna del estado siguiente, pues recordemos que a los FF tipo D se les conoce también como de espejo. Las ecuaciones que se buscan son X = AB Z = A’B Y = AB’ W=0 DA = A’B + AB’ DB = A’B’ + AB Ejemplo 43b; Diseñar circuito en donde si la entrada es 1 se muestre la secuencia: …8,4,2,1… y si la entrada es = 0 se muestre la secuencia … 1,2,4,8… SOLUCION 1. Definición del problema. Si E= 1 entonces mostrar …8,4,2,1… E= 0 entonces mostrar …1,2,4,8,… No existe valor inicial ni valor final. Numero de entradas = 1 = E Numero de salidas = 4 = X, Y, Z, W Numero de estados = 4 por tanto el No de FF = 2 = A, B 2. diagrama de estados (maquina de Mealy) Estado presente Entrada Estado siguiente Salidas Excitación A B E A B X Y Z W DA 0 0 0 0 1 0 0 0 1 0 1 0 0 1 1 1 0 1 0 0 1 1 0 1 0 1 0 0 0 1 0 1 0 0 1 1 0 0 1 0 0 0 0 0 1 0 0 1 1 0 1 0 0 1 1 1 0 1 0 1 0 0 0 1 0 1 1 1 0 0 0 1 0 0 0 0 0 1 1 1 1 0 0 0 1 0 1 0 Figura 4.8 Tabla de verdad X = ∑(3,6) Y = ∑(2,4) Z = ∑(2,7) W = ∑(0,5 DA = ∑(1,2,4,7) DB = B’ DB Figura 4.7Diagrama esquemático X +5 3 6 74138 A B E 0 1 23 4 56 -7’ Y 2 4 3 6 Z 2 7 3 6 W 0 5 3 6 1 2 4 7 DA 74174 DB A A’ B 74174 B’ CP CP Ejemplo 43 C Diseñar un circuito secuencial con una entrada W sincronizada a la señal de reloj, que acepte la secuencia 0011 y que cada vez que la detecte, su salida se Q ponga en ALTO y regrese a condiciones iniciales para detectar de nuevo la secuencia. 1. Definición del problema. A como se van presentando los valores de 0 o 1 en la entrada W, se “generara” una secuencia, digamos 00001100101110011011000100, en donde se desea detectar cuando ocurra 0011 poniendo en ALTO la salida Q y reestableciendo las condiciones iniciales a fin de detectar nuevamente la ocurrencia de otra secuencia. 2.- Diagrama de estados este ejercicio se puede resolver ya sea con la a).maquina de Mealy o con b).-Maquina de Moore a).- maquina de Mealy Figura 1 para ejemplo 43 C: Detector de secuencia 0011 (maquina de Mealy) Estado presente Entrada Estado siguiente Salidas Excitación A B W A B Q DA DB 0 0 0 0 1 0 0 1 0 0 1 0 0 0 0 0 0 1 0 1 0 0 1 0 to y realizar la reducción de ecuaciones 3.Construi r Tabla de Verdad de diagram a propues 0 1 1 0 0 0 0 0 1 0 0 1 0 0 1 0 1 0 1 1 1 0 1 1 1 1 0 0 1 0 0 1 1 1 1 0 0 1 0 0 Las ecuaciones son; Q = ABW ∑(7) DA = A’BW’ + AB’W’ + AB’W = ∑(2,4,5) DB = A’B’W’ + AB’W + ABW’= ∑(0,5,6) b).- maquina de Moore En el modelo de Moore fig 2. la salida está en el mismo estado por eso se genera un estado más que en la maquina de Mealy, además de que después de detectar la secuencia correcta 0011 en E4, la entrada siguiente es considerada como el primer dato figura 2 del ejemplo 43 C. Detector de la secuencia 0011 (maquina de Moore) Estado presente Entrada Estado siguiente Salidas Excitación A B C W A B C Q DA DB DC 0 0 0 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 1 0 0 1 0 1 0 1 1 0 0 1 1 0 1 1 0 0 1 0 0 0 1 0 0 1 1 1 1 0 0 0 1 0 0 1 0 0 0 0 0 1 1 0 0 1 1 0 0 1 0 0 0 1 0 0 0 1 0 1 0 0 0 0 0 0 0 0 1 0 1 1 0 0 0 0 0 0 0 1 1 0 0 0 0 0 0 0 0 0 1 1 0 1 0 0 0 0 0 0 0 1 1 1 0 0 0 0 0 0 0 0 1 1 1 1 0 0 0 0 0 0 0 Las ecuaciones son Q= ∑(8,9) DA = ∑(7) DB = ∑(2,4,5,6) DC = ∑(0,5,8)