TP2_TC2016.pdf

Anuncio

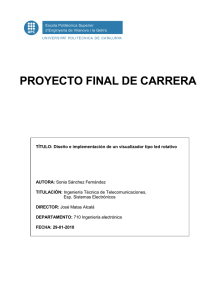

Síntesis de Sistemas Digitales en FPGA 2016 Trabajo Práctico nº 2 Objetivos: Describir circuitos secuenciales sincrónicos utilizando sentencias de estilo algorítmico. Definir archivos de asignación de pines considerando los recursos disponibles en la placa Spartan 3e. Implementar circuitos en la placa de desarrollo. Tareas a realizar: 1. Describir en VHDL el sistema, cuya interfaz se presenta en la figura, que se implementará en la placa Spartan 3e. El mismo deberá contar con un reset Clk asincrónico prioritario, de modo que cuando está en alto los leds de la placa permanecen apagados. Una vez que Switch la entrada de reset cae a cero, el sistema deberá cargar, (4) S (5) en un registro de 4 bits, el valor de los switch cada vez Sistema que se pulse P1, y en otro registro de 4 bits el valor de P1 los switch cada vez que se pulsa P2. Además, el sistema deberá presentar en los leds de la placa el resultado de sumar el contenido de ambos registros, previniendo la P2 posibilidad de sobreflujo. Los datos ingresados se deberán interpretar como números enteros en Reset complemento a la base. 1.1. Verificar el funcionamiento del sistema mediante simulación. 1.2. Definir el archivo .ucf correspondiente a los recursos de la placa que se utilizan. 1.3. Implementar el circuito en la placa de desarrollo y ensayarlo. Trabajo Práctico 2 hoja1