Tema 5.- Memorias. 1. Conceptos básicos generales. 2

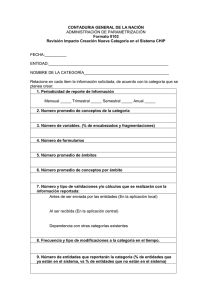

Anuncio

Tema 5 Tema 5.- Memorias. 1. Conceptos básicos generales. 2. Organización de mapas de memorias. 2.1. Objetivos. 2.2. Ejemplo de conexión entre un procesador genérico y la memoria. 2.3. Ejemplo de conexión entre el MC68000 y la memoria. ---***--- Página 1 de 34 Tema 5 1. Conceptos básicos generales. La memoria es la parte de un computador encargada de almacenar la información que éste maneja. En ella se guardan tanto los programas como los datos implicados en la ejecución de los mismos. RAM 2 posiciones de ancho m bits An-1-A0 2n · m bits Address Bus n Dm-1-D0 m Data Bus n 8 9 10 11 … 20 … 23 … 30 … 40 Términos básicos que se manejan cuando se trabaja con memorias. n Nº de posiciones 2 8 = 256 palabras 9 2 = 512 palabras 10 2 = 1024 palabras = 1 Kpalabras 211 = 2 Kpalabras Palabra de memoria. Unidad mínima de acceso. Ancho de la palabra de memoria. Tamaño de la palabra de memoria, coincide con el número de bits del bus de datos del chip de memoria. Celda de memoria. Corresponde a un bit de la memoria. 20 2 = 1024 Kpalabras = 1 Mpalabras Capacidad de una memoria. 23 Cantidad de información que la memoria puede almacenar. Viene determinado por el tamaño del bus de direcciones (AB) y del de datos 30 Capacidad = 2AB · DB bits. Es decir, la memoria 2 = 1024 Mpalabras = 1 Gpalabras (DB) según la fórmula está formada por 2AB posiciones de DB bits cada una de ellas. 2 = 8 Mpalabras 40 2 = 1024 Gpalabras = 1 Tpalabras Página 2 de 34 Tema 5 Tiempo de escritura. Tiempo transcurrido desde que la memoria recibe la orden de escritura hasta que son almacenados en la misma. Tiempo de lectura. Tiempo transcurrido desde la orden de lectura hasta que la memoria vuelca los datos solicitados en su bus de datos. Tiempo de acceso. Media de los dos tiempos de lectura y escritura definidos. Clasificaciones de las memorias siguiendo distintos criterios. Según el acceso a los datos: De acceso aleatorio. Se puede acceder directamente a cualquier dirección de memoria. El tiempo de acceso es el mismo para cualquier dirección de memoria. Ejemplo: la RAM (Random Access Memory). De acceso secuencial. Para acceder a una posición (o dirección) de memoria hay que pasar linealmente por todas las anteriores. El tiempo de acceso depende de la dirección de la palabra de memoria a la que se acceda. Ejemplo: cinta magnética. Página 3 de 34 Tema 5 Según las operaciones permitidas sobre la memoria: De sólo lectura. En estas memorias sólo están permitidas operaciones de lectura. Ejemplo: ROM (Read Only Memory), PROM (Programmable ROM), EPROM (Erasable Programmable ROM), EEPROM (Electrically-erasable Programmable ROM). De lectura y escritura. Pueden ser leídas y escritas. Ejemplo: RAM. Según el tipo de lectura: De lectura destructiva. Al leer el contenido de una posición de memoria, la información almacenada desaparece. Se precisa una regeneración del contenido, después de cada lectura. De lectura no destructiva. La lectura no provoca la pérdida de la información almacenada. Casi totalidad de las memorias centrales modernas pertenecen a este grupo. Página 4 de 34 Tema 5 Según la estabilidad de la información almacenada: Volátiles. La información almacenada en la memoria se pierde al cortar la alimentación. Ejemplo: RAM. No volátiles. Retienen la información aún sin alimentación, el contenido es memorizado sin consumo energético. Ejemplo: ROM. Según la tecnología de las celdas de memoria: Estáticas (SRAM). Esta memoria no necesita ser restaurada, lo que la hace más rápida; pero es también más costosa que la DRAM. Cada celda de memoria se basa en un biestable. Dinámicas (DRAM). Esta memoria necesita ser restaurada millares de veces por segundo para no perder su contenido. Cada celda de memoria se basa en un condensador. Página 5 de 34 Tema 5 Según el soporte físico de almacenamiento: Eléctrico. Memorias de semiconductores estáticas (biestables) y dinámicas (condensadores). Magnético. Disquetes. Óptico. CD y DVD. Mecánico. Tarjetas perforadas. Página 6 de 34 Tema 5 Jerarquía de memorias. Las memorias se pueden clasificar siguiendo una jerarquía de capacidades crecientes y velocidades decrecientes. Registros: Son internos a la CPU, de baja capacidad y acceso rápido. Capacidad: bytes. Caché: Memoria de pequeña capacidad y muy alta velocidad dedicada a que el procesador pueda trabajar a la máxima velocidad sin necesidad de pedir información constantemente a la memoria principal. Su contenido es copia de una parte de la memoria principal. Capacidad: Kilobytes. Memoria principal (o interna): Formada por la asociación de chips de RAM y ROM, según la capacidad de almacenamiento requerida por el sistema. Capacidad: Megabytes o pocos Gigabytes. Memoria secundaria (o periférica): Almacenamiento auxiliar en dispositivos periféricos, de elevada capacidad y baja velocidad de acceso (millones de veces inferior a la de la primaria). No son imprescindibles como la principal. Página 7 de 34 Tema 5 CPU Registros te recie n d ad c Ca pac i Memoria Principal Memoria secundaria (HD, Floppy, CD, Pen Drive...) Página 8 de 34 ent e cr eci t e de y cos idad Ve lo c Caché Tema 5 2. Organización de mapas de memorias. Entendemos por mapa de memoria la organización de las distintas unidades de memoria (chips) en el espacio de direccionamiento de un procesador. 2.1. Objetivos. Objetivos del diseño de un mapa de memoria: a) Adaptación al ancho de palabra del procesador (bus de datos). b) Adaptación el espacio direccionable por el procesador (bus de direcciones). Página 9 de 34 Tema 5 Adaptación al ancho del bus de datos. El ancho de los datos que salen y entran de la memoria ha de coincidir con el tamaño del bus de datos del procesador (K). • Si el ancho del bus de datos de los chips de memoria es superior a K bits, sólo utilizaremos K líneas de dicho bus. • Si el ancho del bus de datos de los chips de memoria es K bits, no tendremos problema, se conectarán directamente las líneas de datos del chip con las del microprocesador. • Si el ancho del bus de datos de los chips de memoria es inferior a K bits, tendremos que utilizar varios chips para conectarlos en paralelo al bus de datos del microprocesador. Ejemplo: el bus de datos del microprocesador de 8 bits y el de los chips de memoria de 4 bits. Será necesario utilizar dos chips de memoria para completar una palabra del microprocesador. 11 A10-A0 11 RAM 2K · 4b D7-D4 4 RAM 2K · 4b 4 D3-D0 Página 10 de 34 11 A10-A0 RAM 2K · 8b D7-D0 8 Tema 5 Adaptación al ancho del bus de direcciones. Proporcionar el espacio direccionable por el microprocesador. Si el ancho del bus de direcciones del procesador es M, el espacio direccionable será 2M posiciones de memoria. Ejemplo: el bus de direcciones del microprocesador es de 12 bits (A11-A0), es decir, un espacio de 212 (= 4K posiciones). Chips de memoria de 2K posiciones. Será necesario utilizar dos chips. A11 11 A10-A0 RAM 2K · 4b 4 D3- D0 12 4 A11 D3- D0 11 D3-D0 RAM 2K · 4b 4 A11-A0 RAM 4K · 4b D3- D0 Página 11 de 34 4 Tema 5 2.2. Ejemplo de conexión entre un procesador genérico y la memoria. Hay que conectar las líneas de dirección, las de datos y las de control. Bus de c ontrol Bus de direcciones 16 CPU A15-A0 D7-D0 8 Bus de datos Página 12 de 34 RAM 64K · 8b 64KB Tema 5 El número de líneas de dirección de cada chip depende de su tamaño: 14 A13-A0 __ __ CS CS Chip 1 ROM 16KB 8 14 A13-A0 A12-A0 __ CS Chip 2 RAM 16KB __ CS Chip 3 RAM 8 KB A12-A0 Chip 4 RAM 8 KB 8 12 A11-A0 D7-D0 D7-D0 __ CS Chip 6 RAM 4 KB 8 12 A11-A0 D7-D0 12 A11-A0 • Chips 1 y 2: 16 K posiciones -> 14 líneas de dirección = A13-A0. • Chips 3 y 4: 8 K posiciones -> 13 líneas de dirección = A12-A0. • Chips 5, 6, 7 y 8: 4 K posiciones -> 12 líneas de dirección = A11-A0. Las líneas más significativas del bus de direcciones que sale del procesador seleccionan el chip al que accedemos. Las líneas menos significativas del bus de direcciones que sale del procesador seleccionan la posición de memoria (dirección física) dentro del chip. __ CS Chip 7 RAM 4 KB 8 D7-D0 __ CS Chip 5 RAM 4 KB 8 D7-D0 8 13 A11-A0 D7-D0 8 13 12 D7-D0 __ CS Chip 8 RAM 4 KB 8 D7-D0 Página 13 de 34 Tema 5 Chip Tipo Tamaño 1 ROM 16 KB 2 RAM 16 KB 3 RAM 8 KB 4 RAM 8 KB 5 RAM 4 KB 6 RAM 4 KB 7 RAM 4 KB 8 RAM 4 KB Líneas de selección 2 A15-14 00 2 A15-14 01 3 A15-13 100 3 A15-13 101 4 A15-12 1100 4 A15-12 1101 4 A15-12 1110 4 A15-12 1111 Página 14 de 34 Líneas de dirección 14: A13-0 0…0 1…1 14: A13-0 0…0 1…1 13: A12-0 0…0 1…1 13: A12-0 0…0 1…1 12: A11-0 0…0 1…1 12: A11-0 0…0 1…1 12: A11-0 0…0 1…1 12: A11-0 0…0 1…1 Rango de posiciones $0000 $3FFF $4000 $7FFF $8000 $9FFF $A000 $BFFF $C000 $CFFF $D000 $DFFF $E000 $EFFF $F000 $FFFF Tema 5 $0000 Mapa de memoria del ejemplo. Chip 1 ROM 16KB Líneas de dirección de la CPU A15 A14 A13 A12 A11-A0 0...0 0 0 1...1 0...0 0 1 1...1 0...0 1 0 0 1...1 0...0 1 0 1 1...1 0...0 1 1 0 0 1...1 0...0 1 1 0 1 1...1 0...0 1 1 1 0 1...1 0...0 1 1 1 1 1...1 Chip al que se accede $3FFF $4000 Chip 1 Chip 2 RAM 16KB Chip 2 Chip 3 $7FFF $8000 Chip 4 Chip 5 Chip 3 RAM 8 KB $9FFF $A000 Chip 6 Chip 7 Chip 8 Chip 4 RAM 8 KB $BFF F $C000 $CFFF $D000 $DFFF $E000 $EFFF $F000 $FFFF Página 15 de 34 Chip 5 RAM 4 KB Chip 6 RAM 4 KB Chip 7 RAM 4 KB Chip 8 RAM 4 KB Tema 5 Si el bus de direcciones de la CPU es de n bits y el chip de memoria es de 2k posiciones (siendo n>k): • Las k líneas menos significativas del bus de direcciones de la CPU seleccionan la dirección dentro del chip. • Las n-k líneas más significativas elegirán el chip de memoria al que se accede. Ejemplos: La CPU accede a la dirección lógica $80FF La CPU accede a la dirección lógica $7FFF Direcció n Lógica: $80F F Líneas de selección Dirección Lógica: $7FFF Línea s de dirección Líneas de se lección 1000 0000 1 11 1 1 11 1 Chip 3 Dirección física $00FF Líneas de direcc ión 0111 1 11 1 1 111 11 11 Chip 2 Dirección física $3FFF Página 16 de 34 Tema 5 A15 0 0 1 1 1 1 1 1 Líneas de dirección A14 A13 A12 A11-A0 0...0 0 1...1 0...0 1 1...1 0...0 0 0 1...1 0...0 0 1 1...1 0...0 1 0 0 1...1 0...0 1 0 1 1...1 0...0 1 1 0 1...1 0...0 1 1 1 1...1 Chip al que se accede Chip 1 ROM 16 K Chip 2 RAM 16 K Chip 3 RAM 8 K Chip 4 RAM 8 K Chip 5 RAM 4 K Chip 6 RAM 4 K Chip 7 RAM 4 K Chip 8 RAM 4 K Según esta tabla obtendríamos las siguientes activaciones de los CS: ___ CS1 = A15 + A14 ___ ___ CS2 = A15 + A14 ___ ___ CS3 = A15 + A14 + ___ ___ CS4 = A15 + A14 + ___ ___ ___ CS5 = A15 + A14 + ___ ___ ___ CS6 = A15 + A14 + ___ ___ ___ CS7 = A15 + A14 + ___ ___ ___ CS8 = A15 + A14 + A13 ___ A13 Sólo uno de los CS estará activo en cada acceso a memoria. A13 + A12 ___ A13 + A12 ___ A13 + A12 ___ ___ A13 + A12 Página 17 de 34 Tema 5 Obtención de los CS mediante decodificadores: 0 A15 A14 1 0 DEC 2:4 1 ___ CS1 ___ CS2 2 3 DEC 1:2 A13 0 1 0 A13 A12 1 0 DEC 2:4 1 2 3 ___ CS3 ___ CS4 A15 A14 3 A13 A12 1 ___ CS5 ___ CS6 ___ CS7 ___ CS8 2 0 DEC 4:16 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 ___ C S1 ___ C S2 ___ CS3 ___ C S4 ___ CS5 ___ CS6 ___ CS7 ___ CS8 NOTA: Estos circuitos de decodificación se basan sólo en las líneas de dirección, es necesario incluir la información de las líneas de control. Página 18 de 34 Tema 5 Decodificación total y decodificación parcial. Es posible que, con los chips de los que disponemos, no se llene el mapa de memoria completo. En estos casos los mapas de memoria pueden hacerse de dos maneras diferentes: • Decodificación total. Cada dirección física (posición de cada chip) es direccionada con una única dirección lógica. Esta decodificación es más exhaustiva y es necesario tener en cuenta un mayor número de líneas de dirección, lo que la hace más precisa, complicando la circuitería de decodificación. • Decodificación parcial. A una dirección física le pueden corresponder diferentes direcciones lógicas. Esta decodificación es más sencilla pero menos precisa. Supongamos, como ejemplo, que queremos completar un espacio de direcciones de 64 K y disponemos de los siguientes chips de memoria: 2 chips de 8 K de RAM 1 chip de 16 K de EPROM. Página 19 de 34 Tema 5 Con la técnica de decodificación total obtendríamos el siguiente mapa de memoria: A15 A14 A13 0 0 Chip 1 16 K EPROM 1 0 1 Chip 2 8 K RAM Chip 3 8 K RAM 1 32 K LIBRES A15 A14 A13 Circuito de decodificación: Página 20 de 34 2 1 0 DEC 4:16 0 1 2 3 4 5 6 7 ___ CSEPROM ___ CS RAM1 ___ CSRAM2 Tema 5 Otra colocación: A15 0 A14 0 define bloques de 32 K define bloques de 16 K 1 X 1 0 0 1 0 1 1 A13 X 16 K EPROM SIN CUBRIR 8 K RAM 8 K RAM Con la decodificación total a cada chip le corresponde un espacio de direcciones cuyo tamaño coincide con la capacidad real del chip. Página 21 de 34 Tema 5 Con decodificación parcial obtendríamos el siguiente mapa de memoria: A15 0 1 A14 0 define bloques de 16 K 1 Chip 2 8 K RAM Chip 3 8 K RAM Chip 1 16 K EPROM define bloques de 32 K Físicamente, cada RAM tiene 8K posiciones aunque en el espacio de direcciones ocupa el doble. Se accederá al chip 2 cuando se acceda a cualquier dirección entre la $0000 y la $3FFF. Se accederá al chip 3 cuando se acceda a cualquier dirección entre la $4000 y la $7FFF. Se accederá al chip 1 cuando se acceda a cualquier dirección entre la $8000 y la $FFFF. Página 22 de 34 Tema 5 A15 Líneas de dirección A14 A13 A12-A0 0 0 X 0 1 X 1 X 0...0 1...1 0...0 1...1 0...0 1...1 Chip al que se accede Chip 2 8 K RAM Chip 3 8 K RAM Chip 1 16 K EPROM Siempre que A15-A14 valgan 00 y 01 se accederá a los chips de RAM 2 y 3 respectivamente, independientemente del valor de las otras líneas de dirección. Para direccionar dentro de los 8 K de RAM necesitamos 13 líneas de dirección (A12-A0). El valor de A13 no interviene ni a la hora de seleccionar el chip ni a la hora de elegir una posición dentro de ese chip. Siempre que A15 valga 1 se accederá a la EPROM, independientemente del valor de las otras líneas de dirección. Para direccionar los 16 K de EPROM necesitamos 14 líneas de dirección (A13-A0). El valor de A14 no interviene ni a la hora de seleccionar el chip ni a la hora de elegir una posición dentro de ese chip. Página 23 de 34 Tema 5 Se simplifica la circuitería de decodificación, en la que el decodificador pasaría a ser 2:4, teniendo como entradas A15 y A14. Tal como se muestra en la siguiente figura: A15 A14 1 0 DEC 2:4 0 ___ CSRAM1 1 ___ CSRAM2 2 ___ CSEPROM 3 Se podría conectar directamente #A15 al CHIP SELECT de la EPROM y usar un decodificador 1:2 con entrada de habilitación activa en bajo a la que se conecta A15. Página 24 de 34 Tema 5 Si se accede a la dirección $C000 (1100 0000 0000 0000) accederemos al chip de EPROM, a la misma posición dentro de este chip que si accediésemos a la dirección $8000 (1000 0000 0000 0000), dado que el valor de A14 no tiene importancia. Vemos que dos direcciones lógicas distintas nos llevan a la misma dirección física en la EPROM. La desventaja de este método es que si se amplía la memoria hay que cambiar el circuito entero, mientras que con la decodificación total, el añadir un nuevo chip de memoria sólo implica conectar el CHIP SELECT de dicho chip a una de las salidas de decodificador. Página 25 de 34 Tema 5 2.3. Ejemplo de conexión entre el MC68000 y la memoria. Organización de la memoria del 68000. Dir física i Dir física i+1 Banco Par Banco Impar Direcciones Pares Direcciones Impares Dir lógica 2i Dir lógica 2i+2 Dir lógica 2i+1 Dir lógica 2i+3 D15 - D8 D7 - D0 #UDS #LDS Página 26 de 34 Tema 5 La activación de uno y/u otro banco dependerá del tamaño y la dirección del dato al que se accede, activándose el banco par (#UDS) cuando accedemos a un BYTE colocado en dirección par o a un WORD, y el impar (#LDS) cuando accedemos a un BYTE colocado en dirección impar o a un WORD. Como ejemplo, supongamos que los bancos implementan un bloque de memoria colocado en la dirección 0. Esta tabla muestra la relación entre las direcciones lógicas y las físicas. Banco Par Dirección del Dirección 68000 dentro del chip 0 0 1 2 2 4 ... ... i 2i ... ... Banco Impar Dirección Dirección del dentro del chip 68000 0 1 2 ... i ... 1 3 5 ... 2i + 1 ... Recordemos que si un dato es de tamaño WORD, el MSByte estará en la dirección lógica más baja (2i) y el LSByte en la más alta (2i+1), ocupando la misma dirección física en ambos bancos. El acceso a un LONG se divide en dos accesos a memoria, uno para cada WORD de los dos que lo componen. Página 27 de 34 Tema 5 Las líneas del MC68000 involucradas en los accesos a memoria son: • Las del bus de direcciones. Indican la dirección a la que queremos acceder. De las 24 líneas que componen el bus de direcciones interno del MC68000, sólo salen al exterior las 23 más significativas (A23 - A1). A0 la utiliza internamente el MC68000 (combinada con el tamaño del dato) para generar las señales #UDS y #LDS. • Las del bus de datos. Por sus líneas viajan los datos que se quieren leer o escribir en la memoria. • Las del bus de control. • #AS. Su activación indica que en el bus de direcciones hay una dirección de memoria válida a la cual el microprocesador quiere acceder. • R / #W. Esta señal se pone a 1 si el acceso es de lectura de memoria y a 0 si es de escritura en memoria. • #UDS (Upper Data Strobe). Asociada al tráfico por la mitad alta del bus de datos. Se activa si se accede a un BYTE cuya dirección es par o un WORD. • #LDS (Lower Data Strobe). Asociada al tráfico por la mitad baja del bus de datos. Se activa si se accede a un BYTE cuya dirección es impar o un WORD. • #DTACK. Señal de sincronización de la memoria con el MC68000 mediante la cual la memoria indica al MC68000 que la transferencia solicitada ha sido realizada. Página 28 de 34 Tema 5 Terminado este repaso, procedemos a exponer un ejemplo: Implementar un espacio de memoria para el 68000 con las siguientes características: • Las 320 K primeras posiciones de memoria serán ocupadas por 320 KB de EPROM. • Las últimas 128 K posiciones de memoria serán ocupadas con 128 KB de RAM. Disponemos los siguientes tipos de chips, en las cantidades necesarias: • EPROM: 320 Kx8, 256 Kx8, 128 Kx8, 64 Kx8, 32 Kx8 y 16Kx8. • RAM: 128Kx8, 32Kx8. Todos los chips tienen señal de Chip Select (#CS) activa en bajo. Los chips de RAM tienen, además, una señal R/W* que cuando vale 1 indica lectura y cuando vale 0 escritura. Proceso: 1. Número de chips de cada tipo elegido. 2. Distribución de los chips en el mapa de memoria del 68000. 3. Ecuaciones de los Chip Select. Página 29 de 34 Tema 5 1. Número de chips de cada tipo elegido. Se trata de tomar el menor número de chips posibles. Para la EPROM habría que completar dos bancos (el par y el impar) de 160 KB cada uno. Para ello elegimos 1 chip de 128 KB y otro de 32 KB para cada banco. Por lo tanto, para implementar la EPROM necesitamos 2 chips de 128 KB y otros 2 de 32 KB. Para la RAM habría que completar dos bancos de 64 KB cada uno. Para ello elegimos 2 chips de 32 KB para cada banco. Por lo tanto, para implementar la RAM necesitamos 4 chips de 32 KB. Página 30 de 34 Tema 5 2. Distribución de los chips en el mapa de memoria del 68000. Se trata de determinar cómo se organizan los chips elegidos para cubrir el espacio de memoria solicitado en el enunciado del problema. La distribución final se obtiene de la siguiente tabla: Chips Tipo Tamaño 1y2 EPROM 128 KB 3y4 EPROM 32 KB 7y8 RAM 32 KB 5y6 RAM 32 KB Líneas de selección 6 A23-18 0000 00 8 A23-16 0000 0100 Líneas de dirección 17: A17-1 0…0 1…1 15: A15-1 0…0 1…1 Rango de posiciones 8 A23-16 1111 1111 8 A23-16 1111 1110 15: A15-1 0…0 1…1 15: A15-1 0…0 1…1 $FF0000 $FFFFFF Esta tabla nos lleva a los siguientes mapas de memoria. Página 31 de 34 $000000 $03FFFF $040000 $04FFFF $FE000 $FEFFFF Tema 5 EPROM Banco Par Banco Impar Chip 1 Chip 2 EPROM EPROM 128 KB 128 KB $ 000000 ← $ 03FFFF $ 040000 Chip 3 Chip 4 EPROM EPROM 32 KB 32 KB ← $ 04FFFF D15 - D8 D7 - D0 #UDS #LDS Página 32 de 34 Tema 5 RAM Banco Par Banco Impar Chip 5 Chip 6 RAM RAM 32 KB 32 KB $ FE0000 ← $ FEFFFF $ FF0000 Chip 7 Chip 8 RAM RAM 32 KB 32 KB ← $ FFFFFF D15 - D8 D7 - D0 #UDS #LDS Página 33 de 34 Tema 5 3. Ecuaciones de los Chip Select. En este apartado obtenemos las ecuaciones de las señales que habilitan los distintos chips. Este sum ando imposibilita el acceso a la EPROM para escribir, que provoca ría una colisión en el bus de datos. ___ ____ __ ___ CS1 = A23 + A22 + A21 + A20 + A19 + A18 + R/W + AS + UDS ___ ____ __ ___ CS2 = A2 3 + A22 + A2 1 + A20 + A19 + A18 + R/W + AS + LDS ___ ___ ____ __ ___ CS3 = A2 3 + A22 + A2 1 + A20 + A19 + A18 + A17 + A16 + R/W + AS + UDS ___ ___ ____ __ ___ CS4 = A2 3 + A22 + A2 1 + A20 + A19 + A18 + A17 + A16 + R/W + AS + LDS ___ ___ ___ ___ ___ ___ ___ ___ __ ___ CS5 = A2 3 + A22 + A2 1 + A20 + A19 + A18 + A17 + A16 + AS + UDS ___ ___ ___ ___ ___ ___ ___ ___ __ ___ CS6 = A2 3 + A22 + A2 1 + A20 + A19 + A18 + A17 + A16 + AS + LDS ___ ___ ___ ___ ___ ___ ___ ___ ___ __ ___ CS7 = A2 3 + A22 + A2 1 + A20 + A19 + A18 + A17 + A16 + AS + UDS ___ ___ ___ ___ ___ ___ ___ ___ ___ __ ___ CS7 = A2 3 + A22 + A2 1 + A20 + A19 + A18 + A17 + A16 + AS + LDS Página 34 de 34