Set de instrucciones del MC68000

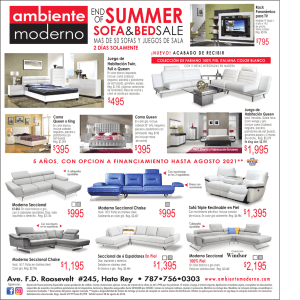

Anuncio

Conjunto de Instrucciones para el Microprocesador MC68000 Notación usada en las tablas Símbolo Significado s d AAA DDD rrr RRR eeeeee EEEEEE MMM CCCC P…P Q…Q SS VVVV u Operando fuente Operando Destino Número de registro de Direcciones Número de registro de Datos Número de registro fuente Número de registro destino Dirección efectiva del operando fuente <Modo><Registro> Dirección efectiva del operando destino <Modo><Registro> Modo de dirección efectiva del destino Especificación de una prueba de código de condición Desplazamiento Datos rápidos inmediatos Tamaño: 00=Byte, 01=Word, 10=Long-Word (En instrucción MOVE: 01=Byte, 11=Word, 10=Long-Word) Número del vector de Trap El estado del código de condición está indefinido Instrucciones de bifurcación condicional Codificación de los modos de direccionamiento Modo Registro Modo de Direccionamiento 000 001 010 011 100 101 110 111 111 111 111 111 - Reg. # Reg. # Reg. # Reg. # Reg. # Reg. # Reg. # 000 001 010 011 100 - Directo en Registro de Datos Directo en Registro de Direcciones Indirecto en Registro Indirecto con Postincremento Indirecto con Predecremento Base más Desplazamiento Base más Indice más Desplazamiento Absoluto Corto Absoluto Largo Relativo con Desplazamiento Relativo con Desplazamiento más Indice Inmediato Inmediato Corto Implícito Códigos de Condición para las Instrucciones Bcc, DBcc y Scc Código Máquina Nemónico Significado Lógica CCCC 0000 T Verdadero 1 0001 F False 0 0010 HI Alto C*.Z* 0011 LS Bajo o Igual C+Z 0100 CC Carry Clear C* 0101 CS Carry Set C 0110 NE <> Z* 0111 EQ = Z 1000 VC Overflow Clear V* 1001 VS Overflow Set V 1010 PL Positivo N* 1011 MI Negativo N 1100 GE >= N.V+N*.V* 1101 LT < N.V*+N*.V 1110 GT > N.V.Z*+N*.V*.Z* 1111 LE <= Z+N.V*+N*.V nota: los códigos T y F no pueden usarse en la instrucción Bcc Máscara de registros en la instrucción MOVEM. Cada posición representa un bit que es puesto a uno si se debe transferir el registro correspondiente. Movimiento REGISTROS Æ Memoria Movimiento Memoria Æ REGISTROS D0.D1.D2.D3.D4.D5.D6.D7.A0.A1.A2.A3.A4.A5.A6.A7 A7.A6.A5.A4.A3.A2.A1.A0.D7.D6.D5.D4.D3.D2.D1.D0