UNDERSTANDING THE LIMITS OF SEMICONDUCTOR

Anuncio

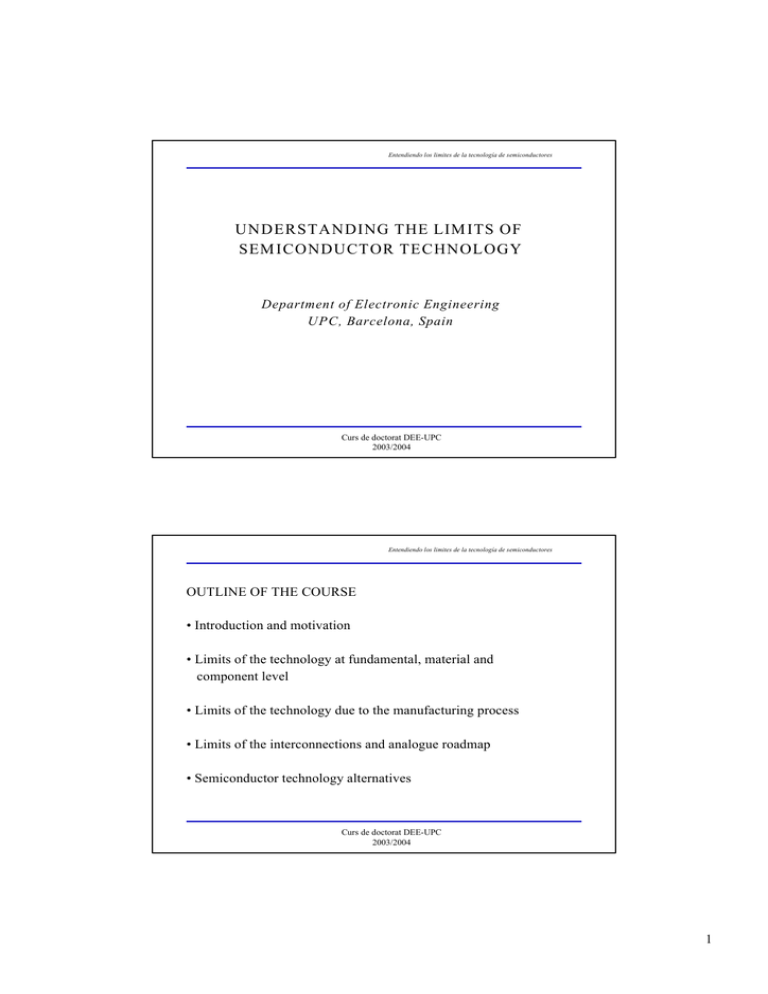

Entendiendo los limites de la tecnología de semiconductores UNDERSTANDING THE LIM ITS OF SEM ICONDUCTOR TECHNOLOGY Department of Electronic Engineering UPC, Barcelona, Spain Curs de doctorat DEE-UPC 2003/2004 Entendiendo los limites de la tecnología de semiconductores OUTLINE OF THE COURSE • Introduction and motivation • Limits of the technology at fundamental, material and component level • Limits of the technology due to the manufacturing process • Limits of the interconnections and analogue roadmap • Semiconductor technology alternatives Curs de doctorat DEE-UPC 2003/2004 1 Entendiendo los limites de la tecnología de semiconductores Causes of limitation in semiconductor technology Fundamental laws Circuit level limitations Materials limitations Manufacturing limitations MOS device limitations Economical limitations Noise and interconnections Manufacturing defects Process fluctuations Curs de doctorat DEE-UPC 2003/2004 Entendiendo los limites de la tecnología de semiconductores Causes of limitation in semiconductor technology Fundamental laws Circuit level limitations Materials limitations Manufacturing limitations MOS device limitations Economical limitations Noise and interconnections Manufacturing defects Analog and RF circuits Test Technology Process fluctuations Curs de doctorat DEE-UPC 2003/2004 2 Entendiendo los limites de la tecnología de semiconductores Moore’s law : the number of integrable devices in a single Semiconductor crystal duplicates each 18 months Evolucion Evolucion of thememorias capacity ofDRAM DRAMs EvolutionEvolución of the complexity of CIsde(Moore’s de la complejidad los CI's Law) 1000 10000 100 (Mbits) 100000 1000 100 10 1 0,1 10 1 1970 1975 1980 1985 1990 1995 2000 0,01 1977 1980 1983 1986 1989 1992 1995 1998 2001 2005 Año Dimension critica (λ ) Photolithography critical dimension (λ) (micras) 2 1,5 1 0,5 0 1985 0.13 1990 1995 2000 0.07 2005 Intel 486 2010 Curs de doctorat DEE-UPC 2003/2004 Entendiendo los limites de la tecnología de semiconductores Semiconductors materials (1) Unitary (2) Compound Si, Ge II III IV V VI Be 5 6 7 8 4 (a) IV-IV (b) III-V (c) II-VI d) IV-VI (3) Alloys (a) Ternary (b) Quaternary Si-Ge Al-P, Al-As, Al-Sb Ga-P, In-P, In-As Zn-O, Zn-S, Zn-Se Zn-Te, Cd-S, Cd-Se Pb-S, Pb-Se, Pb-Te Al xGa 1-x As Cd 1-x Mn x Te Ga As 1-x P x Al x Ga 1-x As y Sb 1-y Ga x In 1-x As 1-y P y 12 B C 13 Al 14 30 Zn 31 Ga 32 48 Cd 49 80 Hg 81 Mg Si Ge N 15 P 33 As In 50 51 Tl 82 83 Sn Pb Sb Bi O 16 S 3·4 Se 52 Te 84 Po Brief periodic table Curs de doctorat DEE-UPC 2003/2004 3 Entendiendo los limites de la tecnología de semiconductores Crystalline structure Estructure Reticular constant (Å) (a) diamant 5,43095 diamant 5,64613 Ga-As zinc-blend 5,65330 Pb-S rock-salt 5,93620 Semiconductor Si Ge (300 K) 1 Å = 10-8 cm Curs de doctorat DEE-UPC 2003/2004 Entendiendo los limites de la tecnología de semiconductores Bloch theorem If U(x) is periodic: U(x+a) = U (x) Ψ (x+a) = e ika Ψ (x) Idealization of Kronig-Penney R. F. Pierret and G. W. Neudeck, Modular Series on Solid State Device, vol. VI, Advanced Semiconductor Fundamentals, Addison-Wesley, 1989 Curs de doctorat DEE-UPC 2003/2004 4 Entendiendo los limites de la tecnología de semiconductores Energy bands in a crystal Ec Eg Ev Forbidden band material Eg (eV) Ge 0.66 Si 1.12 Ga-As 1.42 C 5.4 Curs de doctorat DEE-UPC 2003/2004 Entendiendo los limites de la tecnología de semiconductores N and P type crystals (extrinsec semiconductors) N type P type N type P type Curs de doctorat DEE-UPC 2003/2004 5 Entendiendo los limites de la tecnología de semiconductores Distribution of electron energies and carriers concentrations in Si • Fermi-Dirac energy distribution function fn = 1 1 + exp[(E − E F ) / kT ] • Mass-action law np = n2i • Concentration of majority carriers (room temperature) N-type: ND P-type: NA • Intrinsic carrier concentration: ni = A ⋅ exp(− Eg ) 2kT Intrinsic temperature: about 200ºC Curs de doctorat DEE-UPC 2003/2004 Entendiendo los limites de la tecnología de semiconductores P-N junction device (diode) Curs de doctorat DEE-UPC 2003/2004 6 Entendiendo los limites de la tecnología de semiconductores MOS device ( metal-oxide-semiconductor) • Controllable resitance • Fast switch •Signal amplifier J. P. Uyemura, Fundamentals of MOS Digital Integrated Circuits, Addison, 1989. Curs de doctorat DEE-UPC 2003/2004 Entendiendo los limites de la tecnología de semiconductores The integrated circuit concept: planar technology Patent de Jack Kilby, Nobel 2000 Intel Pentium II J. P. Uyemura, Fundamentals of MOS Digital Integrated Circuits, Addison, 1989. Curs de doctorat DEE-UPC 2003/2004 7 Entendiendo los limites de la tecnología de semiconductores Moore’s law : the number of integrable devices in a single Semiconductor crystal duplicates each 18 months Evolucion Evolucion of thememorias capacity ofDRAM DRAMs EvolutionEvolución of the complexity of CIsde(Moore’s de la complejidad los CI's Law) 1000 10000 100 (Mbits) 100000 1000 100 10 1 0,1 10 1 1970 1975 1980 1985 1990 1995 2000 2005 0,01 1977 1980 1983 1986 1989 1992 1995 1998 2001 Año Dimension critica (λ ) Photolithography critical dimension (λ) (micras) 2 1,5 1 0,5 0 1985 0.13 1990 1995 2000 0.07 2005 Intel 486 2010 Curs de doctorat DEE-UPC 2003/2004 Entendiendo los limites de la tecnología de semiconductores Curs de doctorat DEE-UPC 2003/2004 8 Entendiendo los limites de la tecnología de semiconductores Evolution of the integrated circuits 1958 Kilby’s integrated circuit Pentium 4, 0.18 microns 42 million transistors 1961 First planar process IC • IC area increasing factor, D2, 200 • Critical dimension reduction factor, λ, 1/100 • Packaging efficiency, PE, 50 • Increasing of reliability • Reduction of cost per device • Improvement of relation consumption/delay IBM 70nm transistor 1.2 volts, 27 ps 2 2 8 N = λ− ⋅ D ⋅ PE = 10 Curs de doctorat DEE-UPC 2003/2004 Entendiendo los limites de la tecnología de semiconductores Effects of the miniaturization ELECTROSTATICS area ∝ L2 volume ∝ L3 MECHANICS force ∝ area ∝ L2 deformation ∝ L mass ∝ volume ∝ L3 acceleration ∝ force / mass ∝ L-1 frequency ∝ acoustic speed / length ∝ L-1 time ∝ frequency-1 ∝ L speed ∝ acceleration.time ∝ Constant power ∝ force· speed ∝ L2 frictional force ∝ L2 THERMODYNAMICS heat capacity ∝ volume ∝ L3 thermal conductance ∝ L thermal constant time ∝ L2 voltage ∝ electrostatic length· length ∝ L electrostatic force ∝ area·(E)2 ∝ L2 resistance ∝ length / area ∝ L-1 ohmic current ∝ voltage / current ∝ L2 electrostatic energy ∝ L3 capacitance ∝ energy / (voltage)2 ∝ L magnetic energy ∝ Volume· (B)2 ∝ L5 inductance ∝ energy / (current)2 ∝ L ELECTRODYNAMICS inductive time constant ∝ Ind / R ∝ L2 capacitive time constant ∝ R·C ∝ Constant ELECTRONIC CIRCUIT • Feynman R.P. “There’s plenty of Room at the Bottom” Eng. And Sci., 23:22-36, 1960 • Drexler, K., “Nanosystems”, John Wiley and Sons, 1992 MOS current ∝ L MOS resistance ∝ Constant MOS capacitance ∝ L MOS time constant∝ L power consumption ∝ L2 Curs de doctorat DEE-UPC 2003/2004 9 Entendiendo los limites de la tecnología de semiconductores Evolution of the single bit transition energy 9 10 Landauer88 JSSC Adiabatic 7 10 Moore’s Law limit? Switching energy per gate (pJ) 5 10 3 10 Landauer’s prediction 1 10 -1 10 Adiabatic trend -3 10 -5 10 -7 1 eV 10 -9 10 1940 1960 1980 2000 2020 2040 kTln2 Year R. Landauer, “Irreversibility and heat generation in the computing process”, IBM, J. Res. And Dev., vol. 5, no. 3, pp. 183-191, July 1961. Curs de doctorat DEE-UPC 2003/2004 Entendiendo los limites de la tecnología de semiconductores Atoms per bit of memory V.V. Zhirnov and D. J. Herr, “New Frontiers: Self-Assembly and Nanoelectronics”, Computer, January 2001, pp. 34-43. Curs de doctorat DEE-UPC 2003/2004 10 Entendiendo los limites de la tecnología de semiconductores Curs de doctorat DEE-UPC 2003/2004 “International Technology Roadmap for Semiconductors”, 2001 Entendiendo los limites de la tecnología de semiconductores “International Technology Roadmap for Semiconductors”, 2001 Curs de doctorat DEE-UPC 2003/2004 11 (pJ) Switching energy per gate Entendiendo los limites de la tecnología de semiconductores 10 9 10 7 10 5 10 3 10 1 10 -1 10 -3 10 -5 10 -7 10 -9 1940 Landauer88 JSSC Adiabatic Moore’s Law limit? Landauer’s prediction Adiabatic trend 1 eV kTln2 1960 1980 2000 2020 2040 Year 0.002 fJ Curs de doctorat DEE-UPC 2003/2004 Entendiendo los limites de la tecnología de semiconductores Future evolution • Bohr radius 50 pm • ion Cu2+ radius 73 pm • H2 bond length 74 pm • C C bond length 120 pm • C C bond length 135 pm • C C bond length 150 pm • ion S2- radius 185 pm • Cl2 bond length 198 pm • Si crystal lattice constant 540 pm • gate exide thinness SiO2, conventional technology, foresee year 2010 1nm = 1000 pm • layout resolution of an actual IC, 2001, 120.000 pm (0.12 micres) • typical laateral length of an IC: 15 mm • wavelength of a signal of 10 GHz: 30 cm International Technology Roadmap for Semiconductors, www.sematech.org Curs de doctorat DEE-UPC 2003/2004 12 Entendiendo los limites de la tecnología de semiconductores Physical effects of the feature size reduction • the feature size is reaching the mean free path of carriers “the inelastic mean free path for silicon at room temperature is 100nm” • the feature size is getting close to the wavelength of electrons “the wavelength of electrons carriers flowing parallel to surface is 8-10nm” • the feature size is close to the corresponding to the unitary doping volume “bulk concept is given room to discrete system” • the feature size of the gate oxide (tox) is near of few molecule diameters “the minimum tox deviation causes important effects • the tunnel effects of narrow barriers are becoming significant “for 0.5 volts and a SiO2 barrier of 3 nm the current density is 10-6 A/cm2, while For 1.5 nm is 1 A/cm2” -----> Implications Curs de doctorat DEE-UPC 2003/2004 13