Eliminador clásico de rebotes

Anuncio

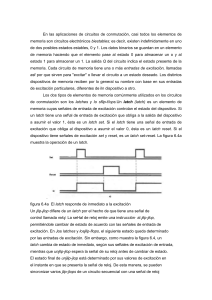

Tres Latches y un Eliminador de Rebotes en la GAL22V10 El proyecto consiste de diseñar tres latches y el eliminador clásico de rebotes que sirvan de fundamento al estudio de los sistemas digitales secuenciales. La figura 1 ofrece diagramas a bloques de un circuito combinatorio y de uno secuencial. Este último presenta una dinámica que no sólo depende de sus entradas lógicas sino que depende además de su estado actual, esto es, presentan la propiedad de contar con memoria y realimentar el contenido de dicha memoria hacia la parte combinatoria según sugiere la figura 1b). Figura 1 Modelo de circuito secuencial a) Circuito lógico combinatorio, b) Circuito lógico secuencial. El un circuito secuencial se tienen n variables de entradas (x1, x2, . . ., xn), m señales de salidas (z1, z2, . . ., zm) y r señales (y1, y2, . . .,yr) y (Y1, Y2, . . ., Yr) que representan el estado presente y el siguiente estado, respectivamente. Los dispositivos de memoria en la figura 1b) pueden ser flip-flops, latches, dispositivos magnéticos, líneas de retardo, relevadores mecánicos, memorias volátiles, etc. Casi todos los elementos de memoria son circuitos electrónicos biestables; es decir adoptan uno de dos posibles estados estables: o 0 o 1 lógicos. La salida Q indica el estado lógico de la memoria. Cada circuito de memoria tiene una o más entradas de excitación, llamadas así porque su función es “excitar” o llevar el circuito a un nivel deseado. Prof. S. Saucedo 1 ICE/2007 Los dos tipos de memoria comúnmente usados en los circuitos de conmutación son los latches y los flip-flops. Un flip-flop difiere de un latch por el hecho de que tiene una entrada de control llamada reloj. La señal de reloj emite una instrucción al flip-flop permitiéndole cambiar de estado de acuerdo con las señales de entrada y del estado actual. Sin embargo, un latch cambia de inmediato su estado al cambiar alguna de sus entradas de excitación, mientras que un flip-flop espera a que su reloj cambie para cambiar de estado. Latch set-reset Uso de la Realimentación para crear latches simples (Estructura NOR) La figura 2 exhibe un latch del tipo set-reset también conocido como latch SR. Básicamente la señal set (S) obliga al latch a que su salida Q tome el valor lógico 1, mientras que su entrada reset (R) obliga a que la salida Q tome el valor lógico 0. El diagrama tradicional del circuito es con acoplamiento cruzado según la figura 2a) lo muestra. Figura 2 Latch set-reset (Latch SR) a) Vista clásica del latch SR y b) Símbolo lógico del latch SR. La ecuación característica del latch set-reset viene dada por Q* = S + RQ Donde Q * es el valor futuro de la salida del latch en función de las dos entradas de excitación y el valor actual de dicha salida. Una restricción en la operación del latch visto es que señales de entrada set y reset no deben ser ambas 1 al mismo tiempo pues la salida no puede ser garantizada en cierto estado. Latch SR con estructura NAND y compuerta para permisivo. En la figura 3 se agrega una señal de control C a un latch SR basado en compuertas NAND de tal manera de poder bloquear o no las señales S y R. El símbolo genérico para un latch con compuerta aparece en la figura 3b). Prof. S. Saucedo 2 ICE/2007 Figura 3 Latch set-reset con compuerta a) Diagrama lógico NAND, b) Símbolo lógico. La ecuación característica del latch set-reset con compuerta viene dada por Q * = SC + RQ + CQ Donde Q * es el valor futuro de la salida del latch en función de las dos entradas de excitación, el control C y el valor actual de dicha salida, Q , como en el caso anterior. Ver latch 74279. Módulo latch D 74LS75 cuádruple El tercer latch a estudiar se ilustra en la figura 4 que emula a una de las cuatro partes del integrado 74LS75 que cuenta con entrada de activación. Cuando HAB tiene el valor 0 la compuerta superior AND se desactiva lo que provoca que el dispositivo tome la forma de retención o de almacenamiento. Si la entrada C cambia a 1, ello crea una ruta desde la entrada DATO hacia la salida del latch, se dice entonces que está en el modo de operación. Figura 4 Diagrama lógico del integrado 74LS75. La ecuación característica del latch tipo D viene dada por Q* = DC + CQ Donde Q * es el valor futuro de la salida del latch en función del dato (D) de entrada, de su señal de Habilitación (C) y del valor actual de dicha salida. La figura 5 brinda el listado fuente del lenguaje ABEL-HDL que diseña los tres latches analizados y el eliminador clásico de rebotes, mediante la retro de dos compuertas NAND. Prof. S. Saucedo 3 ICE/2007 MODULE ffrs TITLE 'Latches tipo RS, D y eliminador de rebotes' X = .x.; "entradas R,S,C,A,B,DATO,HAB pin 2,3,4,7,8,10,11; "salidas Q1n,Q1,Q2n,Q2,QA,QB,Q3n,Q3 PIN 23,22,20,19,17,16,15,14 ISTYPE 'COM'; EQUATIONS Q1n = Q1 = QA = QB = Q2n = Q2 = Q3n = Q3 = !(S # Q1); " Latch SR con NORs !(R # Q1n); !(A & QB); " Eliminador de rebotes (pag. 122 de J. A. Garza) !(B & QA); !(!(C&R) & Q2); " Latch SR con NANDs y activacion !(!(C&S) & Q2n); !(DATO&HAB # Q3&!HAB); " Latch tipo D DATO&HAB # Q3&!HAB; test_vectors ([R,S,C, A,B,DATO,HAB]->[Q1n,Q1,QA,QB,Q2n,Q2,Q3n,Q3]) [0,0,1, [1,0,1, [0,0,0, [0,1,0, [0,0,1, [1,0,1, [0,0,1, [0,1,1, [0,0,0, 0,1, 1,1, 1,0, 1,1, 1,0, 1,1, 0,1, 1,1, 1,0, 0, 0, 1, 0, 1, 1, 1, 0, 1, 0] 1] 1] 1] 0] 1] 0] 1] 1] -> -> -> -> -> -> -> -> -> [X, [1, [1, [X, [X, [1, [X, [X, [0, X, 0, 0, X, X, 0, X, X, 1, 1,0, 1,0, 0,1, X,X, 0,1, X,X, 1,0, X,X, 0,1, X,X, X,X, 1,0, X,X, 1,0, X,X, 1,0, 0,1, 0,1, 1,0]; 1,0]; 0,1]; 1,0]; 1,0]; 0,1]; X,X]; X,X]; X,X]; END Figura 5 Archivo tipo .ABL que define los cuatro dispositivos, sus pines y los vectores de prueba. Tarea Práctica: Diseñar con la GAL usando ABEL-HDL con ispLEVER un latch octal tipo D con tercer estado, semejante al 74LS373, cuya figura se da a continuación (una parte) Prof. S. Saucedo 4 ICE/2007