CONTADORES Y UNIDAD ARITMETICA Y LOGICA

Anuncio

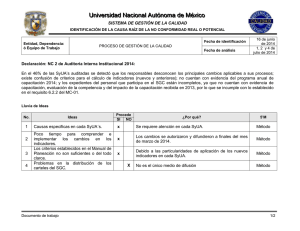

GUIAS ÚNICAS DE LABORATORIO CONTADORES Y UNIDAD ARITMÉTICA Y LÓGICA AUTOR: ALBERTO CUERVO SANTIAGO DE CALI UNIVERSIDAD SANTIAGO DE CALI DEPARTAMENTO DE LABORATORIOS DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE CCOONNTTAADDOORREESS YY UUNNIIDDAADD AARRIITTM MEETTIICCAA YY LLÓÓGGIICCAA CONTADORES Y UNIDAD ARITMÉTICA Y LÓGICA OBJETIVO Los contadores constituyen uno de los circuitos de mayor aplicación en la construcción de sistemas digitales. Igualmente, la Unidad Aritmética y Lógica (ALU: Arithmetic/Logic Unit) es un dispositivo combinacional donde se efectúan las operaciones aritméticas y lógicas en los datos en un computador de acuerdo a un código de selección de entrada a la misma cuyo valor coloca la unidad de control dependiendo de la operación que se debe efectuar. La presente práctica tiene como objetivo reforzar los conocimientos que tiene el estudiante de estos dos dispositivos. Consta de dos partes, en la primera de las cuales se efectúa el diseño de un contador decimal empleando flip-flops JK. En la segunda parte se efectúan distintas operaciones en la ALU colocando entrada el código de selección apropiado. en su PLANTEAMIENTO DEL PROBLEMA Primera parte Diseñe un circuito secuencial sincrónico con cuatro flip-flops A,B,C y D que tenga el diagrama de estados que se muestra. Observe que en este circuito habrán 6 estados no usados. Utilice para su diseño los flip-flops JK y un número mínimo de compuertas que necesite del módulo DIGI BOARD 2 del laboratorio. Las salidas del circuito secuencial serán obtenidas directamente de las salidas de los flip-flops, las cuales deberán ser llevadas al display de 7 segmentos para visualizar el estado del circuito secuencial después que ocurra un pulso de reloj. o 9 1 8 2 7 3 6 4 5 Diagrama de estados DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE CCOONNTTAADDOORREESS YY UUNNIIDDAADD AARRIITTM MEETTIICCAA YY LLÓÓGGIICCAA El circuito debe ser diseñado con la asignación de estados que se muestra en la tabla siguiente: Estado A B C D 0 0 0 0 0 1 0 0 0 1 2 0 0 1 0 3 0 0 1 1 4 0 1 0 0 5 0 1 0 1 6 0 1 1 0 7 0 1 1 1 8 1 0 0 0 9 1 0 0 1 ¿Qué función cree usted que efectúa este circuito? Trabajo en el laboratorio • Coloque inicialmente el estado 0 en su circuito secuencial utilizando las entradas asincrónicas de los flip-flops. • Después de colocar el estado 0, aplique pulsos de reloj con el pulsador del módulo DIGI-BOARD2 a su circuito secuencial para verificar que su funcionamiento coincida con las especificaciones establecidas. Segunda parte En el circuito que se muestra, la Unidad Aritmética y Lógica corresponde a la ALU del módulo DIGI-BOARD2 del laboratorio. A es un registro de 4 bits y B es un número de 4 bits obtenido de uno de los teclados. B 4 BITS reloj A 4 BITS 0 ALU 1 2 3 4 CI s0 s1 s2 s3 s4 M= CI´ DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE CCOONNTTAADDOORREESS YY UUNNIIDDAADD AARRIITTM MEETTIICCAA YY LLÓÓGGIICCAA Utilice para construir el registro A los cuatro flip-flops JK que tiene el módulo DIGIBOARD2 convertidos en flip-flops tipo D, y cualquier compuerta que necesite. Si se efectúan las siguientes operaciones en orden, diga cuál es la salida del registro A después de aplicar cada pulso de reloj. • Utilizando las entradas asincrónicas de los flip-flops, coloque inicialmente el #3 (0011) en el registro A y coloque el número B = 5 (0101) con el teclado. • Coloque las entradas MS3S2S1S0CI´= 010011⇐ (entradas de selección) • Aplique el primer pulso de reloj con el pulsador • Coloque las entradas de selección en 000000 • Aplique el segundo pulso de reloj • Coloque las entradas de selección en 001100 • Aplique el tercer pulso de reloj • Coloque las entradas de selección en 101100 • Aplique el cuarto pulso de reloj • Coloque las entradas de selección en 011001 • Aplique el quinto pulso de reloj. En la solución debe venir dibujado bien explícito este circuito, así como el número almacenado en el registro A después de la aplicación de cada pulso de reloj. DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE CCOONNTTAADDOORREESS YY UUNNIIDDAADD AARRIITTM MEETTIICCAA YY LLÓÓGGIICCAA Trabajo en el laboratorio Monte el circuito, llevando la salida del registro A al display de 7 segmentos para verificar sus respuestas. Los pulsos de reloj deben ser aplicados con el pulsador. SOLUCIÓN Primera parte Estado Presente A B C D 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 Estado siguiente A B C D 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 0 0 0 0 X X X X X X X X X X X X X X X X X X X X X X X X Como D cambia de estado con cada pulso, entonces JD=KD=1 AB 00 01 11 10 00 x x x x x x x x CD 01 11 1 1 x x 10 0 0 x x AB Kc = D 00 01 11 10 00 0 x x 0 o x x 0 CD Estados no usados 01 11 1 x x x 10 0 x x x AB JB=CD 00 01 11 10 00 0 0 x X o 0 x X CD 01 11 0 1 x x 10 0 0 x x De acuerdo con la simplificación efectuada, el circuito será como se muestra a continuación: 1J A 1J 1K A´ 1K B B´ AB 00 01 11 10 00 0 0 x 0 01 1 1 x 0 11 x x x x CD 10 x x x x ABJc = A´D 00 01 11 10 00 x 0 x x 01 x 0 x x 11 x 1 x x 10 x 0 x x CD AB KB=CD 00 01 11 10 00 X x X 0 01 X X x 1 11 x X x x CD 10 x X x x JA=BCD 1J 1K C C´ KA=D 1J 1 1K D D´ pulsos DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE CCOONNTTAADDOORREESS YY UUNNIIDDAADD AARRIITTM MEETTIICCAA YY LLÓÓGGIICCAA Segunda parte • • • • • 1J Q 1J Q 1J Q 1J Q 1K Q´ 1K Q´ 1K Q´ 1K Q´ Después del primer pulso: 8 Después del segundo pulso: 9 Después del tercer pulso: 4 Después del cuarto pulso: 1 Después del quinto pulso: 2 pulsos So S1 S2 S3 M CI del teclado ALU Po Qo BIBLIOGRAFÍA 1. Víctor P. Nelson, H. Troy Nagle, Bill D. Carroll y J. David Irwin, “Análisis y Diseño de Circuitos Lógicos Digitales “, Prentice-Hall Hispanoamericana S.A., 1996 2. System Technick, “DIGI BOARD2 Descripción Técnica “ 3. J.F. Wakerly, “Digital Design Principles and Practices “, 2ª ed., Englewood Cliffs, NJ: Prentice-Hall, 1994 4. F. Hill y G. Peterson, “Digital Systems: Hardware Organization and Design “, Nueva York: John Wiley & Sons, 1973 DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE CCOONNTTAADDOORREESS YY UUNNIIDDAADD AARRIITTM MEETTIICCAA YY LLÓÓGGIICCAA