Familias lógicas parte #1 - Facultad de Ingeniería

Anuncio

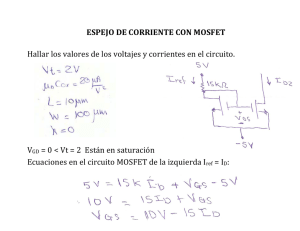

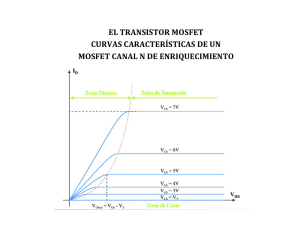

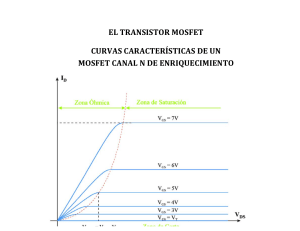

Departamento de Electrónica Electrónica Digital Familias Lógicas (Parte #1) Facultad de Ingeniería Bioingeniería Universidad Nacional de Entre Ríos 1 Una familia lógica es un conjunto de Circuitos integrados con características eléctricas de entrada, salida y circuitería interna similares, pero que realizan diferentes funciones lógicas. Principales parámetros de los CIs digitales: • • • • • • • Voltaje de entrada y de salida. Corriente de entrada y de salida. Fan-in, Fan-out. Retardo de propagación. Margen de ruido. Encapsulados. Denominación e identificación. Voltaje de entrada y salida: Voltaje de salida VOH (min) VOL (max) Voltaje de entrada VIH (min) VIL (max) Corriente de entrada: IIH: Corriente en un terminal de entrada cuando se aplica un voltaje de estado alto. Suministro de corriente IIL: Corriente en un terminal de entrada cuando se aplica un voltaje de estado bajo Vertedor de corriente Corriente de salida: IOH: Corriente máxima que puede suministrar la salida en estado alto manteniendo un voltaje superior a VOH (min). IIL: Corriente máxima que puede consumir la salida en estado bajo manteniendo un voltaje inferior a VOL (max). Fan Out (abanico de salida ó factor de carga): Cantidad de entradas que puede controlar una salida sin exceder sus especificaciones en el peor de los casos. Fan In: Cantidad máxima de entradas. Retardo de propagación. Intervalo de tiempo entre dos puntos de referencia de una entrada y una salida, con la salida cambiando de un nivel lógico a otro. TPHL: El tiempo entre un cambio de entrada y el correspondiente cambio de salida, cuando la salida pasa de ALTO a BAJO. TPLH: El tiempo entre un cambio de entrada y el correspondiente cambio de salida, cuando la salida pasa de BAJO a ALTO. Margen de ruido (NM noise margin): NMH=VNH=VOH(min)-VIH(min) NML=VNL=VIL(min)-VOL(min) Encapsulados: Familia lógica CMOS Complementary Metal Oxide Semiconductor. N-MOS y P-MOS: Alta y Muy Alta escala de integración LSI - VLSI CMOS: Baja – Media - Alta y Muy Alta escala de integración SSI – MSI - LSI - VLSI CANAL N: VGS=0 RDS ͌ 106 Ω + VGS>VT RDS ͌ 1KΩ CANAL P: VGS=0 RDS ͌ 1KΩ VGS<-VT RDS ͌ 106 Ω + Efectos si superamos el Fan Out: FIN!!!!