1 - Sitio Odin.fi

Anuncio

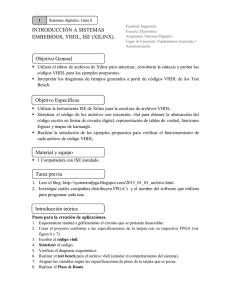

TUTORIAL “LENGUAJE VHDL” PRÁCTICAS DE LABORATORIO PRÁCTICA 1 Los operadores VHDL y las compuertas lógicas Cuando se diseña con lógica programable se requiere del manejo de tres elementos: Lenguaje del tipo “HDL” (Hardware Description Language), Dispositivo lógico programable (CPLD o FPGA) Plataforma de desarrollo. Introducción al lenguaje VHDL Un programa en VHDL requiere de tres módulos fundamentales: El módulo de las bibliotecas (LIBRARY), que es la parte en la que se listan todas las bibliotecas que se usaran en el diseño. Como por ejemplo: ieee, std, work, etc. El módulo de la entidad (ENTITY), que es la parte donde se especifican los pines de entrada/salida del circuito. El módulo de la arquitectura (ARCHITECTURE), que es la parte que contiene el código que describe el comportamiento del circuito. Los comentarios empiezan con dos guiones "--" seguidos, hasta el final de línea. Los caracteres son cualquier letra o número y se escriben entre comillas simples: '2', 't'. Las cadenas son un conjunto de caracteres y se escriben entre comillas dobles: "hola", los bits son en realidad caracteres, y es posible formar con ellos cadenas y representar números por ejemplo: "1110100", O"126", X"FE"; el primer número es binario, el segundo octal, esto se indica con una O antecediendo la cadena, el último número es hexadecimal; indicado por la X delante de la cadena. Palabras reservadas. Son aquellas que tienen un significado especial en VHDL. La entidad puede tomar cualquier nombre, excepto las palabras reservadas En la arquitectura se describe el comportamiento funcional del módulo entidad. La arquitectura incluye una parte declaratoria y una parte operatoria. La parte declaratoria puede incluir diferentes tipos de declaraciones (señales internas, componentes, constantes, etc.). La parte operatoria incluye el código funcional del módulo; La figura I muestra la estructura básica de cualquier código en VHDL. Secciones básicas de un código VHDL. DISEÑO DE SISTEMAS DIGITALES TUTORIAL “LENGUAJE VHDL” PRÁCTICAS DE LABORATORIO LOS OPERADORES VHDL Y LAS COMPUERTAS LÓGICAS OBJETIVO: El alumno aprenderá el funcionamiento de los operadores en lenguaje VHDL para construir diferentes tipos de expresiones mediante los cuales se pueden calcular datos. En lenguaje VHDL existen operadores de asignación con los cuales se transfieren valores de un objeto de datos a otro y operadores de asociación que relacionan un objeto de datos con otro. La figura 1.1 muestra los operadores más utilizados. Figura 1.1 Operadores en lenguaje VHDL. ACTIVIDADES: 1. Crear una carpeta de trabajo, tal como se muestra en la figura 1.2 Figura 1.2. Carpeta de trabajo. 2. 3. Ejecutar la plataforma de desarrollo para lógica programable de Altera (MaxPlus+II o Quartus) o de Xilinx (ISE-Project Navigator). Utilizar la herramienta de diseño en el editor de texto para introducir el código funcional de las diferentes compuertas lógicas en lenguaje VHDL. El archivo en VHDL generado debe tener la extensión *.vhd. La figura 1.3 muestra el código requerido para las compuertas: OR, XOR, AND DISEÑO DE SISTEMAS DIGITALES TUTORIAL “LENGUAJE VHDL” PRÁCTICAS DE LABORATORIO library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity COMPUERTAS is Port ( A : in STD_LOGIC; B : in STD_LOGIC; COR : out STD_LOGIC; CXOR : out STD_LOGIC; CAND : out STD_LOGIC); end COMPUERTAS; architecture Behavioral of COMPUERTAS is begin COR <= A OR B; CXOR <= A XOR B; CAND <= A AND B; end Behavioral; Figura 1.3. Código VHDL para las compuertas: OR, XOR, AND 4. Utilizar la herramienta de simulación de la plataforma de desarrollo para verificar el comportamiento lógico de las compuertas básicas. La figura 1.4 muestra la simulación de esta práctica. Figura 1.4. Simulación del código VHDL para las compuertas: OR, XOR, AND DISEÑO DE SISTEMAS DIGITALES