Ejemplo de diseño de circuito secuencial

Anuncio

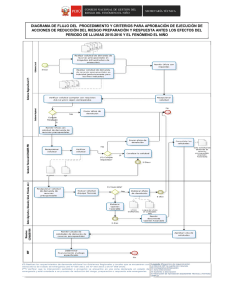

PROBLEMA Diseñar un circuito secuencial que cumpla con los siguientes requerimientos: • Una alarma se encenderá si durante tres o más pulsos de muestreo consecutivos, un sensor se encuentra activo. • Utilizar el modelo de Moore. El problema puede representarse como la detección de una secuencia de entrada. En este caso se busca la secuencia 111, suponiendo que un 1 representa el estado activo del sensor. IDENTIFICACIÓN DE ELEMENTOS DEL DISEÑO Entradas: • Sensor (x) Salidas: • Alarma (z) Estados requeridos • Sensor sin activar (S0) • Sensor activo durante un pulso (S1) • Sensor activo durante dos pulsos consecutivos (S2) • Sensor activo durante tres o más pulsos consecutivos (S3) DIAGRAMA DE ESTADOS Los estados se representan por círculos. Dentro de ellos, se indica el nombre del estado y el valor de la(s) salida(s) que le corresponde(n). Las flechas indican transiciones o cambios de estado. Sobre las flechas se indica el valor de la(s) entrada(s) que provoca(n) tal transición. Las transiciones de estado son controladas por una señal de reloj. Mientras esta señal no se presente, la entrada no es evaluada y no puede existir un cambio de estado. Para probar que el diagrama de estados sea correcto, podemos seguir las siguientes estrategias: 1. Verificar que el número de transiciones (flechas) que salen de cada estado, corresponda al total de combinaciones de entrada posibles. En este caso se tiene una sola entrada. Como esta puede tomar dos valores (0 o 1) entonces debe haber dos transiciones saliendo de cada estado. 2. El funcionamiento se puede probar a partir de la definición de una secuencia de entrada con valores arbitrarios de 1 y 0. Lo que debemos observar con esta prueba es que solamente con la secuencia deseada, se llegue al estado en el cual se activa la salida. Entrada 0 0 1 0 1 1 1 0 1 1 1 1 0 1 1 0 Estado S0 S0 S1 S0 S1 S2 S3 S0 S1 S2 S3 S3 S0 S1 S2 S0 TABLA DE ESTADOS La tabla de estados es una representación alternativa al diagrama de estados. La información que contiene es exactamente la misma, pero es de ayuda para la reducción de estados equivalentes, además de servir como base para la tabla de verdad. Estado Entrada Estado Salida actual (x) siguiente (z) S0 0 S0 0 S0 1 S1 0 S1 0 S0 0 S1 1 S2 0 S2 0 S0 0 S2 1 S3 0 S3 0 S0 1 S3 1 S3 1 Para determinar si dos o más estados son equivalentes y se pueden reducir a uno solo, se verifica el cumplimiento de los criterios siguientes: • Para la misma entrada, el estado siguiente debe ser el mismo. • Las salidas deben ser iguales. En este caso, la primera condición se cumple para los estados S2 y S3, pero la salida es diferente, por lo que no se pueden considerar como equivalentes. SELECCIÓN DE DISPOSITIVOS PARA EL BLOQUE DE MEMORIA En este ejemplo, se utilizarán flip-flops tipo D (FFD). Estos dispositivos son controlados por una señal de reloj. Al momento que ésta se activa, el valor que se encuentra presente en su entrada (D) se carga en su salida (Q). ASIGNACIÓN DE VALORES NUMÉRICOS A LOS ESTADOS Estado S0 S1 S2 S3 B A 0 0 0 1 1 0 1 1 Se tienen 4 estados, por lo tanto se requieren 2 bits para representarlos con un valor numérico. A estos bits les llamaremos variables de estado y los representaremos con letras mayúsculas B y A. En el circuito, las variables de estado son representadas por las salidas de los FF. TABLA DE VERDAD Estado actual x Estado siguiente B A B+ A+ 0 0 0 0 0 0 0 1 0 1 0 1 0 0 0 0 1 1 1 0 1 0 0 0 0 1 0 1 1 1 1 1 0 0 0 1 1 1 1 1 z 0 0 0 0 0 0 1 1 Esta tabla es una representación de la tabla de estados utilizando los valores numéricos que fueron asignados a cada estado. Las columnas de estado actual indican el valor que tendrían los FF en un momento dado. Las columnas de estado siguiente muestran el valor que deben tomar los FF si al activarse la señal de reloj, se encuentra presente el valor de entrada que se indica en la tabla. Al final se muestra el valor de salida que corresponde a cada estado y las posibles combinaciones de entrada. ECUACIONES DE ESTADO SIGUIENTE B A B+ A+ 0 0 0 0 0 0 0 1 0 1 0 1 0 0 0 0 1 1 1 0 1 0 0 0 0 1 0 1 1 1 1 1 0 0 0 1 1 1 1 1 z 0 0 0 0 0 0 1 1 Para obtener las ecuaciones de estado siguiente, utilizaremos la sección de la tabla que se encuentra sombreada. Esto se realizará por medio de mapas de Karnaugh. x B+ 00 01 11 10 x 0 1 0 0 0 0 0 1 1 1 A+ 00 BA x Estado siguiente BA Estado actual 01 11 10 0 1 0 0 0 0 1 0 1 1 Los valores que se colocan en el exterior de las tablas corresponden al estado actual y a las entradas del circuito (en amarillo). El mapa se llena con los valores del estado siguiente (en azul): la columna B+ se utiliza para obtener la ecuación de estado siguiente del FF B, mientras que la columna A+ se utiliza para la del FF A. Para llenar el mapa, se sigue algo similar a un sistema de coordenadas. Una vez que los mapas se han llenado, se realizan las agrupaciones de los términos y se obtienen las siguientes ecuaciones: B+= BX + AX = X (A+B) A+= BX + /AX = X (/A + B) ECUACIONES DE SALIDA Como el circuito se diseñó siguiendo el modelo de Moore, la salida depende únicamente del valor del estado actual. Por lo tanto, la tabla de verdad para la salida, y el mapa para obtener la ecuación quedan de la siguiente forma: Estado actual B A z B A 0 0 0 0 1 0 1 0 0 1 1 1 Z 0 0 0 0 0 1 1 1 De aquí se obtiene la ecuación de la salida: Z = AB CONSTRUCCIÓN DEL CIRCUITO Utilizando las ecuaciones anteriores, se obtiene el siguiente diagrama para el circuito: Al simularlo con el software Quartus II Web Edition, utilizando la misma secuencia de prueba con la que se verificó el diagrama de estados, se obtiene el siguiente diagrama de tiempos: En este diagrama puede notarse que el valor de la entrada es considerado solamente cuando hay una transición positiva en la señal de reloj. Es en ese momento cuando puede presentarse un cambio en el estado o en la salida.