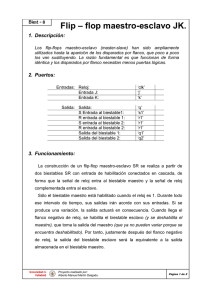

LABORATORIO DE TECNOLOGÍA DE COMPUTADORES PRÁCTICA 9

Anuncio

LABORATORIO DE TECNOLOGÍA DE COMPUTADORES

PRÁCTICA 9

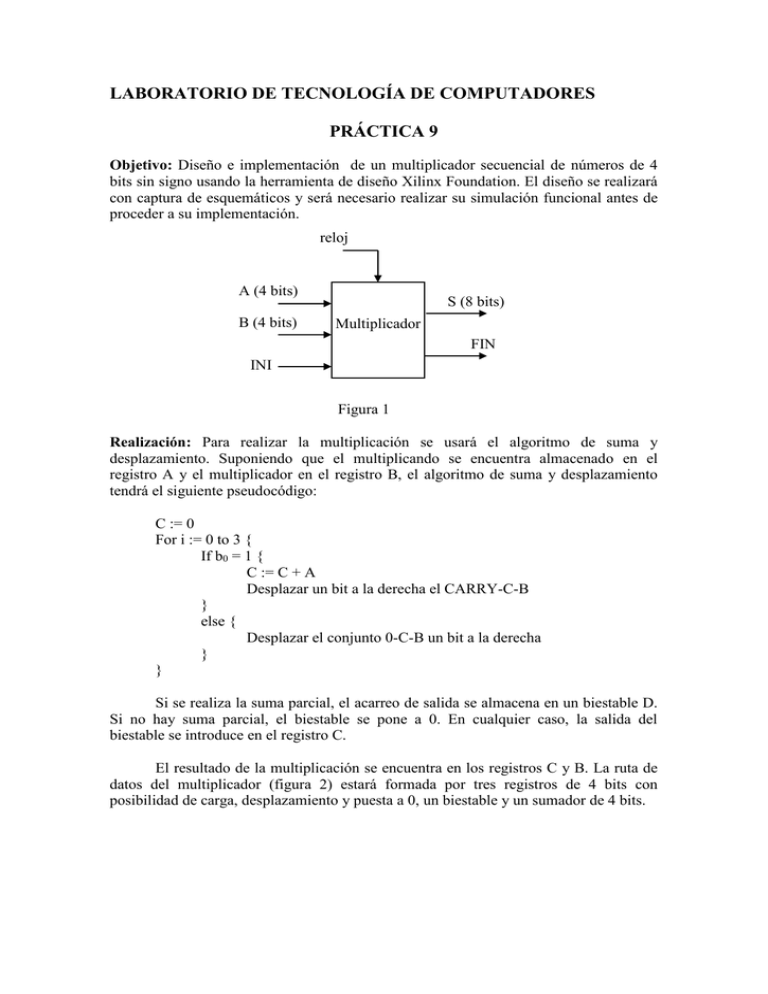

Objetivo: Diseño e implementación de un multiplicador secuencial de números de 4

bits sin signo usando la herramienta de diseño Xilinx Foundation. El diseño se realizará

con captura de esquemáticos y será necesario realizar su simulación funcional antes de

proceder a su implementación.

reloj

A (4 bits)

B (4 bits)

S (8 bits)

Multiplicador

FIN

INI

Figura 1

Realización: Para realizar la multiplicación se usará el algoritmo de suma y

desplazamiento. Suponiendo que el multiplicando se encuentra almacenado en el

registro A y el multiplicador en el registro B, el algoritmo de suma y desplazamiento

tendrá el siguiente pseudocódigo:

C := 0

For i := 0 to 3 {

If b0 = 1 {

C := C + A

Desplazar un bit a la derecha el CARRY-C-B

}

else {

Desplazar el conjunto 0-C-B un bit a la derecha

}

}

Si se realiza la suma parcial, el acarreo de salida se almacena en un biestable D.

Si no hay suma parcial, el biestable se pone a 0. En cualquier caso, la salida del

biestable se introduce en el registro C.

El resultado de la multiplicación se encuentra en los registros C y B. La ruta de

datos del multiplicador (figura 2) estará formada por tres registros de 4 bits con

posibilidad de carga, desplazamiento y puesta a 0, un biestable y un sumador de 4 bits.

LA

CC LC DC

LB DB

4

4

A

D

C

C0

B

b0

Cin

SUMADOR

0

CD

Salida

Figura 2

El diagrama de estados de un posible controlador para implementar este

algoritmo con la ruta de datos de la figura 2 se muestra en la figura 3.

S0

F

S1

Fin

F

S2

Fin

S3

Figura 3

La señal F es el resultado de comparar el valor de la señal de entrada INI en un

instante de tiempo anterior (valor almacenado en un biestable) y el actual. Si la señal

INI ha cambiado el valor de F será 1 y procederemos con la multiplicación, sino será 0 y

se permanecerá en el estado S1 a la espera de que esta señal cambie (F= XOR(INI,

INI_OLD).

Para construir la máquina de estados usaremos biestables D y puertas lógicas. La

realimentación entre los estados S2 y S3 representa el bucle for y se tendrá que realizar 4

veces (para lo cual se utilizará un contador módulo 4 para contar el número de veces

que se ha ejecutado el bucle). Tras la cuarta iteración del bucle (estado contador = 11),

la señal FIN se pondrá a 1 y habrá terminado la multiplicación.

S0:

S1:

S2:

S3:

Se carga en un biestable el valor de la señal INI y a continuación el

sistema siempre se va al estado S1.

Si F = 1 se cargan los registros A y B con el valor de los operandos (LA

= LB = 1). Se inicializa a 0 el registro C (CC = 1). Y se pasa a S2.

Si B0 = 1 se carga en el registro C (LC = 1) el resultado de la suma A + C,

y se carga el biestable D con el acarreo.

Si B0 1, se inicializa el biestable D a 0 (CD = 1) y se pasa al estado S3.

Se incrementa el contador del bucle (INC = 1) y se desplaza el conjunto

D – C – B (DC y DB = 1).

Si FIN = 0 se vuelve al estado S2.

Si FIN = 1 se vuelve al estado S0.