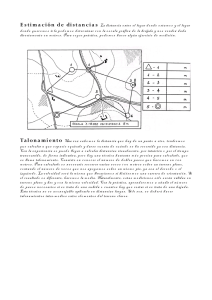

Tcp Tmem Memoria Principal Mem Rd Wr a Dir A ALU entera Mux X

Anuncio

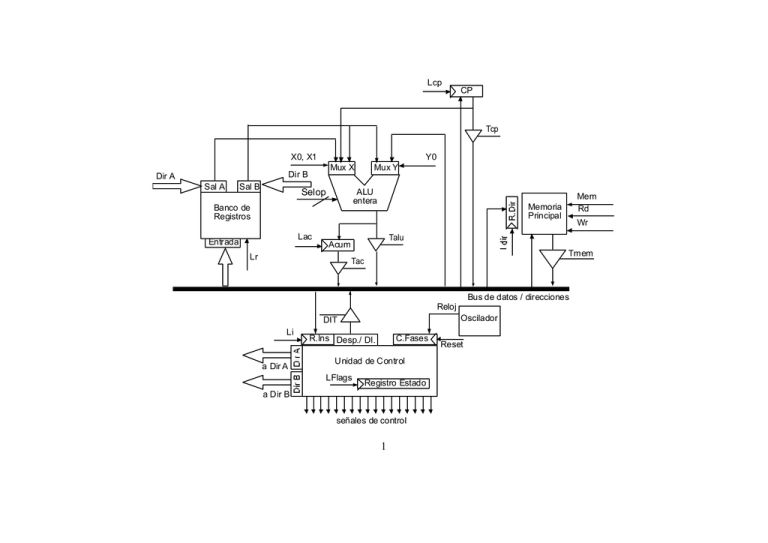

Lcp CP Tcp X0, X1 Y0 Mux X Dir B Dir A Sal A Sal B ALU entera Selop Banco de Registros Lac Entrada Mux Y Wr Talu Acum Lr Mem Rd Memoria Principal Tmem Tac Bus de datos / direcciones Reloj Oscilador DIT Li a Dir A R.Ins Desp./ DI. C.Fases Unidad de Control LFlags Registro Estado a Dir B señales de control 1 Reset Lcp CP Inc X0 Y0 Mux X Dir B Dir A Sal A Sal B Banco de Registros Lac Mux Y ALU entera Selop Entrada Tcp Wr Talu Acum Lr Mem Rd Memoria Principal Tmem Tac Bus de datos Tbdad Tadbd Bus de direcciones Reloj Oscilador DIT Li a Dir A C.Fases R.Ins Desp./ DI. Unidad de Control LFlags Registro Estado a Dir B señales de control 2 Reset Lcp CP Inc Tcp Dir. Salida ALU entera Selop Banco de Registros Lac Entrada Wr Talu Acum Lr Mem Rd Memoria Principal Tmem Tac Bus de datos Tbdad Tadbd Bus de direcciones Reloj Oscilador DIT Li R.Ins Desp./ DI. C.Fases Unidad de Control a Dir LFlags Registro Estado señales de control 3 Reset Lcp CP Inc Tcp Dir. Salida Banco de Registros Entrada Lr ALU mul / div Selop Lac Talu Acum Selop2 ALU add / sub Mem Rd Memoria Principal Wr Acum2 Lac2 Tmem Talu2 Tac Bus de datos Tbdad Tadbd Bus de direcciones Reloj Oscilador DIT Li R.Ins Desp./ DI. C.Fases Unidad de Control a Dir LFlags Registro Estado señales de control 4 Reset Lcp CP Tcp X0, X1 Y0 Mux X Dir B Dir A Sal A Sal B ALU entera Selop Banco de Registros Lac Entrada Mux Y Reloj Ttmp Ltmp SP Oscilador DIT Li Tmp Wr Tmem Tac Bus de datos / direcciones Tsp Lsp Mem Rd Talu Acum Lr Memoria Principal R.Ins Desp./ DI. C.Fases Unidad de Control a Dir A LFlags a Dir B señales de control 5 Registro Estado Reset Lcp Inc Mux X Dir. CP Tcp X0 Salida Banco de Registros Selop Entrada Lr Lac ALU 1 mul / div ALU 2 add / sub Talu Acum Selop2 Mem Rd Memoria Principal Wr Acum2 Lac2 Tmem Talu2 Tac Bus de datos Tbdad Tadbd Bus de direcciones Reloj Tsp Lsp Ttmp Ltmp SP Oscilador DIT Li Tmp R.Ins Desp./ DI. C.Fases Unidad de Control a Dir LFlags Registro Estado señales de control 6 Reset Lcp CP Inc X0 Y0 Mux X Dir A Mux Y Salida ALU coma fija Banco de Registros de coma fija Entrada Lr Lac Selop Mem Rd Memoria Principal Talu Ltmp Acum Tmp Wr Tmem Ttmp Tac Talu2 Bus de datos Tbdad Tadbd Lr2 Entrada Banco de Registros de coma flotante Sal A Acum2 Bus de direcciones Lac2 Reloj ALU coma flotante Selop2 Li Sal B Dir B Oscilador DIT Mux X X0' Dir A Tcp Mux Y a Dir A R.Ins Desp./ DI. Unidad de Control LFlags Y0' C.Fases Registro Estado a Dir B señales de control 7 Reset 8 9 1 X0 Y0 Selo p Lac Tac Ta lu L cp Tcp In c Ld ir Me m Rd Wr Tme m Ta db d Tb da d Dir A Di r B Lr Di t Li Lfla gs Re se t 2 Selop Lac Tac Talu Lcp Tcp Inc Ldir Mem Rd Wr Tmem Tadbd Tbdad Dir Lr Di t Li Lflags Reset 3 Selop Lac Tac Talu Lcp Tcp Inc Ldir Mem Rd Wr Tmem Tadbd Tbdad D ir Lr Di t Li Lflags Reset 4 X0, X1 Y0, Y1 Selop Lac Tac Talu Lcp Tcp Ldir Mem Rd Wr Tmem Tadbd Tbdad Dir A Dir B 5 X0 Selo p 2 L a c2 Ta c Talu 2 L cp Tcp Inc Ld ir M em Rd Wr Tm em Ta db d Tb da d Dir Lr D it Li Ltm p Ttm p Lfla g s R ese t Lr 2 La c 6 X0' Y0' Selop2 Lac2 Tac Talu2 Lcp Tcp Inc Ldir M em Rd Wr Tm em Tadbd Tbdad Dir A Lr 2 D it Li Ltm p Ttm p Lflags R eset Lr Lac 7 X0, X1 Y0, Y1 Selop Lac Tdir Tal u Lcp Tcp Inc Ldir Mem R /W Tm em Lb Lc Ld Lsp Tsp Lfl ags Reset Li 8 9