tema 5. generadores y sintetizadores de señales

Anuncio

5

Generadores y Sintetizadores de

Señales

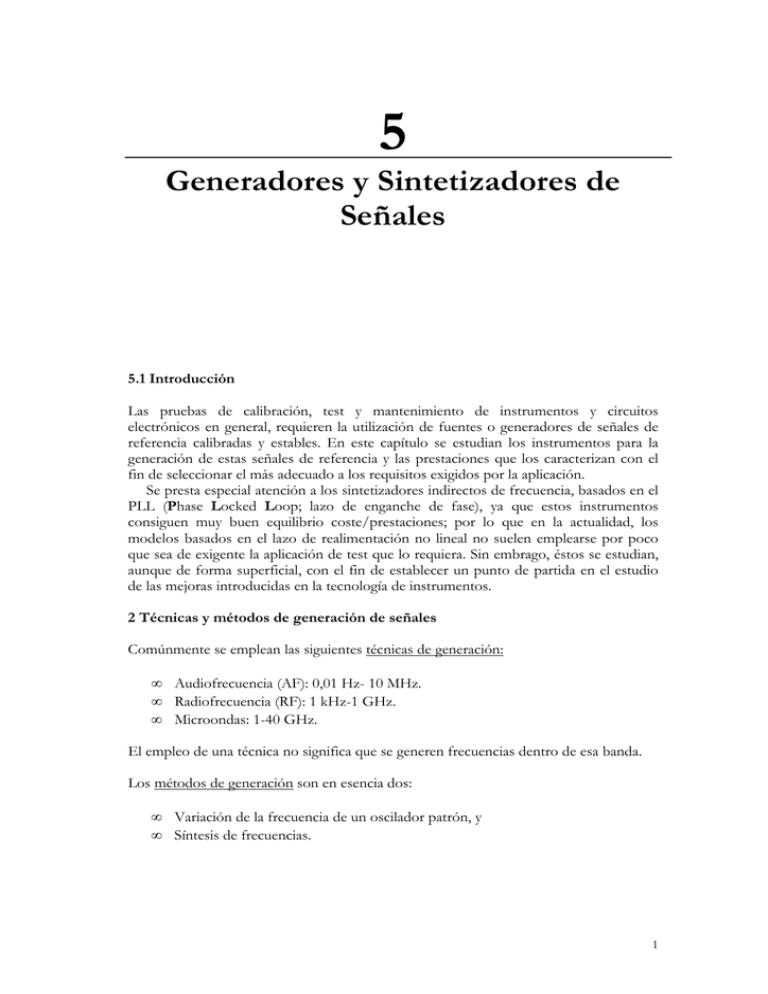

5.1 Introducción

Las pruebas de calibración, test y mantenimiento de instrumentos y circuitos

electrónicos en general, requieren la utilización de fuentes o generadores de señales de

referencia calibradas y estables. En este capítulo se estudian los instrumentos para la

generación de estas señales de referencia y las prestaciones que los caracterizan con el

fin de seleccionar el más adecuado a los requisitos exigidos por la aplicación.

Se presta especial atención a los sintetizadores indirectos de frecuencia, basados en el

PLL (Phase Locked Loop; lazo de enganche de fase), ya que estos instrumentos

consiguen muy buen equilibrio coste/prestaciones; por lo que en la actualidad, los

modelos basados en el lazo de realimentación no lineal no suelen emplearse por poco

que sea de exigente la aplicación de test que lo requiera. Sin embrago, éstos se estudian,

aunque de forma superficial, con el fin de establecer un punto de partida en el estudio

de las mejoras introducidas en la tecnología de instrumentos.

2 Técnicas y métodos de generación de señales

Comúnmente se emplean las siguientes técnicas de generación:

•

•

•

Audiofrecuencia (AF): 0,01 Hz- 10 MHz.

Radiofrecuencia (RF): 1 kHz-1 GHz.

Microondas: 1-40 GHz.

El empleo de una técnica no significa que se generen frecuencias dentro de esa banda.

Los métodos de generación son en esencia dos:

•

•

Variación de la frecuencia de un oscilador patrón, y

Síntesis de frecuencias.

1

Instrumentación Electrónica. Juan José González de la Rosa

Otro criterio de clasificación que suele emplearse es la forma de onda de la salida:

•

•

•

•

•

•

•

Generadores de funciones matemáticas,

Generadores de señales sinusoidales moduladas,

Generadores de barrido,

Osciladores de precisión,

Generadores de pulsos,

Generadores de funciones a la carta y ruidos “blanco” y “rosa”.

Generadores de palabras digitales, etc.

3 Generadores de funciones matemáticas

Estos instrumentos entregan señales que pueden describirse mediante ecuaciones y

fórmulas matemáticas.

3.1 Esquema de bloques

Se basa en la estructura o circuitos del lazo de realimentación no lineal. El ejemplo 1

muestra el funcionamiento cualitativo basado en un circuito electrónico.

3.2 Elementos de ajuste en el generador de funciones

El bloque de realimentación del ejemplo 1 se denomina oscilador principal, y genera las

señales cuadrada y triangular. Las señales generadas por el oscilador principal pasan a la

etapa de salida donde se las procesa para generar en el terminal de salida del instrumento

una señal con impedancia de salida adecuada a la aplicación en curso; lo usual es 50 Ω.

La corriente del integrador se corrige mediante dos generadores de corriente

controlados por tensión. Las entradas de estos generadores de corriente son el resultado

del ajuste fino de frecuencia y del establecimiento de la simetría de la señal; que

determina la duración de los semiciclos positivo y negativo (ciclo de trabajo). El

diagrama de bloques de la figura 1 muestra la acción de control mencionada.

+ ∆V MILLER

Fuente de

+ ∆IMILLER

Señales

corriente

Oscilador principal

cuadrada y

controlada

no lineal

- ∆V MILLER

I

MILLER

∆

triangular

por tensión

Fig. 1. Ajuste de la frecuencia y del ciclo de trabajo corrigiendo la corriente del integrador

“Miller.

Las entradas de tensión que ofrecen las salidas de corrección de corriente de la figura 1

provienen de las salidas diferenciales de un amplificador diferencial corregidas por el

ajuste de simetría. A su vez, la entrada de este amplificador diferencial de salida dual es

el resultado de la suma de tres señales de CC:

•

•

•

2

Ajuste fino de frecuencia,

entrada externa VCO (Voltage Controlled Oscillator),

entrada del generador de control.

5 Generadores y Sinterizadotes de Señales

El generador de control permite realizar un barrido en frecuencia aplicando una señal de

diente de sierra. Si el barrido es lineal el generador ofrece cada frecuencia durante el

mismo tiempo; en caso de ser logarítmico se emplea el mismo tiempo por décadas.

Cuando actúa el generador de control se inhiben las señales de ajuste fino y de VCO.

Ejemplo 1. La figura 1 Ej1 muestra un ejemplo de circuito electrónico que implementa un generador

de funciones. El circuito muestra el comparador regenerativo unido al integrador “Miller”,

cuya salida es la entrada del primero.

C

+V

+

(1- α)Roff

αRoff

-V

(1-β

β)RF

-

vo1

-

R2

R1

-

AO1

AO2

+

v o2

+

β RF

(1-χ)Rs

Dz1

+V

χRs

-V

Dz2

Fig. 1. Ej. 1. Lazo de realimentación no lineal basado en circuitos

con amplificadores operacionales.

La figura 2 Ej. 2 muestra las señales que entrega este circuito en la que se observa la

generación simultánea de señales cuadradas y triangulares.

(V)

v o2

v o1

V z1

V1

t (ms)

0

V2

T

V z2

Fig. 2. Ej. 2. Señales generadas por el circuito de la figura 1. Ej.1.

Se aprecia en la figura anterior que la frecuencia de las señales de salida dependen de la

constante de tiempo del integrador, de la relación de división β y de los valores

extremos de la salida, dados por los diodos “Zéner”. En concreto, el periodo de la señal

viene dado por:

T = 2⋅

R1

⋅ C ⋅ (V1 − V 2 )

Vz

3

Instrumentación Electrónica. Juan José González de la Rosa

3.3 Aplicaciones de los generadores de funciones

La señal cuadrada se emplea para test de velocidad en la medida de tiempos de subida y

bajada. La señal triangular se usa para verificar la linealidad de los circuitos. La señal

senoidal se emplea para realizar barridos en frecuencia y obtener la respuesta en

frecuencia de circuitos electrónicos.

4 Generadores de pulsos

4.1 Fundamentos

Estos instrumentos ofrecen pulsos o trenes de pulsos de tensión y/o corriente. Un

pulso viene descrito por:

•

•

•

•

Retardo respecto a una referencia interna del instrumento

duración o anchura,

transiciones o tiempos de subida y de bajada, y

periodo.

4.2 Aplicaciones

Los pulsos se emplean como estímulos de circuitos electrónicos con el fin de examinar

su velocidad y tiempo de respuesta. Se emplean los pulsos dobles para medir la

velocidad de recuperación de los circuitos.

4.3 Diagrama de bloques

La figura 2 muestra el diagrama de bloques.

Oscilador

principal

Monoestable

de retardo

Monoestable

de anchura

Transiciones:

Subida y Bajada

Generación de señal para

sincronismo con otro equipo

Recorte o

limitación

Amplitud e

impedancia

Salida

Fig. 2. Diagrama de bloques de un generador de pulsos.

5 Osciladores controlados por tensión (VCO)

5.1 Definiciones y diagrama de bloques

El oscilador controlado por tensión es un convertidor de tensión analógica a una señal

cuadrada cuyos niveles lógicos dependen de la tecnología de fabricación. El más común

es el 566 fabricado por Signetics (entre otros fabricantes, NE/SE566).

La figura 3 muestra el diagrama de bloques. La figura 4 muestra el montaje

experimental. Tiene dos salidas separadas. La resistencia y el condensador externos

determinan la frecuencia del oscilador. El condensador se carga y se descarga a

velocidad constante a través de R0 y C0. Esta carga y descarga a corriente constante es

característica del integrador “Miller” y provoca la señal triangular; la señal cuadrada se

obtiene haciendo pasar la triangular por un disparador de Schmitt.

4

5 Generadores y Sinterizadotes de Señales

La frecuencia de la salida en los terminales 3 y 4 responde a la siguiente ecuación:

fo =

2

R0 C 0

v

⋅ 1 − i

V

cc

(1)

En (1) he puesto el subíndice “o” (de output) “salida” y hablo de “fo” cuando se aplica

entrada exterior, y de “fFR” en ausencia de entrada, cuando el circuito oscila libremente.

Realizado un montaje experimental en ausencia de entrada (con el terminal 5 sin

conectar a la entrada) se obtiene, a partir de la ecuación (1), un valor concreto de

frecuencia a partir de la tensión en dicho terminal 5, que origina el propio circuito:

V

⋅ 1 − 5 =

Vcc

10,43

= 4

⋅ 1 −

= 556,73759 ≈ 557 Hz

−9

12

10 (Ω) ⋅ 47 ⋅10 ( F )

f FR =

2

R0 C 0

v

⋅ 1 − i

Vcc

2

2

=

R C

0 0

Esta es la frecuencia de las señales triangular y cuadrada que se miden en las patas 3 y 4

del circuito integrado 566.

Vcc=+12 V

R0=10 kΩ

Ω

vi

Fuentes de

corriente

Disparador

de Schmitt

Amplificador

Aislador,

Buffer

Amplificador

Aislador,

Buffer

cuadrada

triangular

C0=0,047 µF

Fig. 3. Diagrama de bloques del VCO digital integrado 566.

Aparecen como componentes externos el condensador y la

resistencia, que determinan la frecuencia de oscilación.

Esta frecuencia se denomina frecuencia de oscilación libre1, o frecuencia en ausencia de

entrada. También se llama frecuencia de reposo o central. Es la frecuencia propia de un

oscilador, y se calcula a partir de la tensión en el terminal “5” del VCO, en ausencia de

entrada, mediante un simple divisor de tensión a partir del circuito de la figura 4:

V5 = Vcc

1

R2

10 (kΩ)

= 12 (V )

≅ 10,434783 (V ) ≈ 10,43 (V )

R1 + R 2

1,5 (kΩ) + 10 (kΩ)

Free Running frequency: traducción de la denominación internacional que proporciona el subíndice.

5

Instrumentación Electrónica. Juan José González de la Rosa

Si el valor de la resistencia R1 se incrementa hasta 2 kΩ, la tensión en el terminal V5

pasa a valer:

V5 = Vcc

R2

10 (kΩ)

= 12 (V )

= 10 (V )

R1 + R 2

2 (kΩ) + 10 (kΩ)

Consecuentemente, la frecuencia de oscilación aumentará según (1):

f FR =

V

⋅ 1 − 5

V cc

2

R0 C 0

2

4

10

=

10 4 (Ω) ⋅ 47 ⋅10 −9 ( F ) ⋅ 1 − 12 = 0,00564 = 709 Hz

Simplemente por tener otra cuenta, pruébese que con R1=1 kΩ, R2=9 kΩ y C0=0,027

µF, sale V5=10,8 V y fo=617,3 Hz.

Como se observa en la figura 4, aplicando mediante un condensador de acoplo una

entrada podemos conseguir señales de frecuencia modulada (FM). Por ejemplo, si la

entrada es sinusoidal de frecuencia 1 kHz de valor medio nulo y 2 Vpp, en teoría se

sumará y restará 1 a la tensión de reposo del terminal 5 para obtener los dos valores

extremos de la frecuencia de oscilación; la frecuencia de oscilación de la salida variará

con 1 kHz de frecuencia (frecuencia de la señal sinusoidal de entrada). Estos dos valores

se sitúan a ambos lados de la frecuencia de reposo, que por ello se la denomina central.

Vcc

R1=1,5

kΩ

Ω

R0

Cac

V5 Cdesac

vi

R2=10

kΩ

Ω

6

5

8

cuadrada

VCO 3

566

triangular

4

1

7

C0

Fig. 4. Montaje experimental con el VCO 566; se

detallan los terminales.

Con el fin de calcular los dos valores extremos entre los que oscila la frecuencia de salida

aplicamos la ecuación (1) y sustituimos a la entrada los picos de tensión. Con una

tensión de entrada de ±1 V de pico (2 Vpp) sabemos que la tensión en el terminal 5 será

de 10,43 más 1 V, y de 10,43 menos 1 V. Así la tensión en el terminal 5 tomará los

valores 11,43 V y 9,43 V, para los picos de entrada positivo y negativo respectivamente.

para V5 = 11,43 V →

f =

6

2

R0 C 0

V

⋅ 1 − 5

Vcc

2

1,14

11,43

=

10 4 (Ω) ⋅ 47 ⋅10 −9 ( F ) ⋅ 1 − 12 = 0,00564 ≈ 202 ( Hz )

5 Generadores y Sinterizadotes de Señales

para V5 = 9,43 V →

f =

2

R0 C 0

V

⋅ 1 − 5

Vcc

2

5,14

9,43

=

10 4 (Ω) ⋅ 47 ⋅10 −9 ( F ) ⋅ 1 − 12 = 0,00564 ≈ 911 ( Hz )

Se observa que cuando la tensión de entrada va de 10,43 V a 11,43 V, la frecuencia de

salida disminuye de 577 (frecuencia de reposo) a 202 Hz; similarmente, cuando la

tensión de entrada disminuye de 10,43 a 9,43 V, la frecuenta aumenta desde 577 a 911

Hz. Es decir, que 577 es la frecuencia central entre 202 y 911 Hz. Este es un proceso de

modulación en frecuencia FM. Este es el principio operativo de los sensores que

convierten tensión en frecuencia.

Así, el rango de frecuencias del circuito se obtiene a partir del rango de tensiones de

entrada. Tenemos las frecuencias ala y baja, límites del rango y su variación:

fH =

V5( mín)

2 V5( máx )

⋅ 1 −

f

=

⋅ 1−

L

Vcc

R0 C 0

V cc

2

2

− fL =

⋅ V5( máx ) − V5( mín ) =

∆V

Vcc R0 C 0

Vcc R0 C 0

2

R0 C 0

∆f = f H

[

]

La expresión anterior corresponde a la sensibilidad del circuito, que se define como:

S=

∆f

2

=

∆V Vcc R0 C 0

Es de destacar que las cuentas que hemos realizado al explicar el proceso de modulación

en frecuencia se verifican, si la impedancia vistas por la fuente de entrada de tensión (Vi)

es infinita. Esta aproximación se basa en el dibujo de la figura 5.

Vi

V5

Zi

10,43 V

Z’

Fig. 5. Circuito equivalente que se

presenta en la entrada del VCO.

En efecto, según la figura 5 se tiene:

V5 = (Vi + 10,43)×

Z'

≈

Zi + Z'

{Z ' → ∞}

≈ Vi + 10,43

7

Instrumentación Electrónica. Juan José González de la Rosa

6 El lazo de enganche de fase (PLL)

6.1 Concepto y definiciones

El de bucle de captura de fase (PLL; Phase Locked Loop; lazo de enganche de fase) es

un circuito con realimentación negativa cuyo objetivo principal consiste en generar una

señal de amplitud fija y frecuencia coincidente con la de entrada, dentro de un margen

determinado.

Cuando el PLL está fuera de sintonía, la salida adopta la frecuencia de oscilación libre

o pulsación central (wFR). El margen de enganche, ∆wL, es la banda de frecuencias entre

las que el PLL se mantiene en sintonía. En esta banda, las pulsaciones de entrada y

salida coinciden. Estando fuera de sintonía el circuito oscila a la pulsación central, y

puede sintonizar las frecuencias de entrada comprendidas en una estrecha franja

denominada margen de captura, ∆wC, y contenida en el margen de enganche. La

frecuencia de oscilación libre se sitúa en el centro geométrico de estos márgenes. La

figura 6 muestra esta distribución espectral.

wLI

wCI

wFR

wCS

wLS

wi

∆ wC

∆ wL

Fig. 6. Distribución espectral de las frecuencias

características de un PLL: Frecuencia central

(wFR), frecuencia de captura superior (wCS) e

inferior (wCI), y frecuencia de enganche superior

(wLS) e inferior (wLI).

6.2 Componentes y funcionamiento de un PLL

La figura 7 muestra el diagrama de bloques de un circuito PLL. En él se aprecia el

detector de fase (PD), cuya salida depende del valor absoluto del desfase entre las

señales de salida vo(t) y la de entrada vi(t).

vi

(wi, θi)

vo

PD, K

V/rad

vd

F(s)

A

vf

VCO, KO rad/seg/V

(wo, θo)

Fig. 7. Diagrama de bloques de un PLL. Se muestran las

señales (variables) de entrada y salida del circuito.

Si se utiliza un comparador de fase de tipo multiplicador (de constante K):

v d = K ⋅ (v1 × v 2 ) = K ⋅ [V1 sen(w1t + θ1 )× V 2 sen(w2 t + θ 2 )]

=

8

K ⋅ V1V 2

⋅ [cos((w1 − w2 )t + θ1 − θ 2 ) − cos((w1 + w2 )t + θ1 + θ 2 )]

2

(2)

5 Generadores y Sinterizadotes de Señales

Como se observa, se origina una frecuencia suma y otra frecuencia diferencia. El filtro

paso-bajo [F(s)] transmite sólo la componente de baja frecuencia del detector. Esta señal

casi continua (de baja frecuencia) establece la frecuencia de oscilación de un oscilador

controlado por tensión (VCO), cerrando el lazo de realimentación.

En situación de enganche, la frecuencia de la señal de salida coincide con la de

entrada (pulsaciones 1 y 2 de la ecuación de anterior), y la tensión de salida del filtroamplificador es continua y depende de la diferencia de desfases:

v f = K D ⋅ cos (θ o − θ i )

(3)

donde KD es una constante que depende de la constante del detector de fase K, y de las

amplitudes de entrada y de salida. Se considera la igualdad en la expresión (3)

suponiendo esta señal tenga frecuencia nula (sólo nos quedamos con la componente de

CC).

Ahora se realiza una aproximación de Taylor del coseno de la diferencia de desfases

anterior. Para ello se recuerda el desarrollo redefiendo nuestra variable de trabajo por

comodidad:

x ≡ θo − θi ;

cos(x ) ≅ cos(x 0 ) − sen(x 0 ) ⋅ (x − x 0 ) − cos(x 0 ) ⋅

(x − x 0 )2

2

+ ...

Si se utiliza el desarrollo en torno al punto x0=π/2, se anula el término de segundo orden

y resulta una aproximación lineal:

2

π

θo − θi −

2

π

cos(θ o − θ i ) ≅ 0 − 1 ⋅ θ o − θ i − − 0 ⋅

+ ...

2

2

π π

cos(θ o − θ i ) ≅ − θ o − θ i − = − (θ o − θ i )

2 2

Entonces, la salida del comparador de fases será, considerando la igualdad en la

expresión en lugar de la aproximación:

π

v f = K D ⋅ − (θ o − θ i )

2

con

KD ≡

KV1V 2

2

(4)

El funcionamiento lineal es fundamental para que el PLL opere en situación de

enganche. La frecuencia de salida del VCO se expresa, en situación de sintonía, como

π

wo = w FR + K o × v f = w FR + K o × K D ⋅ − (θ o − θ i )

1424

3 2

K

(5)

V

donde se observa que cuando la tensión de salida del filtro es cero, entonces oscila a la

pulsación de oscilación libre.

9

Instrumentación Electrónica. Juan José González de la Rosa

En estado de sintonía, la tensión de salida del filtro, vf, varía sólo en función de la

diferencia de desfases entre la entrada y la salida. Los límites de la pulsación de salida

vienen impuestos por los valores extremos del cos(θ0-θi).

6.3 Montaje experimental

La figura 8 muestra un montaje experimental con el PLL digital 565.

+7 V

C2

R1

C3

8

vi

10

2

741

+

vf

7

565

3

9

6

1

C1

4

ref

5

vo

-7 V

Fig. 8. Montaje experimental. R1=10 kΩ; C1=0,01 µF,

C2=10 µF, C3=0,1 nF.

La figura 9 muestra las señales de entrada y de salida fuera de sintonía. La frecuencia de

oscilación libre es de 3,2845 kHz y la entrada es de 5 kHz.

Fig. 9. Señales de entrada y de salida de un PLL

fuera de enganche. Entrada de 1Vpp y Vm=0.

10

5 Generadores y Sinterizadotes de Señales

7 Sintetizadores de frecuencia

Este apartado centra su atención en los sintetizadores indirectos de frecuencia.

7.1 Concepto

Un instrumento sintetizador de frecuencias ofrece una frecuencia múltiplo de una

referencia interna, que es la que determina la resolución y exactitud del instrumento;

como por ejemplo un oscilador de cuarzo. En consecuencia, la frecuencia del patrón

debe ser muy estable2.

En principio, la frecuencia de salida puede expresarse mediante una relación de

proporcionalidad simple, siendo el factor de proporcionalidad un número racional:

fo =

A

⋅ f REF

B

(6)

Como la salida deriva de una frecuencia estable, ésta también lo es, y se logra una

frecuencia estable y precisa. Se consigue un amplio margen de variabilidad, desde 10-6

Hz hasta 1012 Hz; la mejor estabilidad puede ser de 10-10 seg./24 horas.

7.2 Tipos

Se clasifican según el método de generación:

• Sintetizadores directos: Realizan operaciones matemáticas sobre la frecuencia de

referencia para obtener la salida. Este procedimiento es caro y sólo se usa en

instrumentos de propósito específico.

• Sintetizadores digitales: En ellos se muestrea la señal deseada, y un CDA y un

filtro obtienen la salida. Se emplea en instrumentos de bajo coste (pequeño

ancho de banda).

• Sintetizadores indirectos: Emplean un PLL para sintonizar un VCO (puede ser

su VCO interno) con una frecuencia deducida de la de referencia. Es el método

más común.

2

Una frecuencia se considera estable cuando apenas varía al cabo del tiempo. Una frecuencia puede ser

estable y poco precisa; en este caso el offset de frecuencia debe eliminarse, ajustándose el oscilador.

11

Instrumentación Electrónica. Juan José González de la Rosa

7.3 Sintetizadores indirectos

La figura 10 muestra el diagrama de un sintetizador de frecuencias en el que se divide la

frecuencia de salida del VCO.

PLL

1

Filtro

PB

Detector

fase

1/10Z

1

Amplifica

-dor

VCO

1/10X

fo

fREF=1

MHz

1

1/10Y

Fig. 10. Diagrama de bloques de un sintetizador de frecuencias. Las flechas acentuadas

indican acceso desde el panel frontal del instrumento.

El PLL recibe como entradas la frecuencia variable (dividida) de un oscilador y la señal

de salida del VCO (interno) realimentada.

Con el fin analizar el circuito se supone la situación de sintonía del PLL, es decir, se

supone que las frecuencias de entrada y de salida coinciden, manteniéndose en

consecuencia un desfase constante entre ambas señales.

f REF

10

Z

=

f VCO

10 Y

(7)

La frecuencia de salida es la del VCO dividida:

fo =

f VCO

10 X

(8)

Combinando las expresiones (7) y (8) se obtiene la frecuencia de salida en función de la

frecuencia de referencia interna:

fo =

f VCO

10 X

=

1

10 X

⋅

10 Y

10 Y

⋅

f

=

⋅ f REF

REF

Z

X +Z

10

14243 10

fVCO

12

(9)

5 Generadores y Sinterizadotes de Señales

Ejemplo 2. Utilizando la ecuación (8) deducir el rango de variación de la frecuencia de salida de un

sintetizador de frecuencias que responde al esquema de la figura 9; siendo sus parámetros: Z=4,

Y[4,5], X[0,7], fREF=1 MHz.

fo =

10Y

10 X + 4

⋅ 1 (MHz )

Los casos extremos se obtienen realizando las combinaciones adecuadas de

exponentes:

f o,máx =

f o,mín =

10 5

10 0+ 4

10 4

10 7 + 4

⋅ 1 (MHz ) = 10 (MHz )

⋅ 1 (MHz ) = 0,1 (Hz )

Por tanto, este sintetizador posee un rango que abarca desde 0,1 (Hz) hasta 10 (MHz).

La expresión (8) indica que la frecuencia de salida del instrumento se obtiene a partir de

múltiplos (factor 10Y) de la frecuencia mínima apreciable, o resolución del sintetizador:

f REF

10 X + Z

Esto significa que el divisor de frecuencias que actúa sobre la salida del VCO aumenta la

resolución de la síntesis. Este bloque permite aumentar la resolución sin disminuir el

ancho de banda del lazo.

Referencias

[1]

[2]

[3]

[4]

[5]

[6]

[7]

[8]

J.T. Humphries, Electrónica Industrial. Dispositivos, Máquinas y Sistemas de

Potencia Industrial. Ed. Paraninfo. Madrid.

N.R. Malik, Electronic Circuit: Analysis, Simulation and Design. Prentice Hall

International Editions, 1995.

T.B. Mills, The Phase Locked Loop as a Communication System Building Block.

Application Note 46. National Semiconductor, 1971.

W.D. Cooper and A.D. Helfrick, Instrumentación electrónica moderna y técnicas

de medición, Prentice-Hall. Hispanoamericana, 1991.

S. Wolf y R.FM. Smith, Guía para Mediciones Electrónicas y Prácticas de

Laboratorio. Edición ampliada y actualizada. Prentice-Hall Hispanoamericana.

México, 1992.

National Semiconductor. LM565/LM565C Data Sheet, 1999.

E. Mandado, P. Mariño y A. Lago, Instrumentación Electrónica. Marcombo.

Boixareu editores, 1995.

R. Pallás, Instrumentación Electrónica Básica, Marcombo, Boixareu editores, 1987.

13