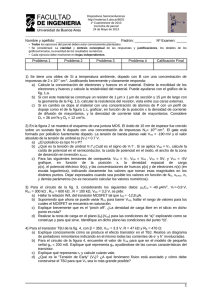

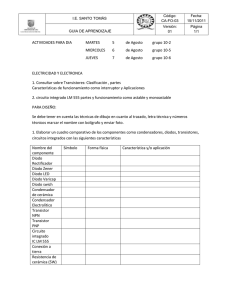

Tema 4: Dispositivos semiconductores

Anuncio