Oficio Elegante - Departamento de Informática

Anuncio

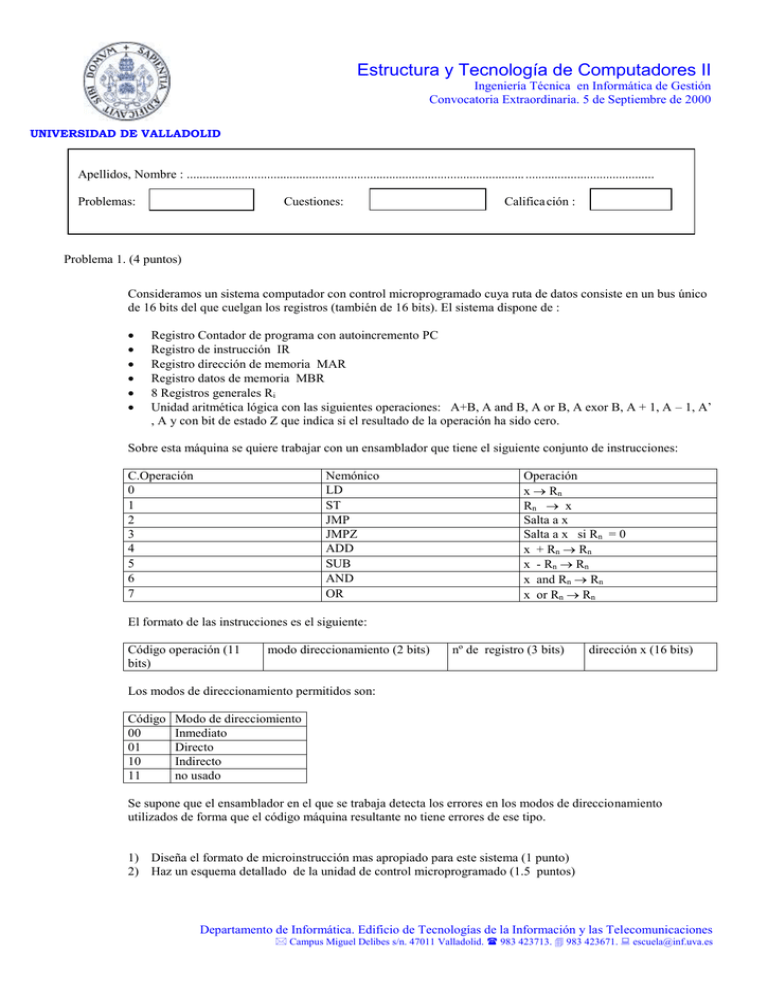

Estructura y Tecnología de Computadores II Ingeniería Técnica en Informática de Gestión Convocatoria Extraordinaria. 5 de Septiembre de 2000 UNIVERSIDAD DE VALLADOLID Apellidos, Nombre : ......................................................................................................... ........................................ Problemas: Cuestiones: Califica ción : Problema 1. (4 puntos) Consideramos un sistema computador con control microprogramado cuya ruta de datos consiste en un bus único de 16 bits del que cuelgan los registros (también de 16 bits). El sistema dispone de : Registro Contador de programa con autoincremento PC Registro de instrucción IR Registro dirección de memoria MAR Registro datos de memoria MBR 8 Registros generales Ri Unidad aritmética lógica con las siguientes operaciones: A+B, A and B, A or B, A exor B, A + 1, A – 1, A’ , A y con bit de estado Z que indica si el resultado de la operación ha sido cero. Sobre esta máquina se quiere trabajar con un ensamblador que tiene el siguiente conjunto de instrucciones: C.Operación 0 1 2 3 4 5 6 7 Nemónico LD ST JMP JMPZ ADD SUB AND OR Operación x Rn Rn x Salta a x Salta a x si Rn = 0 x + Rn Rn x - Rn Rn x and Rn Rn x or Rn Rn El formato de las instrucciones es el siguiente: Código operación (11 bits) modo direccionamiento (2 bits) nº de registro (3 bits) dirección x (16 bits) Los modos de direccionamiento permitidos son: Código 00 01 10 11 Modo de direcciomiento Inmediato Directo Indirecto no usado Se supone que el ensamblador en el que se trabaja detecta los errores en los modos de direccionamiento utilizados de forma que el código máquina resultante no tiene errores de ese tipo. 1) Diseña el formato de microinstrucción mas apropiado para este sistema (1 punto) 2) Haz un esquema detallado de la unidad de control microprogramado (1.5 puntos) Departamento de Informática. Edificio de Tecnologías de la Información y las Telecomunicaciones Campus Miguel Delibes s/n. 47011 Valladolid. 983 423713. 983 423671. escuela@inf.uva.es Estructura y Tecnología de Computadores II Ingeniería Técnica en Informática de Gestión Convocatoria Extraordinaria. 5 de Septiembre de 2000 UNIVERSIDAD DE VALLADOLID 3) Detalla las microinstrucciones necesarias para la lectura y ejecución de la instrucción LD con los distintos modos de direccionamiento. (1.5 puntos) Problema 2. (3 puntos) Consideramos un sistema con memoria principal de 1 Mbyte y memoria caché con 32 bloques agrupados en 8 conjuntos. Cada bloque tiene una capacidad de almacenamiento de 256 bytes. 1. Para las distintas funciones de mapa posibles indicar razonadamente los campos en que se divide la dirección y el tamaño de los mismos. (1 punto) 2. Suponiendo que la función de mapa utilizada es correspondiencia asociativa por conjuntos y que inicialmente la caché está vacía se ejecuta un programa que accede a las siguientes direcciones: 0xE3901, 0x24115, 0x01124, 0x00144, 0xE39FE, 0xFF9FF a. Si el algoritmo de reemplazo es FIFO indicar la evolución de la caché (1 punto) b. Repetir el apartado anterior suponiendo que el algoritmo usado es LRU (1 punto) Cuestión 1. (1 punto) Describir los fundamentos del sumador con cálculo anticipado de acarreo Cuestión 2. (1 punto) Aplica el algoritmo de división sin restauración a la división de 37 entre 4, indicando detalladamente los pasos intermedios. Cuestión 3. (1 punto) En el segmento de datos de un programa en ensamblador tenemos la siguiente definición: radio dd 12.25 Suponiendo que el formato utilizado es el IEEE 754, ¿cuál será el contenido de los 32 bits de memoria correspondientes a esa variable? Departamento de Informática. Edificio de Tecnologías de la Información y las Telecomunicaciones Campus Miguel Delibes s/n. 47011 Valladolid. 983 423713. 983 423671. escuela@inf.uva.es