TEMA 11

Anuncio

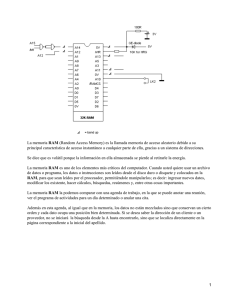

TEMA 11 MEMORIAS. CIRCUITOS LÓGICOS PROGRAMABLES 1 CLASIFICACIÓN SEGÚN SU TECNOLOGÍA 2 PARAMETROS FUNDAMENTALES DE LAS MEMORIAS •Modo de acceso: –Aleatorio (RAM, Random Access Memory) –Serie •Alterabilidad –Memorias ROM (Read Only Memory) Memorias de "solo lectura" Almacenamiento permanente de datos y programas Tipos: ROM, PROM, EPROM, EEPROM. –Memorias RWM (Read-Write Memory) Memorias de lectura y escritura Almacenamiento no permanente de programas y datos Memorias SRAM, DRAM, FLASH 3 PARAMETROS FUNDAMENTALES DE LAS MEMORIAS •Estabilidad – Volatilidad – No: ROM, PROM, EPROM, EEPROM, FLASH – Si: SRAM, DRAM. – Almacenamiento Estático/Dinámico •Tiempo de acceso (tA). •Tiempo de ciclo (tc) . Ancho de banda de las memorias •Capacidad y organización: Nº de palabras x bits por palabra. •Medio físico de almacenamiento –Electrónico –Magnético –Óptico •Consumo •Coste. 4 ESTRUCTURA GENERAL DE UNA MEMORIA RAM. ORGANIZACIONES 2D Y 3D. Configuración de la memoria RAM como circuito integrado BUS DE DIRECC. n líneas BUS DE DATOS m líneas MEMORIA CS: chip select R/W’: Lectura/escritura’ OE: output enable BUS DE CONTROL 5 ESTRUCTURA GENERAL DE UNA MEMORIA RAM. ORGANIZACIONES 2D Y 3D. Configuración de la memoria RAM como circuito integrado BUS DE DIRECC. n líneas MEMORIA BUS DE DATOS m líneas Nº de palabras: 2n Organización 2n x m bits Bits por palabra: m Ejemplo: n=11, m=8 Organización 211 x 8=2k x8 Capacidad 16 Kbits= 16384 bits 6 ESTRUCTURA GENERAL DE UNA MEMORIA RAM. ORGANIZACIONES 2D Y 3D. Funcionamiento genérico de una memoria RAM en una operación de lectura o escritura BUS DE CONTROL CS CPU + CONTROL LEC/ESCR MEMORIA CS LEC/ESCR MEMORIA BUS DE DIRECCIONES BUS DE DATOS 7 ESTRUCTURA GENERAL DE UNA MEMORIA RAM. ORGANIZACIONES 2D Y 3D. Organización 2-D, dos dimensiones i Diw-1 ………………………..Di0 i Diw-1 ………………………..Di0 Para el caso de una memoria de 16KB sería preciso un decodificador con 14 líneas de entrada y 214 líneas de salida. 8 ESTRUCTURA GENERAL DE UNA MEMORIA RAM. ORGANIZACIONES 2D Y 3D. a) Estructura lógica de la celda binaria para una memoria RAM estática con organización 2-D. b) Diagrama de bloques de la celda R Q´ S Q 9 ESTRUCTURA GENERAL DE UNA MEMORIA RAM. ORGANIZACIONES 2D Y 3D. Organización 3-D, tres dimensiones Columna Fila Al utilizar decodificación doble y selección por coincidencia de líneas activadas, para el caso de 16 KB, son precisos dos decodificadores de 7x128 . En el caso general de una memoria de N palabras, el número de líneas de selección pasan de N con un decodificador, a 2√N o N1+N2 (tales que N1xN2=N) con dos decodificadores. 10 ESTRUCTURA GENERAL DE UNA MEMORIA RAM. ORGANIZACIONES 2D Y 3D. Estructura lógica de la celda binaria para una memoria RAM estática con organización 3-D 11 Estructura lógica completa de una memoria RAM estática 16x4. Se utiliza como celda binaria el diseño anterior (2-D). 12 Las líneas de acceso al c.i. son: - Bus de direcciones A3:A0. - Bus de datos I/O3:I/O0. Se trata de cuatro líneas bidireccionales que pueden actuar como entradas o salidas, excluyentemente, gracias a los buffers triestado. - Señales de control de lectura/escritura (L/E') y habilitación global del chip (CS', chip select). - Señal de control de habilitación de salida OE' (Output Enable). 13 SEÑALES DE CONTROL. CICLOS DE LECTURA Y ESCRITURA Matriz de memoria 8 bi ts 512 filas C.I. RAM estática de 32K x 8 A8 A7 A6 A5 A4 A3 A2 A1 A0 512 X 64 ARRAY 64 columnas A14 A13 A12 A11 A10 A9 14 SEÑALES DE CONTROL. CICLOS DE LECTURA Y ESCRITURA CE=VIL; OE=VIL; WE=VIH 15 SEÑALES DE CONTROL. CICLOS DE LECTURA Y ESCRITURA 16 ESTRUCTURA INTERNA DE UNA MEMORIA RAM DINÁMICA Organización interna de un c.i. de memoria dinámica (DRAM) de 1Mx1 bits Bus de direcciones multiplexado A0/A10 A1/A11 A2/A12 . . A9/A19 Dout Din 17 SEÑALES DE CONTROL. CICLOS DE LECTURA Y ESCRITURA Ciclo de lectura Ciclo de escritura 18 SEÑALES DE CONTROL. CICLOS DE LECTURA Y ESCRITURA Cronograma del modo página rápido para la operación de lectura 19 MEMORIAS RAM DE SOLO LECTURA (ROM) CLASIFICACION - Memorias ROM (Read Only Memory): El contenido se establece en el proceso de fabricación. - Memorias PROM (Programable ROM): Son memorias ROM programables en un equipo especializado. El contenido es inalterable desde el momento de la programación. - Memorias RPROM (Reprogramable ROM): Es posible reprogramarlas borrando el contenido previamente. Según la forma de realizar el borrado, se contempla una subclasificación adicional: - Memorias EPROM (Erasable PROM): La grabación se realiza en equipos especiales. El borrado se realiza mediante la exposición del integrado a radiación ultravioleta. - Memorias EEPROM o E2PROM (Electrically EPROM): Programables y borrables eléctricamente. Esto las dota de una gran versatilidad, puesto que tanto la programación, modificación y borrado puede realizarse ON LINE. Presentan la ventaja de ser borrables byte a byte. 20 MEMORIAS RAM DE SOLO LECTURA (ROM) Algunas APLICACIONES usuales de las ROM son la implementación de: - Conversores de código - Generadores de caracteres - Func. aritméticas complejas (trigonométricas, logarítmicas, etc.) - Secuenciales de propósito general - Unidades de control microprogramadas - Almacenamiento de partes del sistema operativo. COMPARACIÓN con las memorias RAM de lectura/escritura. - La circuiteria de direccionamiento es igual (uso de decodificadores) - El bloque de E/S se simplifica (sólo buffers de salida). - Las líneas de control quedan reducidas a CS (Chip Select). - Son no volátiles. 21 CELDAS BINARIAS: ELEMENTOS ACOPLADORES a) Memorias ROM. 22 b) Memorias PROM (similar en las RPROM). 23 24 Características de la EPROM 2716 (a) Diagrama temporal de lectura 25 Características de la EPROM 2716 (b) Programación de la EPROM 2716 26 EXTENSIÓN DE LA LONGITUD DE PALABRA 27 EXTENSIÓN DEL NÚMERO DE PALABRAS 28 EJEMPLOS DE EXTENSION DE MEMORIAS RAM RAM de 4096x2 bits construida con 8 RAM 2102 (1 Kbit). 29 EJEMPLOS DE EXTENSION DE MEMORIAS RAM RAM de 1 Kbyte construida con 8 RAM 2111 de 1 Kbit (256x4). 30 31 Circuito de direccionamiento para una RAM de 8 Kbytes construida con 64 RAM 2111 de 1 Kbit (256x4). 32 EJEMPLO DE UN SISTEMA DE MEMORIAS EN UN MICROCOMPUTADOR REAL 33 34 DISEÑO DE CIRCUITOS CON MEMORIAS Y CIRCUITOS LÓGICOS PROGRAMABLES (PLD) 35 DISEÑO DE CIRCUITOS CON MEMORIAS Y CIRCUITOS LÓGICOS PROGRAMABLES (PLD) VENTAJAS: Reemplazan a varios componentes discretos Reducción de CI’s Reducción de espacio, conexiones, consumo ... Reducción de coste Aumento de fiabilidad Posibilidad de ser reprogramados Versatilidad de los diseños que se pueden adaptar a nuevas especificaciones. Posibilidad de corregir errores de diseño Utilización de herramientas EDA (Electronic Desing Automation) en el diseño Lenguajes de descripción de Hw (HDL), ejem: VHDL. Simulación... Gran variedad de dispositivos con diversas tecnologías, arquitecturas y niveles de complejidad. Capacidades equivalentes desde varias decenas a varios millones de puertas. 36 Memorias PROM y PLD A B C D Matriz decodificadora (programable) PROM (16x4): Salidas Productos Matriz codificadora (fija) a b c d 37 Memorias PROM y PLD A B C D Matriz decodificadora (programable) FPLA (4x16x4): (Field Programmable Logic Array) Salidas Productos Entradas Matriz codificadora (programable) a b c d 38 Memorias PROM y PLD A B C D Matriz decodificadora (fija) PAL (4x16x4): (Programmable Array Logic) Salidas Productos Entradas Matriz codificadora (programable) a b c d 39 Ejemplo de utilización de diferentes arquitecturas: 40 Ejemplo de utilización de diferentes arquitecturas: 41 Utilizando una PROM 16x4: A B C D a b c d 42 Utilizando un FPLA Simplificando: a=A; b=A’B+AB’ c=B’C+BC’; d=C’D+CD’ Resultado 7 productos, FPLA=4x7x4 A B C D A D’C AB’ BC’ A’B B’C DC’ a b c d 43 Utilizando un PAL Simplificando: a=A; b=A’B+AB’ c=B’C+BC’; d=C’D+CD’ Resultado 7 productos, PAL=4x8x4 A B C D A 0 A’B AB’ B’C BC’ C’D CD’ a b c d 44 3 + 3 = 6 45 46 47 PROBLEMAS DE MEMORIAS 48 49 50 51 52 53 54