Diapositivas Tema 04

Anuncio

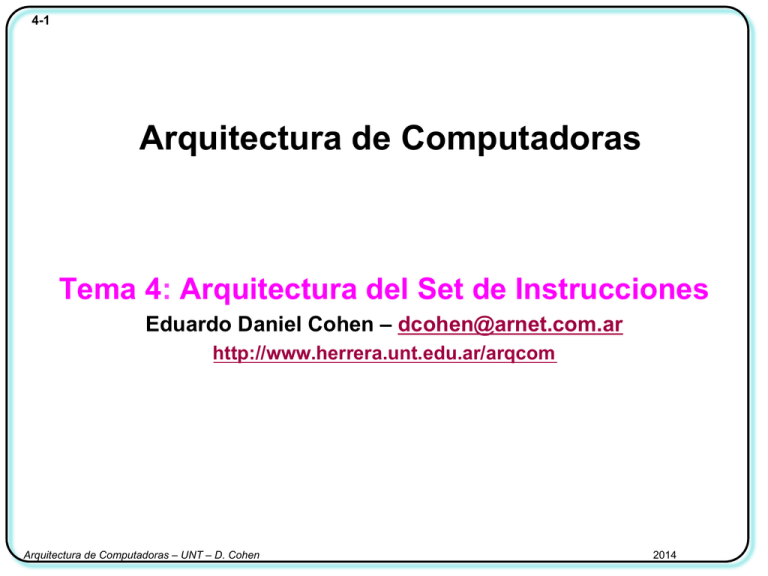

4-1 Arquitectura de Computadoras Tema 4: Arquitectura del Set de Instrucciones Eduardo Daniel Cohen – dcohen@arnet.com.ar http://www.herrera.unt.edu.ar/arqcom Arquitectura de Computadoras – UNT – D. Cohen 2014 4-2 Arquitectura del Set de Instrucciones Indice 1. 2. 3. 4. 5. 6. Repaso. Distintos Conjuntos de Instrucciones. Modos de Direccionamiento y Lenguajes de Alto Nivel (HLL). Stacks Subrutinas. Marcos de Enlace. Arquitectura de Computadoras – UNT – D. Cohen 2014 4-3 El Ciclo de la Instrucción Instruction Fetch Obtener instrucción de Memoria M(PC), guardar Instrucción en IR Actualizar PC Instruction Decode Execute Arquitectura de Computadoras – UNT – D. Cohen Determinar las acciones que se requieran Ejecutar las acciones requeridas (leer o escribir en M o I/O, procesar en ALU...) 2014 4-4 ¿Qué debe especificar una instrucción? Flujo de Datos ¿Qué operación realizar? add r0, r1, r3 • Op code: add, load, branch, etc. ¿Dónde están los operando/s? add r0, r1, r3 • En registros del CPU, celdas de memoria, lugares de I/O o parte de una instrucción. ¿Dónde se guarda el resultado? add r0, r1, r3 • En un registro, M o I/O. ¿Dónde está la próxima instrucción? • En el lugar de memoria a que apunta el PC • Para ej. salto – PC endloop Arquitectura de Computadoras – UNT – D. Cohen add r0, r1, r3 br endloop 2014 4-5 Formato de la Instrucción Op-Code Operando 1 Operando 2 ... Operando n 1. Op-Code: Qué Operación se efectúa. • n bits – hasta 2n operaciones distintas. 2. Operandos: Con qué datos se opera. 3. • En general desde 0 a 3 operandos. • El dato puede estar en el campo, en Memoria o en un Registro. Puede haber más de un formato, dependiendo de Op-Code. Arquitectura de Computadoras – UNT – D. Cohen 2014 4-6 3 Clases de Instrucciones Movimiento de Datos • Mover datos desde M(i) o R(i) a M(j) o R(j) sin modificarlos. Tienen siempre una fuente y un destino. • Load— La fuente es memoria y el destino un registro. • Store— La fuente es un registro y el destino es memoria. • Hay casos con fuentes y destino ambos M o ambos R. Procesamiento – Instrucciones Aritméticas y Lógicas. • Procesar uno o más operandos fuentes y guardar el resultado en un lugar de destino. • Add, Sub, Shift, etc. Control de flujo de Instrucciones (Saltos) • Alterar el flujo normal de control en lugar de ejecutar la siguiente instrucción de la dirección contigua. • Br Loc, Brz Loc2,—saltos condicionales o incondicionales. Arquitectura de Computadoras – UNT – D. Cohen 2014 4-7 ¿Cuáles son las componentes de un ISA? Conocido como el Modelo del Programador de la máquina. Celdas de Almacenamiento • Registros de propósito general y especial en el CPU. • Muchas celdas de propósito general de igual tamaño en Memoria. • Almacenamiento relacionado con dispositivos I/O. Formato de la Instrucción • Tamaño y significado de los diferentes campos de la Instrucción. El Set de Instrucciones de la Máquina. • Es el repertorio completo de las operaciones de la máquina. • Emplea celdas de almacenamiento, formatos y resultados del ciclo de la Instrucción. Naturaleza del ciclo de la Instrucción. • Cosas que se hndependientemente de la instrucción en cuestión. Arquitectura de Computadoras – UNT – D. Cohen 2014 4-8 Los Registros del CPU pueden tener una “personalidad” Acumulador, Puntero de Pila, Contadores, Fuente, Destino. Las diferentes arquitecturas se clasifican generalmente en cómo y dónde se ubican los operandos y resultados y cómo se especifican por la instrucción. Pueden estar en Registros del CPU o en Memoria. Stack Registro Implícito General Purpose Registers Push Pop Top Second • • • Stack Machine Arquitectura de Computadoras – UNT – D. Cohen A • • • Accumulator Machine General Register M a c h i ne 2014 4-9 ISAs de 3, 2, 1 y 0 direcciones La clasificación se basa en las instrucciones aritméticas que tienen dos operandos y un resultado. Un ISA de 3 direcciones usa modos de direccionamiento tanto para los operandos como para el resultado R ← Op1 op Op2 Una instrucción de 2 direcciones usa el operando destino (resultado) como operando fuente también Op1 ← Op1 op Op2 Una instrucción de 1 dirección emplea un registro implícito, llamado acumulador, para que contenga tanto un operando como el resultado Acc ← Acc op Op1 Una de 0-dirección emplea una pila para contener los dos operandos y el resultado TOS ← TOS op SOS (TOS es Top Of Stack, SOS es Second On Stack) La instrucción de 4 direcciones, prácticamente no se ve actualmente, permite que la dirección de la próxima instrucción se especifique explícitamente. Arquitectura de Computadoras – UNT – D. Cohen 2014 4-10 Modos de Direccionamiento Un modo de direccionamiento es el soporte de Hw para una forma útil de determinar dónde se encuentra el operando. Modos de direccionamiento diferentes resuelven distintos problemas de los Lenguajes de Alto Nivel (HLL). • Algunas direcciones se conocen en tiempo de compilación, ej. Variables globales. • Otras no se conocen hasta el tiempo de corrida, ej. Punteros. • Puede ser necesario calcular las direcciones. Por ejemplo: • Componentes de la estructura de un record (registro): • Variable de base (dirección completa) + constante (pequeña) • Componentes de una tabla o vector: • Constante de Base (dirección completa) + variable índice (pequeña) • Es posible guardar valores constantes sin usar otras celdas de memoria, en la misma instrucción o adyacente a ella. • Un buen programa no se cambia a sí mismo. Arquitectura de Computadoras – UNT – D. Cohen 2014 4-11 HLL Ejemplos de Direcciones Estructuradas Lenguaje C: rec → count • rec es un puntero a un record: variable de dirección completa • count es el nombre de un campo: un offset fijo en bytes, digamos 2 Lenguaje C: v[i] • v es la dirección fija de la tabla: dirección completa fija (constante). • i es el nombre del índice variable: no supera a la dimensión de la tabla. Las variables deben estar en registros o en Memoria. Pequeñas constantes pueden estar contenidas en la instrucción. Conclusión: se necesita “aritmética de direcciones.” • Ej., Dirección de Rec → Count es la dirección de Rec + offset de count. Arquitectura de Computadoras – UNT – D. Cohen Count Rec → V[i] V → 2014 4-12 Implementación Stack Se implementa en memoria. Arquitecturas con Stack Explícito: • Registro especial, Stack Pointer (SP), en CPU. • Instrucciones Dedicadas: PUSH y POP. Excepción: guarda estado de la tarea en stack. Excepciones: Traps + Interrupciones. Arquitectura de Computadoras – UNT – D. Cohen 2014 4-13 Arquitecturas sin Stack Explícitos Necesitan convocar a Subrutinas. Instrucciónes JAL r y J r. (para CALL y RETURN). • JAL r, guarda PC en registro r. • J r, salta a la dirección dada por r. El stack se implementa mediante: • Un registro general (GPR) – standard fijo. • Movimiento de datos e incrementos o decrementos. ¿Soporta llamadas anidadas? ¿Y recursivas? Arquitectura de Computadoras – UNT – D. Cohen 2014 4-14 Implementación de Rutinas Arquitecturas con Stack con Instrucciones Específicas. Call – guarda PC en stack (transparente). • Algunas arquitecturas guardan CCR también (Call). • Hay que asegurarse de guardar el estado. • ¿qué es el “estado”? • • • • Los argumentos los guarda quien convoca. Registros con Variables locales, los guarda el convocado. Esta es una convención posible. Se trabaja con standards. ¿Por qué? Return. • Restaurar estado y volver. • El convocado restaura lo que guardó (mediante POPs). • Restaura PC, mediante instrucción RETURN. • El convocante restaura lo que guardó (también con POPs) Muy limitado usar solo POP y PUSH para direccionar Stack. ¿Qué pasa si la rutina cambia el valor de SP antes de retornar? Arquitectura de Computadoras – UNT – D. Cohen 2014 4-15 Enlaces Standard (gcc): Marcos (Frames) Se emplea un puntero de marco, “Frame Pointer” Argumentos (guarda quien llama) Registros Guardados por El Convocado (old FP, RA) Memoria Alta Argumentos y variables locales, a una distancia (offset positivo) fijo de FP Variables Locales FP SP Crece y decrece durante evaluación de expresiones y procesamiento Rutina. Memoria Baja En este ejemplo el stack crece hacia abajo, caso MIPS. Arquitectura de Computadoras – UNT – D. Cohen 2014 4-16 Resumen Todas las máquinas tienen 3 clases de instrucciones. Arquitecturas de 3, 2, 1 o 0 direcciones. Modos de direccionamiento para manejar estructuras de datos en forma eficiente • Aritmética de direcciones. Variados modos de direccionamiento, sintaxis y semántica en la industria. Stacks permiten subrutinas, y rutinas para excepciones… • Explícitos o implícitos. • Standards para pasaje de parámetros. Máquinas con GPRs o con registros “con personalidad” Arquitectura de Computadoras – UNT – D. Cohen 2014