tema 10. circuitos secuenciales - OCW Usal

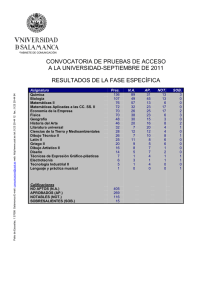

Anuncio

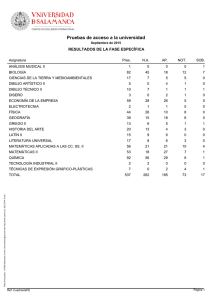

TEMA 10. CIRCUITOS SECUENCIALES http://www.tech-faq.com/wp-content/uploads/images/integrated-circuit-layout.jpg IEEE 125 Aniversary: http://www.flickr.com/photos/ieee125/with/2809342254/ Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 1 TEMA 10. CIRCUITOS SECUENCIALES - Introducción - Elementos de memoria : biestables, latches - Registros de desplazamiento estáticos - Circuitos secuenciales síncronos - Circuitos secuenciales asíncronos Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 2 TEMA 10. CIRCUITOS SECUENCIALES INTRODUCCIÓN Sistemas combinacionales: la salida depende solamente de lo que haya en las entradas en ese instante Sistemas secuenciales: La salida depende de los valores de las entradas en ese instante y también de los valores que tuvieron en los instantes anteriores Circuitos que “recuerdan” o tienen memoria de las situaciones de interés por las que ha pasado el sistema a las situaciones se denominan estados Variables de estado: en cada caso concreto definen los estados a recordar Ejemplo: Circuito de una única entrada y una única salida y que proporciona salida 1 cuando aparece en la entrada dos “1” consecutivos Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 3 TEMA 10. CIRCUITOS SECUENCIALES INTRODUCCIÓN La forma de operar de un sistema secuencial Operación secuencial del sistema: dado un estado y una entrada el sistema produce una salida y el estado siguiente Estado anterior Entrada xni Salida zni Estado siguiente +1 D. Pardo, et al. 2006 Se describe mediante un diagrama de estados (Secuencia de grafos) por los que pasa el circuito como consecuencia de las sucesivas entradas y las salidas que produce Ejemplos: ASCENSOR BOLIGRAFO ENTRADAS SALIDAS ESTADOS INTERNOS entre dos pisos Pulsar No Pulsar Llamada desde el bajo Llamada desde el primero Sale Punta Entra Punta No Se Mueve Punta. Motor en marcha: Sube o baja Motor parado Punta Dentro Punta Fuera. Ascensor piso bajo Ascensor piso 1º Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 4 TEMA 10. CIRCUITOS SECUENCIALES INTRODUCCIÓN Hablamos de estado siguiente y anterior: Secuencia temporal Clasificación de sistemas secuenciales: definición de secuencia Sistemas síncronos: Sólo se observa el sistema durante el pulso de reloj marcapasos El reloj establece cuando se modifica el estado (no la salida: sistemas Mealy). Sistemas asíncronos: El sistema es permanentemente activo Un cambio en alguna de las entradas del sistema: induce un transitorio que evoluciona hasta el siguiente estado Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 5 TEMA 10. CIRCUITOS SECUENCIALES ESTRUCTURA GENERAL DE UN SISTEMA SECUENCIAL SÍNCRONO Variables de entrada xi Variables de estado yi Sistema Combinacional Reloj Memoria Variables de salida zi Variables de excitación Yi D. Pardo, et al. 2006 Dos bloques básicos: en coincidencia con el pulso de reloj • Un bloque combinacional que : Lee las variables de entrada y de estado. Genera las funciones booleanas de salida y de excitación. • Un bloque de memoria que: “recuerda” la evolución del sistema configura el estado anterior • El nuevo estado se generará y será leído con el nuevo pulso de reloj Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 6 TEMA 10. CIRCUITOS SECUENCIALES ELEMENTOS DE MEMORIA: FLIP-FLOP o BIESTABLE BIESTABLE: circuito secuencial que se caracteriza por: Tener dos estados estables: almacena permanentemente un bit “0” y “1”: Estado: contenido de la memoria Se mantiene indefinidamente en uno de los estados posibles Reloj Variables de estado yi Variables de excitación Memoria Yi D. Pardo, et al. 2006 Entradas o señales externas de excitación hacen que el BIESTABLE cambie de estado. NOTA: La funció función de excitació excitación es caracterí característica de cada tipo de biestable (D, T, RS o JK). JK). Tienen dos salidas: Q y Q : son las variables de estado (definen los estados internos) Las salidas dependen de las entradas (vars de excitación) y del estado anterior Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 7 TEMA 10. CIRCUITOS SECUENCIALES ELEMENTOS DE MEMORIA Flip-flop RS (implementación NOR) Q = R Q' Q' = S Q Q’ http://www.profesormolina.com.ar/electronica/componentes/int/biest.htm • Una de las dos entradas a “0”, salidas complementarias. • Una entrada a “1” determina el valor de la salida. Tabla de estados Tabla de estados (combinacional (combinacional)) R S 0 0 0 1 1 1 0 1 Q 0 1 1 0 0 Q’ 1 0 0 1 0 se conserva el estado viola complementariedad Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 8 TEMA 10. CIRCUITOS SECUENCIALES ELEMENTOS DE MEMORIA Flip-flop RS (implementación NOR) :tabla característica transiciones entre estados Partimos de Qn=0 e introducimos R=S=0: estado de memoria Tabla característica Q’ http://www.profesormolina.com.ar/electronica/componentes/int/biest.htm Partimos de Qn=0 e introducimos R=0, S=1: SET R S Qn + 1 0 0 Qn MEM 0 1 1 1 0 1 1 0 ? SET RESET Q’ http://www.profesormolina.com.ar/electronica/componentes/int/biest.htm Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 9 TEMA 10. CIRCUITOS SECUENCIALES ELEMENTOS DE MEMORIA J Flip-flop JK K Qn Qn +1 No cambio 0 0 0 0 0 1 0 1 0 0 1 1 0 1 0 0 Reset 1 1 0 0 0 1 1 1 Set 1 1 1 1 0 1 1 0 Basculación http://www.profesormolina.com.ar/electronica/componentes/int/biest.htm Tabla de Excitación Tabla característica del flip-flop J-K Qn J K Qn+1 J K Qn + 1 0 0 × 0 0 0 Qn 0 1 × 1 0 1 0 1 × 1 0 1 0 1 1 × 0 1 1 1 Qn Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 10 TEMA 10. CIRCUITOS SECUENCIALES ELEMENTOS DE MEMORIA Flip-flop JK master-slave: flip-flop activado por flancos de la señal del reloj D. Pardo, et al. 2006 J Q K Q' Reloj Diagrama ló lógico del flipflip-flop J-K http://www.profesormolina.com.ar/electronica/componentes/int/biest.htm Bloquea el cambio en la salida hasta que no acaba el pulso de reloj. Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 11 TEMA 10. CIRCUITOS SECUENCIALES ELEMENTOS DE MEMORIA Q J Flip-flop T (K = J) T K Q CP D. Pardo, et al. 2006 Qn+1 T 0 1 Tabla de verdad Func. Func. log 0 1 Qn Qn Tabla caracterí característica Si mantenemos J=K=T=1, la salida oscila Aplicaciones: Divisor de frecuencia por 2 Contadores … Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 12 TEMA 10. CIRCUITOS SECUENCIALES ELEMENTOS DE MEMORIA Q J D Flip-flop D (D=J= K ) K Q CP J Tabla de verdad Func. Func. log K D Qn+1 0 1 0 0 1 0 1 1 D. Pardo, et al. 2006 Tabla caracterí característica La salida en el estado siguiente sigue a la entrada (útil para almacenar un único bit de datos) Aplicación: registros de desplazamiento Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 13 TEMA 10. CIRCUITOS SECUENCIALES REGISTROS DE DESPLAZAMIENTO Registro de desplazamiento con carga serie Salida de datos serie o paralelo Salidas paralelo Entrada serie D D CP Pulsos de desplazamiento Q Q Q D CP Salida serie CP D. Pardo, et al. 2006 Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 14 TEMA 10. CIRCUITOS SECUENCIALES REGISTROS DE DESPLAZAMIENTO Registro de desplazamiento con carga en paralelo y salida serie Desplaza/Carga Q2 Q1 D1 D2 CP Q0 D0 CP CP Pulsos de reloj D. Pardo, et al. 2006 Entradas en paralelo Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 15 TEMA 10. CIRCUITOS SECUENCIALES SÍNTESIS DE SISTEMAS SECUENCIALES SÍNCRONOS Analizar el enunciado con el fin de determinar el número de entradas y el de salidas Obtención del diagrama de estados Asignación secundaria: asignar un número binario a cada estado Programación de los flip-flops: obtención de las variables de excitación de los biestables para que dado un estado y unos valores de las entradas, se obtenga el estado siguiente Ecuaciones de las redes de control: por métodos puramente combinacionales y a partir de las matrices de control, se obtienen las ecuaciones correspondientes Síntesis de las redes combinacionales de control Síntesis de la red de salida Veamos un ejemplo: Diseñar un circuito secuencial síncrono que presente un valor uno en su salida cada vez que el número de unos, coincidentes con el pulso de reloj, contenidos en una secuencia de 3 bits, sea impar Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 16 TEMA 10. CIRCUITOS SECUENCIALES ANÁLISIS DE CIRCUITOS SECUENCIALES SÍNCRONOS Consiste en el proceso inverso de la síntesis Procedimiento general: Escribir las ecuaciones de excitación de los flip-flops Construir las matrices de programación a partir de las ecuaciones anteriores Construir las matrices de estado, empleando la tabla característica de los flip-flop y las matrices de programación obtenidas previamente Construir el diagrama de estados a partir de la matriz de estados y la de salida Asignación secundaria y reducción de estados, si ha lugar Trascripción literal de la operación del circuito Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 17 TEMA 10. CIRCUITOS SECUENCIALES ANÁLISIS DE CIRCUITOS SECUENCIALES SÍNCRONOS Ejemplo CP Salida, z Circuito CP C B Entrada, w z w C B B w S Q R CPQ A A A Ecuaciones de excitación Matrices de programación B B C S Q R CPQ B B Matrices de estado Matrices de salida Diagrama de estados Asignación secundaria A w B D. Pardo, et al. 2006 w S Q R CPQ C Trascripción literal C Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 18 TEMA 10. CIRCUITOS SECUENCIALES SISTEMAS SECUENCIALES ASÍNCRONOS Son aquellos que NO se encuentran pilotados por un pulso de reloj Alta velocidad de respuesta Dos tipos: Sistemas de modo de nivel: cambio en una de las entradas Sistemas de modo de pulso: doble cambio en una entrada a pulso Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 19 TEMA 10. CIRCUITOS SECUENCIALES SISTEMAS SECUENCIALES ASÍNCRONOS: Modo de PULSO Se diseñan con elementos de memoria sin reloj (latches) Variables de entrada xi Variables de estado yi Sistema Combinacional Reloj Memoria Variables de salida zi Variables de excitación Yi D. Pardo, et al. 2006 Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 20 TEMA 10. CIRCUITOS SECUENCIALES SISTEMAS SECUENCIALES ASÍNCRONOS: Modo de PULSO RESTRICCIONES • NO pulsos simultáneos en dos o más entradas (n entradas, n+1 posibles condiciones de entrada) • Transiciones de los elementos de memoria iniciadas por los pulsos de entrada • Las variables de entrada sólo se utilizan en la forma no complementada o complementada, pero no en ambas Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 21 TEMA 10. CIRCUITOS SECUENCIALES SISTEMAS SECUENCIALES ASÍNCRONOS: Modo de PULSO Veamos un ejemplo z x1 Ecuaciones de excitación x2 Matrices de programación Matrices de estado Diagrama de estados y Q S Asignación secundaria Trascripción literal D. Pardo, et al. 2006 y Q R Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 22 TEMA 10. CIRCUITOS SECUENCIALES SISTEMAS SECUENCIALES ASÍNCRONOS (Modo de PULSO): SINTESIS No existe señal de reloj El disparo del circuito se realiza con pulsos en las entradas Obtención del diagrama de estados Asignación de estados Matrices de estado Matrices de programación y de salida Ecuaciones de programación y de salida Dibujar el circuito Veamos un ejemplo: Diseñar un circuito de modo de pulso con dos líneas de entrada x1 y x2 y una línea de salida z. El circuito debe producir un pulso en la salida que coincida con el último pulso de entrada de la secuencia x1-x2-x2. Ninguna otra secuencia de entrada debe producir un pulso de salida (circuito detector de secuencia) Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 23 TEMA 10. CIRCUITOS SECUENCIALES SISTEMAS SECUENCIALES ASÍNCRONOS: Modo de NIVEL El cambio de nivel de una entrada provoca el posible cambio de la salida y el estado No son necesarios elementos de memoria Circuito combinacional realimentado Variables de entrada xi Sistema Combinacional Variables de estado ys Variables de salida zj Variables de excitación Yr Retardo ∆t D. Pardo, et al. 2006 Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 24 TEMA 10. CIRCUITOS SECUENCIALES SISTEMAS SECUENCIALES ASÍNCRONOS (Modo de NIVEL): ANALISIS Ecuaciones combinacionales Matriz de excitación x1 z Matriz de transición Matriz de flujo Matriz de salida x2 D. Pardo, et al. 2006 Descripción literal Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 25 TEMA 10. CIRCUITOS SECUENCIALES SISTEMAS SECUENCIALES ASÍNCRONOS (Modo de NIVEL): ANALISIS Ejemplo: flip-flop RS asíncrono implementación NAND x S R y 00 01 11 10 00 11 11 11 11 X = y+S 01 11 11 01 01 Y = x +R 11 11 10 00 01 10 11 10 10 11 S y x R D. Pardo, et al. 2006 XY S S x y R x 00 01 11 10 y R 01 00 11 10 00 00 1 2 3,4 5 01 01 1 2 3 5 11 11 1 2 3,4 5 10 10 1 2 4 5 Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 26 TEMA 10. CIRCUITOS SECUENCIALES SISTEMAS SECUENCIALES ASÍNCRONOS (Modo de NIVEL): SÍNTESIS Veamos un ejemplo: Dadas dos señales A y B (entradas), diseñar una red que suministre una salida z = 1 cuando ambas entradas son 1, pero sólo si, partiendo de entradas A=B=0, A fue 1 antes que B. Si la salida es 1 se mantiene hasta que B sea 0. Suponemos que las entradas no cambian a la vez Tabla de flujo primitiva Reducción de la tabla primitiva a Tabla de flujo reducida Matriz de excitación Matriz de salida Implementación Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 27 TEMA 10. Problemas de CIRCUITOS SECUENCIALES Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 28 TEMA 10. CIRCUITOS SECUENCIALES PROBLEMAS CIRC. SEC. SÍNCRONOS. PROB. 1 B A C B A J Q A K Q B CP J Q K CP Q B C J Q K Q CP D. Pardo, et al. 2006 CP Ecuaciones de excitación Matrices de programación Matrices de estado Matrices de salida Diagrama de estados Asignación secundaria Trascripción literal Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 29 TEMA 10. CIRCUITOS SECUENCIALES PROBLEMAS CIRC. SEC. SÍNCRONOS. PROB. 2 Q x D y Q CP D. Pardo, et al. 2006 A A z y x y CP J Q K CPQ B Ecuaciones de excitación Matrices de programación Matrices de estado Matrices de salida Diagrama de estados Asignación secundaria Trascripción literal Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 30 TEMA 10. CIRCUITOS SECUENCIALES PROBLEMAS CIRC. SEC. SÍNCRONOS. PROB. 3 z x J y2 x K Q CP y1 Ecuaciones de excitación Q Matrices de programación Matrices de estado Matrices de salida x J Q Diagrama de estados y2 x Asignación secundaria K CPQ y1 Trascripción literal CP D. Pardo, et al. 2006 Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 31 TEMA 10. CIRCUITOS SECUENCIALES PROBLEMAS CIRC. SEC. SÍNCRONOS. PROB. 12 0/0 AB 00 x/z CP t 1/0 x 0/0 01 0/0 A 1/0 B 0/0 10 1/0 z 11 1/1 D. Pardo, et al. 2006 Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 32 TEMA 10. CIRCUITOS SECUENCIALES PROBLEMAS CIRC. SEC. SÍNCRONOS. PROB. 13 00/ 0 ab/z 11/ 0 00/1 11/ 1 CP A 11/1 1 01/ 0 B 01/ 0 D 01/ 0 10/ 0 b Estado A 10/ 1 C 10/1 a 11/ 0 10/ 0 A B D C C C A z 00/ 1 01/ 0 00/ 0 D. Pardo, et al. 2006 Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 33 TEMA 10. CIRCUITOS SECUENCIALES PROBLEMAS CIRC. SEC. ASÍNCRONOS MODO DE NIVEL Se desea automatizar la barrera de un cruce a nivel entre una carretera y una vía férrea con una sola vía. Para ello se colocan en la vía dos conmutadores, uno a cada lado del cruce, separados por una distancia mayor que la longitud de cualquier tren y que están activados mientras está pasando el tren por ellos. Diseñar un circuito secuencial asíncrono de modo de nivel para el control de la barrera, de manera que ésta baje cuando el tren se acerca al cruce y suba cuando el tren se aleje. Entre los dos conmutadores nunca están dos trenes; es decir, nunca dos trenes circulan suficientemente juntos. Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 34 Agradecimientos Daniel Pardo Collantes, Área de Electrónica, Departamento de Física Aplicada. Universidad de Salamanca. Referencias Pardo Collantes, Daniel; Bailón Vega, Luís A., “Fundamentos de Electrónica Digital”.Universidad de Salamanca. Ediciones Universidad de Salamanca. 2006. http://www.profesormolina.com.ar/electronica/componentes/int/sist_digit/image018.jpg http://www.profesormolina.com.ar/electronica/componentes/int/biest.htm http://2.bp.blogspot.com/_Sb4aoWqhThY/S99T4vz6kI/AAAAAAAABzY/6JcgGuof_aQ/s1600/muestreo.png Raúl Rengel Estévez: raulr@usal.es María Jesús Martín Martínez : mjmm@usal.es 35