Introducción a los Sistemas de Entrada/Salida

Anuncio

Introducción a los

Sistemas de Entrada/Salida

Arquitectura de Sistemas Paralelos (1)

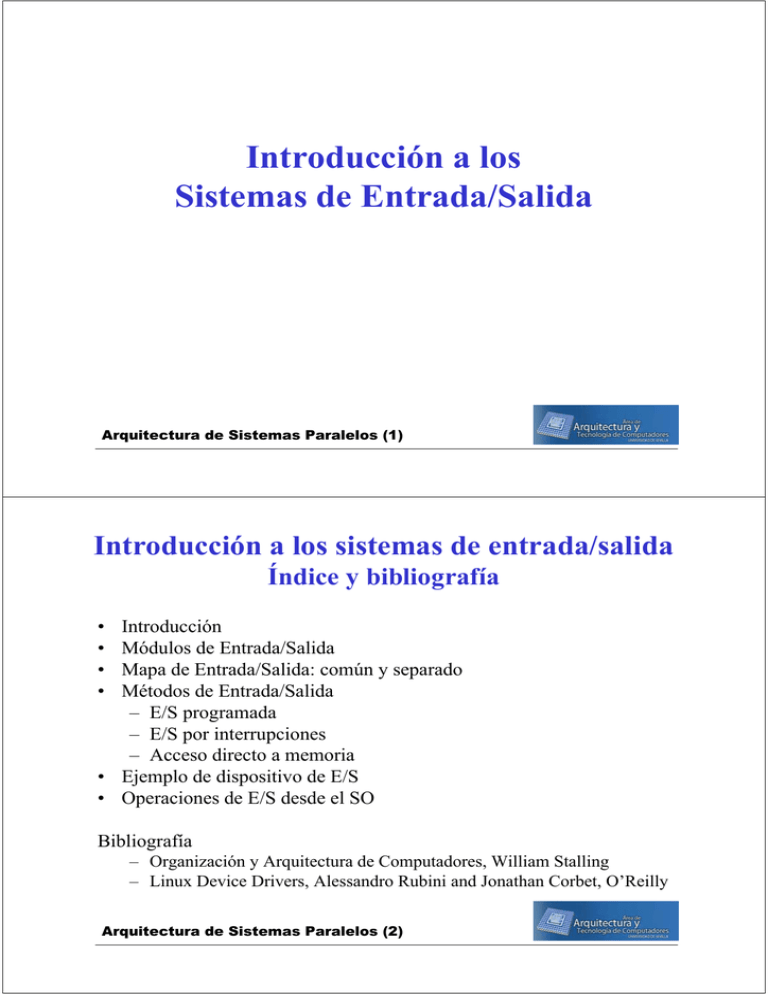

Introducción a los sistemas de entrada/salida

Índice y bibliografía

•

•

•

•

Introducción

Módulos de Entrada/Salida

Mapa de Entrada/Salida: común y separado

Métodos de Entrada/Salida

– E/S programada

– E/S por interrupciones

– Acceso directo a memoria

• Ejemplo de dispositivo de E/S

• Operaciones de E/S desde el SO

Bibliografía

– Organización y Arquitectura de Computadores, William Stalling

– Linux Device Drivers, Alessandro Rubini and Jonathan Corbet, O’Reilly

Arquitectura de Sistemas Paralelos (2)

Introducción a los sistemas de entrada/salida

Introducción (I)

• Un computador no puede estar formado sólo por la CPU y la memoria.

Para darle alguna utilidad debe de poder comunicarse con el mundo

exterior. Esto se realiza a través del subsistema de entrada/salida

(módulos de E/S)

• La misión principal del subsistema de E/S es la adaptación de los

dispositivos externos para su conexión al bus del sistema. ¿Por qué no

pueden conectarse directamente?

– A menudo, la velocidad de transmisión de datos de los periféricos es

mucho menor que la de la memoria y la CPU (es necesario amortiguar esa

diferencia de velocidades)

– Debido a la gran variedad de periféricos existentes no es posible incorporar

toda la lógica necesaria para controlar tal diversidad de dispositivos dentro

del procesador

– Los formatos y tamaños de datos de los periféricos suelen ser diferentes a

los utilizados por el computador a los que se conectan

Arquitectura de Sistemas Paralelos (3)

Entrada/Salida

Introducción (II)

• Existen dos esquemas diferentes para la

implementación del subsistema de E/S:

a) Diseñarlo a medida utilizando

componentes básicos

b) Utilizar dispositivos genéricos de E/S y

programarlos convenientemente

(b)

(a)

Arquitectura de Sistemas Paralelos (4)

Módulos de E/S

Definiciones

• Dispositivo externo: elementos que permiten la transferencia de información

entre la CPU y el mundo exterior. Funcionan a modo de interface

transformando la información asíncrona y analógica del mundo exterior a la

información síncrona y codificada del computador

• Módulo de E/S: elementos que permiten la conexión de un dispositivo externo

al bus del sistema. Los términos “controlador”, “procesador de E/S” y “módulo

de E/S” son equivalentes desde el punto de vista funcional:

• Los controladores son módulos de E/S muy sencillos que tienen el

hardware necesario para que funcione el dispositivo externo

• Los procesadores de E/S son auténticos procesadores con un juego

especializado de instrucciones orientado a operaciones de E/S, que son

programados por la CPU, permitiendo un funcionamiento autónomo

• Un dispositivo externo conectado a un módulo de E/S se denomina dispositivo

periférico o simplemente periférico

Arquitectura de Sistemas Paralelos (5)

Módulos de E/S

Diagrama de bloques de un dispositivo externo

Arquitectura de Sistemas Paralelos (6)

Módulos de E/S

Diagrama de bloques de un módulo de E/S

Arquitectura de Sistemas Paralelos (7)

Módulos de E/S

Funciones (I)

• Las funciones de un módulo de E/S son:

– Control y temporización

– Comunicación con el procesador

– Comunicación con los dispositivos

– Almacenamiento temporal

– Detección de errores

Arquitectura de Sistemas Paralelos (8)

Módulos de E/S

Funciones (II)

• Control y temporización

– Son necesarios para coordinar el tráfico entre dispositivos internos y externos

– Por ejemplo, el control de la transferencia de datos desde un dispositivo

externo al procesador podría implicar la siguiente secuencia de pasos:

1. El procesador pregunta por el estado del dispositivo

2. El módulo de E/S devuelve el estado del dispositivo

3. Si el dispositivo está listo, el procesador solicita la transferencia al módulo de E/S

4. El módulo de E/S obtiene los datos

5. Los datos se transfieren del módulo de E/S al procesador

• La comunicación con el procesador implica:

–

–

–

–

Decodificación de órdenes

Datos

Información de estado

Reconocimiento de dirección

Arquitectura de Sistemas Paralelos (9)

Módulos de E/S

Funciones (III)

• La comunicación con el dispositivo implica:

– Órdenes

– Información de estado

– Datos

• Almacenamiento temporal de datos

– Los datos se envían en ráfagas rápidas desde la memoria al módulo de E/S y

después se envían al periférico a la velocidad de éste (el proceso inverso es

semejante)

– Los datos se almacenan para no mantener ocupada a la memoria en una

operación de transferencia lenta (evitar una caída en el rendimiento)

• Detección de errores

– Errores debidos a defectos mecánicos o eléctricos

– Errores en la transmisión de información (códigos de detección de errores)

Arquitectura de Sistemas Paralelos (10)

Módulos de E/S

Funciones (IV)

Velocidades típicas de transferencia en dispositivos de E/S (bps)

(Almacenamiento temporal de datos)

Arquitectura de Sistemas Paralelos (11)

Mapa de Entrada/Salida: común y separado

Definición

• A la hora de integrar el subsistema de E/S (selección del dispositivos y

acceso a sus registros) en un computador existen dos posibilidades:

– E/S común o asignada/mapeada en memoria: en la que el procesador no

contempla el acceso a módulos de E/S. El acceso a los periféricos se hace

como si se accediese a un dato almacenado en la memoria principal. A los

periféricos se le asigna posiciones de memoria como si fueran variables. Ej:

el procesador Motorola 68000

– E/S aislada o separada: el acceso a la E/S está contemplado en la

arquitectura. Existen dos mapas de memoria separados: uno para memoria y

otro para E/S. Esto implica que existen instrucciones específicas de E/S

(inport/outport) y también señales específicas. Ej: la familia i80x86

• Aunque el sistema soporte espacios de direcciones separados no todos los

dispositivos tienen porqué usar los puertos de E/S: mientras que el uso de

los puertos de E/S eran común en las tarjetas ISA, los dispositivos PCI

suelen mapear sus registros en memoria

Arquitectura de Sistemas Paralelos (12)

Mapa de Entrada/Salida: común y separado

Ejemplo: Esquema de direcciones de E/S en un PC

Arquitectura de Sistemas Paralelos (13)

Mapa de Entrada/Salida: común y separado

Ventajas e inconvenientes

• Mapear la E/S en memoria tiene como ventajas:

– no utilizar instrucciones de propósito específico y aprovechar

toda la potencia del juegos de instrucciones, permitiendo una

mejor programación

– el acceso a memoria es mucho más eficiente

– el compilador tiene mas libertad para elegir el lugar y el modo de

direccionamiento en el acceso a memoria

• Y como inconveniente:

– se desperdicia parte del espacio de direcciones

Arquitectura de Sistemas Paralelos (14)

Mapa de Entrada/Salida: común y separado

Los problemas de la E/S en memoria

• Hay que tener en cuenta que las operaciones de E/S suelen tener

efectos colaterales (ej: bandera desactivada cuando se produce

una lectura) mientras que la operaciones con memoria no

• Cuando existen efectos colaterales las operaciones de E/S

mapeada en memoria pueden ser problemáticas

• Como la velocidad de acceso a memoria es crítica en el

rendimiento de la CPU, el acceso a memoria (sin efectos

colaterales) es optimizado: caché, optimizaciones del

compilador y reordenación hardware de instrucciones

• Para evitar el uso de la caché el espacio de memoria del

dispositivo puede ser configurado como memoria no cacheable

• Para evitar la optimización del compilador y la reordenación

harware de instrucciones cuando se programa deben utilizarse

memory barriers

Arquitectura de Sistemas Paralelos (15)

Métodos de Entrada/Salida

Clasificación

• Debido a la diferencia de velocidad entre procesador y

periféricos es necesario proporcionar mecanismos para

sincronizar las operaciones de E/S

• A la hora de clasificar los diferentes métodos para llevar

a cabo las operaciones de E/S hay que tener en cuenta los

siguientes factores:

– Inicio de la transferencia (¿quién comienza la transferencia?)

– Transferencia (¿quién realiza la transferencia?)

• Existen tres técnicas para realizar las operaciones de E/S:

– E/S programada

– E/S por interrupciones

– Acceso directo a memoria

Arquitectura de Sistemas Paralelos (16)

Métodos de Entrada/Salida

E/S programada

• También llamada por sondeo o encuesta (polling)

• La CPU tiene el control absoluto de la operación de E/S: inicia

y lleva a cabo la transferencia

• El procesador ejecuta un programa que controla directamente

la operación de E/S :

– Comprobación del estado

– Envío de una orden de lectura o escritura

– Transferencia de datos

• Esta técnica tiene la ventaja de utilizar un hardware mínimo

aunque malgasta tiempo de proceso ya que ha de interrogar

continuamente al periférico (espera activa,

en sistemas

multiproceso)

Arquitectura de Sistemas Paralelos (17)

E/S programada

Ejemplo de programación

void main ()

{

unsigned char estado;

...

inicializar_periferico_X();

...

while (!fin_operacion) {

estado = inportb (PUERTO_REG_ESTADO_X);

if ((estado & MASCARA_BIT_LISTO)!= 0)

hacer_operacion(); activo en alta

}

}

((estado | ~ MASCARA_BIT_LISTO)!= 0xFFFF)

activo en baja

Arquitectura de Sistemas Paralelos (18)

Métodos de Entrada/Salida

E/S por interrupciones

•

•

•

Para evitar la degradación en las prestaciones del sistema que supone la

espera activa, en este caso es el dispositivo el que solicita la operación de

E/S cuando se encuentra preparado para realizarla (interrupción)

La transferencia es llevada a cabo por la CPU de forma semejante a como

se hacía en la E/S programada

El esquema básico de funcionamiento de la E/S por interrupciones es:

1. El procesador ejecuta instrucciones de un programa

2. Al finalizar cada instrucción comprueba si se ha producido una interrupción

3. En caso afirmativo el procesador envía una señal de reconocimiento al

dispositivo, guarda el estado actual del proceso (contador del programa y

registros) y comienza a ejecutar la rutina que sirve la interrupción

(manejador de interrupción o rutina de servicio de interrupción)

4. Al finalizar la ejecución de la rutina de servicio, se recupera el estado de la

máquina y se continúa ejecutando el proceso que se abortó

Arquitectura de Sistemas Paralelos (19)

E/S por interrupciones

Esquema de funcionamiento

PSW=“Program Status Word”

PC=“Program Counter”

Arquitectura de Sistemas Paralelos (20)

E/S por interrupciones

Implementación

•

En la implementación de la E/S mediante interrupciones aparecen dos

cuestiones:

– ¿cómo se determina el procesador qué dispositivo ha provocado la

interrupción?

– si se han producido varias interrupciones, ¿cómo decide el

procesador la que debe atender?

•

Hay cuatro técnicas utilizadas comúnmente para implementar la E/S

por interrupciones:

–

–

–

–

Múltiples líneas de interrupción

Consulta software (software polling)

Conexión en cadena (daisy chain)

Arbitraje de bus

Técnicas que usan interrupciones vectorizadas

Arquitectura de Sistemas Paralelos (21)

Implementación de la E/S por interrupciones

Múltiples líneas de interrupción

• Consiste en proporcionar varías líneas de interrupción entre el

procesador y los módulos de E/S

• Es poco práctico porque malgasta terminales del procesador y además

de existir más periféricos que líneas no se resolvería el problema

• La prioridad viene fijada por el procesador

CPU

Periférico 0

Periférico 1

INT0

INT1

...

INTN

Arquitectura de Sistemas Paralelos (22)

Periférico N

Implementación de la E/S por interrupciones

Consulta software

• Todos los módulos de E/S comparten una línea común para solicitar

interrupciones

• Cuando el procesador detecta una interrupción, se produce un salto a

una subrutina de servicio de interrupción que se encarga de consultar a

cada módulo de E/S para determinar cuál ha producido la interrupción

• La desventaja de la consulta software está en el tiempo que consume

• La prioridad viene determinada por el orden en que se hace la encuesta

Arquitectura de Sistemas Paralelos (23)

Implementación de la E/S por interrupciones

Conexión en cadena (I)

•

•

•

•

•

•

•

Se trata de una consulta o polling hardware

Todos los módulos de E/S comparten una línea común para solicitar

interrupciones

La línea de reconocimiento de interrupción se conecta encadenando los

módulos uno tras otro

Cuando el procesador recibe una interrupción, activa la señal de

reconocimiento, la cual se propaga a través de la secuencia de módulos de

E/S hasta que alcanza al que solicitó la interrupción

El módulo correspondiente responde colocando una palabra que lo identifica

en las líneas de datos (vector)

El procesador utiliza el vector de interrupción como puntero a la rutina de

servicio (así se evita ejecutar una rutina de servicio general)

La prioridad viene determinada por el orden en que se conectan los módulos

en la cadena

Arquitectura de Sistemas Paralelos (24)

Implementación de la E/S por interrupciones

Conexión en cadena (II)

Arquitectura de Sistemas Paralelos (25)

Implementación de la E/S por interrupciones

Arbitraje de bus

•

•

•

•

Con esta técnica, un módulo de E/S antes de poder activar la línea de

petición de interrupción debe disponer del control del bus

Mediante el arbitrador de bus se garantiza que sólo un módulo puede

activar la señal de petición en un determinado instante

Es una técnica que usa interrupciones vectorizadas como el daisy chain

La prioridad viene determinada por el arbitrador

Arquitectura de Sistemas Paralelos (26)

Implementación de la E/S por interrupciones

Ejemplo de arbitrador: PIC 8259 (I)

•

•

•

•

Los 80x86 disponen de una sola línea de petición de interrupción

(INTR) y una sola línea de reconocimiento de interrupción (INTA)

Para manejar cierta variedad de dispositivos y estructuras de prioridad,

se configura un árbitro de interrupciones externo (PIC 8259)

El 8259 permite manejar hasta 8 módulos. Si se precisan más pueden

conectarse en cascada permitiendo manejar hasta 64 módulos

El esquema de funcionamiento de un sistema basado en el 8259 es el

siguiente:

– El 8259 acepta las solicitudes de interrupción de los dispositivos

conectados a él

– El 8259 determina qué interrupción tiene la prioridad más alta e

indica la petición al procesador activando la señal INTR

– El procesador reconoce la solicitud activando la señal INTA

– El 8259 sitúa el vector de interrupción apropiado en el bus

– El procesador comienza la ejecución de la rutina de servicio

Arquitectura de Sistemas Paralelos (27)

Implementación de la E/S por interrupciones

Ejemplo de arbitrador: PIC 8259 (II)

• El esquema de prioridades es configurable en el 8259. Se

permiten los siguientes modos:

– Completamente anidados: las solicitudes de interrupción se

ordenan según un nivel de prioridad desde 0 (IR0) hasta 7(IR7)

– Rotatorio: un dispositivo pasa a tener la menor prioridad del grupo

después de ser servido (aplicaciones en las que hay dispositivos con

igual prioridad de interrupción)

– Con máscara especial: se permite que el procesador pueda inhibir

selectivamente las interrupciones de determinados dispositivos

Arquitectura de Sistemas Paralelos (28)

Implementación de la E/S por interrupciones

Ejemplo de arbitrador: PIC 8259 (III)

Arquitectura de Sistemas Paralelos (29)

E/S por interrupciones

Habilitación/Deshabilitación de interrupciones

• Las interrupciones pueden ser:

– enmascarables: se pueden dejar de atender por software

– no enmascarables: siempre son atendidas

• Existen 3 niveles en los que habilitar/deshabilitar las interrupciones:

– A nivel de procesador: se deshabilitan todas las interrupciones

enmascarables

– A nivel de controlador de interrupciones (PIC): se pueden

habilitar/deshabilitar todas las interrupciones asociadas a un canal de

interrupción

– A nivel del dispositivo: los dispositivo periféricos suelen tener bits en sus

registros de E/S para habilitar/deshabilitar las diferentes interrupciones que pueden

generar

Arquitectura de Sistemas Paralelos (30)

E/S por interrupciones

Ejemplo de programación

void main () {

void interrupt (*manejador_antiguo)();

...

inicializar_periferico_X();

antiguo=getvect(INT_X);

disable(); /* Se deshabilitan mientras se manipulan

los vectores de interrupcion */

setvect(INT_X, manejador_intr_periferico_X);

enable ();

...

disable();

setvect(INT_X, manejador_antiguo);

enable (); }

void interrupt manejador_intr_periferico_X() {

... /* Se realizan las operaciones necesarias */}

Arquitectura de Sistemas Paralelos (31)

Acceso directo a memoria

Concepto

• Tanto la E/S por interrupciones como la E/S programada requieren la

intervención activa del procesador para transferir datos entre la

memoria y los módulos de E/S

• Ambos métodos tienen un impacto negativo sobre la actividad del

procesador y la velocidad de E/S

• Utilizando la E/S programada, el procesador puede transferir datos a

alta velocidad al precio de no hacer nada más

• La E/S con interrupciones libera en parte al procesador a expensas de

reducir la velocidad de E/S (debido a la sobrecarga que supone el

cambio de contexto)

• Cuando hay que transferir grandes volúmenes de datos, se requiere una

técnica más eficiente: el Acceso Directo a Memoria (DMA)

• En el DMA tanto el inicio de la transferencia como la transferencia en

sí están gobernadas por el dispositivo (se libera a la CPU)

Arquitectura de Sistemas Paralelos (32)

Acceso directo a memoria

El controlador de DMA

• El acceso directo a memoria requiere un módulo adicional en el bus

del sistema: el Controlador de DMA (DMAC)

• La única tarea de la CPU es programar el DMAC. Hay que enviarle al

menos la siguiente información:

–

–

–

–

Dirección del periférico de E/S

Posición inicial de memoria de donde se lee o se escribe

El tipo transferencia: lectura o escritura

El tamaño de la transferencia (número de palabras a transferir)

• El DMAC transfiere el bloque de datos completo, palabra a palabra,

directamente desde, o hacia, la memoria, sin que tenga que pasar a

través del procesador

• Cuando la transferencia ha concluido el DMAC envía una señal de

interrupción al procesador (TC, Terminal Count)

Arquitectura de Sistemas Paralelos (33)

Acceso directo a memoria

Implementación (I)

• Existen varias formas de realizar el acceso directo a memoria:

– Memoria multipuerto: la memoria permite realizar transferencias

simultáneas por parte de la CPU y el DMAC. La memoria tiene dos

puertos: uno para la CPU y otro para el DMAC. Es posible el acceso

concurrente a un mismo bloque de memoria por lo que hay que

establecer mecanismos de control

– Acceso a memoria por robo de ciclo: es una solución más

económica y es la utilizada habitualmente. El DMAC cada vez que

quiere tomar el control del bus del sistema para realizar una

transferencia, lo solicita a la CPU activando una señal (HOLD). La

CPU concede el control del bus (se activa la señal HLDA), el DMAC

se hace dueño del bus y realiza la transferencia. Ejemplo 80x86 y

8237:

• Transferencia en bloque o ráfaga

• Transferencia bajo demanda

• Transferencia simple

Arquitectura de Sistemas Paralelos (34)

Acceso directo a memoria

Implementación (II)

Acceso a memoria por robo de ciclo

Arquitectura de Sistemas Paralelos (35)

Acceso directo a memoria

Implementación (III)

•

La conexión del DMAC al sistema puede realizarse de varias formas

diferentes:

– Bus único, DMA independiente: El módulo de DMA actúa como un

procesador suplementario. Es económica pero ineficiente: la

transferencia de cada palabra consume dos ciclos de bus

– Bus único, DMA-E/S: El número de ciclos de bus necesarios puede

reducirse sustancialmente si se integran las funciones de DMA y E/S

(el camino entre el DMA y los módulos de E/S no incluye al bus del

sistema)

– Bus de E/S: El concepto anterior puede llevarse algo más lejos

conectado los módulos de E/S a un módulo de DMA mediante un bus

de E/S. Se reduce a uno el número de interfaces de E/S en el módulo de

DMA y es una configuración fácilmente ampliable

Arquitectura de Sistemas Paralelos (36)

Acceso directo a memoria

Implementación (IV)

Bus único,

DMA independiente

Bus único,

DMA-E/S

Bus de E/S

Arquitectura de Sistemas Paralelos (37)

Acceso directo a memoria

Ejemplo de módulo de DMA: DMAC 8237 (I)

•

•

•

•

El 8237 es un controlador de DMA de 4 canales programables en 3 modos

diferentes, con posibilidad de ser conectado en cascada y que además de las

funciones tradicionales soporta también transferencias memoria-memoria

El bus de datos es de 8 bits y el de direcciones de 16 bits (requiere un latch

externo porque está multiplexado para ahorrar pines)

Cuando se usa con la familia 80x86 es necesario un latch (registro de página) que

almacene los 4 bits superiores de la dirección del 80x86 en modo real (20 bits)

Modos de transferencia:

– Transferencia única: El dispositivo es programado para realizar una única

transferencia

– Transferencia de bloque: Se transfieren todas las palabras de las que consta

la transferencia

– Transferencia bajo demanda: la transferencia se realiza sólo mientras el

dispositivo siga solicitando el canal de DMA. Esta modalidad permite dejar

ciclos a la CPU cuando no es realmente necesario que el DMA opere

Arquitectura de Sistemas Paralelos (38)

Acceso directo a memoria

Ejemplo de módulo de DMA: DMAC 8237 (II)

•

•

•

•

•

El controlador de DMA es realmente un circuito secuencial generador de

señales de control y direcciones que permite la transferencia directa de los

datos sin necesidad de registros temporales intermedios (transferencia al vuelo)

Las operaciones memoria-memoria precisan de un registro temporal

intermedio, por lo que son al menos dos veces más lentas que las de E/S

(permiten chequeos para finalizar transferencias)

Cuando el 8237 está inactivo permanece desconectado de los buses del

sistema; cuando se produce una petición de DMA por parte de un dispositivo

(con DREQi se pide y con DACKi se confirma), genera una solicitud para

apropiarse del bus (HRQ), espera confirmación (HLDA) y a continuación

genera las señales necesarias para realizar la transferencia. Cuando acaba

genera una interrupción (TC, Terminal Count)

Dispone de esquemas de prioridad fija (DREQ0 más prioritaria) y rotativa

La operación que realiza el 8237 es consecuencia de la programación realizada

previamente en los registros de comando, modo, base de dirección y contador

de palabras a transferir

Arquitectura de Sistemas Paralelos (39)

Ejemplo de módulo de DMA: DMAC 8237

Sistema basado en un 8237

Arquitectura de Sistemas Paralelos (40)

Acceso directo a memoria

Ejemplo de programación

void main () {

void interrupt (*manejador_antiguo)();

...

inicializar_periferico_X();

inicializar_DMA (dir, tam, tipo, ...);

antiguo=getvect(INT_FIN_TRANS);

disable(); /* Se deshabilitan mientras se manipulan

los vectores de interrupcion */

setvect(INT_FIN_TRANS, manejador_fin_trans);

enable ();

...

disable();

setvect(INT_FIN_TRANS, manejador_antiguo);

enable (); }

void interrupt manejador_fin_trans () {

/* Se comprueban los posibles errores de la transferencia */ ...}

Arquitectura de Sistemas Paralelos (41)

Métodos de E/S

Resumen

Arquitectura de Sistemas Paralelos (42)

Ejemplo de dispositivo de E/S

Interfaz Periférico Programable 8255

•

•

•

•

Características

Diagrama de bloques

Direcciones y registros de control

Modos de funcionamiento:

– Modo 0 (E/S programada)

– Modo 1 (E/S por interrupciones)

– Modo 2 (E/S bidireccional)

• Emulación interfaz centronics (puerto paralelo impresora)

mediante un 8255

Arquitectura de Sistemas Paralelos (43)

Interfaz Periférico Programable 8255

Características

• Dispone de tres puertos de E/S (A, B y C):

dos de tamaño byte (A y B) y uno de tamaño

2x4 bits (C) con control bit a bit

• Los puertos pueden ser configurados como

entrada, salida o bidireccionales

• Dispone de líneas de protocolo

Arquitectura de Sistemas Paralelos (44)

Interfaz Periférico Programable 8255

Diagrama de bloques

Arquitectura de Sistemas Paralelos (45)

Interfaz Periférico Programable 8255

Direcciones y registros de control

Arquitectura de Sistemas Paralelos (46)

Interfaz Periférico Programable 8255

Modo 0 (E/S Programada)

• Se utilizan los tres puertos (A,B,C) como simples registros

donde leer y escribir. La CPU y el/los dispositivo/s externo/s

correspondiente/s se encarga/n de leer/escribir de acuerdo a un

determinado protocolo previamente definido

¾El puerto A (8 bits) se configura como entrada o salida con el bit

D4 del registro de control

¾El puerto B (8 bits) se configura como entrada o salida con el bit

D1 del registro de control

¾El puerto C alto (4 bits) se configura como entrada o salida con el

bit D3 del registro de control

¾El puerto C bajo (4 bits) se configura como entrada o salida con el

bit D0 del registro de control

Arquitectura de Sistemas Paralelos (47)

Interfaz Periférico Programable 8255

Cronograma Modo 0

Arquitectura de Sistemas Paralelos (48)

Interfaz Periférico Programable 8255

Modo 1 (E/S por interrupciones)

• En este modo se utiliza el protocolo Handshake

¾El puerto A (8 bits) se configura como entrada o salida con el

bit D4 del registro de control

¾El puerto B (8 bits) se configura como entrada o salida con el

bit D1 del registro de control

¾El puerto C contiene las señales del protocolo

Arquitectura de Sistemas Paralelos (49)

Interfaz Periférico Programable 8255

Modo 1 (E/S por interrupciones). Configuración de entrada

Señales de protocolo cuando el puerto está configurado como entrada

STBA (strobe input): Un cero en esta línea de entrada indica

que hay dato disponible en el puerto A (activada por el

dispositivo externo)

IBFA (input buffer full): Un uno en esta línea de salida indica

que el dato ya ha sido cargado en el registro del puerto A.

IBFA se desactiva cuando se desactiva STBA (el dispositivo

externo da su confirmación) y se produce el flanco de subida

de la señal RD (dato leído por la CPU)

Las señales STBB , IBFB son funcionalmente equivalentes

Arquitectura de Sistemas Paralelos (50)

Interfaz Periférico Programable 8255

Modo 1 (E/S por interrupciones) Configuración de salida

Señales de protocolo cuando el puerto está configurado como salida

OBFA (output buffer full): esta línea de salida se pone a cero

(activa en baja) para indicarle al dispositivo que la CPU ha

escrito un dato en el puerto A. Se activa con el flanco de

subida de la señal WR (escritura finalizada) y se desactiva

con la confirmación del dispositivo (ACKA)

ACKA (acknowledge input): un cero en esta entrada indica

que los datos del puerto A han sido leídos por el

dispositivo externo. Esencialmente es una respuesta del

dispositivo periférico indicando que ha sido recibido el

dato enviado por la CPU

Las señales OBFB y ACKB son funcionalmente equivalentes

Arquitectura de Sistemas Paralelos (51)

Interfaz Periférico Programable 8255

Modo 1 (E/S por interrupciones). Interrupciones

•

•

•

•

Señales de interrupción se pueden generar en los puertos A y B tanto si

están configurados como entrada (la CPU debe leer un dato) como si lo

están como salida (la CPU ya puede escribir un nuevos dato)

El bit 4 del puerto C (PC4) es el bit de habilitación de interrupción del

puerto A (INTEA) cuando está configurado como entrada y el PC6 cuando

lo está como salida. El del puerto B (INTEB) es el bit 2 (PC2).

Para que el 8255 genere una interrupción asociada al puerto A (señal

INTRA) cuando está configurado como entrada, se debe cumplir que:

STBA es 1, IBFA es 1 e INTEA es 1

(semejante para el puerto B)

Para que el 8255 genere una interrupción asociada al puerto A (señal

INTRA) cuando está configurado como salida, se debe cumplir que:

ACKA es 1, OBFA es 1 e INTEA es 1

(semejante para el puerto B)

Arquitectura de Sistemas Paralelos (52)

Interfaz Periférico Programable 8255

Modo 1 (E/S por interrupciones). Registros y señales

Arquitectura de Sistemas Paralelos (53)

Interfaz Periférico Programable 8255

Cronograma Modo 1

1

2

5

3

4

Comienzo de la

ejecución de los

manejadores de

interrupción

Arquitectura de Sistemas Paralelos (54)

1

2

4

5

3

Interfaz Periférico Programable 8255

Modo 2 (E/S bidireccional)

• El PUERTO A funciona de forma bidireccional. Es como un doble

modo 1. El PUERTO B no tiene este modo

¾ Los cinco líneas superiores del puerto C contienen las señales de

protocolo

Señales de protocolo

(semejantes a las descritas en el modo 1)

STB (strobe input)

IBF (input buffer full)

ACK (acknowledge)

OBF (output buffer full)

INTR

Arquitectura de Sistemas Paralelos (55)

Interfaz Periférico Programable 8255

Modo 2 (E/S bidireccional). Registro y señales

Arquitectura de Sistemas Paralelos (56)

Interfaz Periférico Programable 8255

Cronograma Modo 2

Arquitectura de Sistemas Paralelos (57)

Interfaz Periférico Programable 8255

Emulación interfaz centronics (puerto paralelo impresora)

Arquitectura de Sistemas Paralelos (58)

Operaciones de E/S desde el SO

El S.O. Linux y la programación de drivers

•

•

•

•

El kernel de Linux ofrece una interfaz de programación que facilita la

creación de drivers, de manera que el diseñador debe mapear llamadas al

sistema independientes del driver de carácter estándar con operaciones

específicas del driver

Una característica interesante de esta interfaz de programación es que los

drivers pueden ser implementados fuera del kernel y añadidos a éste en

tiempo de ejecución

La distinción entre mecanismos (capacidades que se ofrecen) y política (uso

de esas capacidades) es una de las mejores ideas aplicadas al diseño de

sistemas UNIX

Esta idea se aplica al diseño de drivers: drivers libres de política (driver para

un floppy). El objetivo es programar código para el kernel que permita el

acceso al dispositivo sin forzar ninguna política puesto que diferentes

usuarios pueden tener necesidades diferentes (acceso flexible, sin

restricciones)

Arquitectura de Sistemas Paralelos (59)

El S.O. Linux y la programación de drivers

El kernel de Linux

Arquitectura de Sistemas Paralelos (60)

El S.O. Linux y la programación de drivers

Programación del kernel: Módulos

• Una de las características más significativas de Linux es la

posibilidad de ampliar la funcionalidad del kernel en

tiempo de ejecución

• El código que se añade al kernel en tiempo de ejecución se

denomina módulo

• El kernel de Linux ofrece soporte para diferentes tipos de

módulos incluido los drivers, aunque no limitados a ellos

• Clases de dispositivos y módulos

– Dispositivos de caracteres

– Dispositivos de bloque

– Interfaces de red

Arquitectura de Sistemas Paralelos (61)

Programación del kernel: Módulos

Módulos vs Aplicación

Aplicación

Módulo

• Ejecuta una tarea desde que

comienza hasta que acaba

• Puede utilizar funciones que

no han sido definidas por

ella, linkando con las

librerías adecuadas (printf)

• Se ejecutan en el espacio de

usuario

• Permite atender solicitudes

de procesos en ejecución

• Puede usar sólo las funciones

que el kernel exporta (printk)

• Se ejecuta en el espacio del

kernel

Los módulos que se encuentran cargados en un momento dado pueden conocerse con el

comando lsmod o cat /proc/modules

Los dispositivos del sistema pueden conocerse con el comando cat /proc/devices

Arquitectura de Sistemas Paralelos (62)

Programación del kernel: Módulos

Espacio de usuario y espacio del kernel

•

•

•

•

•

•

Una de las tareas de un S.O. es proteger de accesos no autorizados a los

diferentes recursos del sistema

Esta tarea del S.O. requiere un componente hardware de protección en el

procesador: diferentes niveles con funciones diferentes y operaciones no

permitidas en niveles inferiores (todos los actuales procesadores disponen de

al menos dos niveles)

Los sistemas Unix utilizan dos niveles de protección:

– Modo superusuario: en el que se ejecuta el kernel (todo está permitido)

– Modo usuario: en el que se ejecutan las aplicaciones (se evitan accesos

directos al hardware y accesos a memoria no autorizados)

Habitualmente se denominan espacio del kernel y espacio de usuario

La aplicaciones y los módulos del kernel tienen mapas de memoria diferentes.

Se requieren funciones para realizar transferencias de datos de uno a otro. Ej:

copy_to_user y copy_from_user

El espacio del kernel a diferencia del de usuario es nonswappable (no

paginable) y nonpreemptive (de ejecución no concurrente)

Arquitectura de Sistemas Paralelos (63)

El S.O. Linux y la programación de drivers

Puertos de E/S y E/S mapeada en memoria

•

•

•

Un dispositivo periférico es controlado mediante operaciones de

lectura/escritura sobre sus registros internos

Desde el punto de vista del hardware no hay diferencias conceptuales entre que

estos registros estén mapeados en E/S o en memoria (cat /proc/ioport y cat

/proc/iomem)

Para evitar los problemas de los efectos colaterales en la E/S mapeada en

memoria:

– el espacio de memoria del dispositivo debe ser configurado como memoria no

cacheable (ej: opción en el espacio de configuración de los dispositivos PCI)

– deben utilizarse memory barriers (ej: rmb, wmb, y mb)

•

•

•

Existen funciones para leer y escribir en los puertos una palabra (operaciones

simples) o más (operaciones complejas). Ej: inb, outb, insb, ..

Existen funciones para leer y escribir en memoria (operaciones simples y

complejas). Ej: readb, writeb, memcpy_fromio, memcpy_toio, …

Algunas plataformas reservan un espacio de memoria no paginable para la E/S

mapeada en memoria (no ocurre en ISA/PCI x86). Si el acceso a la memoria

asignada está virtualizado se requiere el uso de funciones especiales (ioremap y

iounmap)

Arquitectura de Sistemas Paralelos (64)

El S.O. Linux y la programación de drivers

Gestión de interrupciones (I)

• El Linux existen dos tipos de interrupciones:

– Rápidas: Deben ser rápidamente atendidas, pues su ejecución se realiza con

todas las interrupciones deshabilitadas (interrupción de un timer)

– Lentas: Se ejecutan con todas las interrupciones habilitadas excepto la que

está siendo servida, por lo que su tratamiento puede consumir más tiempo

• Para que un módulo pueda atender las solicitudes de interrupción de un

determinado canal debe asignarle un manejador de interrupción cuando

se carga el módulo (request_irq) y desasignárselo cuando se descarga

(free_irq)

• Mediante el comando cat /proc/interrupts se saben las IRQs asociadas a

cada dispositivo

• Mediante el comando cat/proc/stat se sabe las veces que se ha ejecutado

una IRQ

• Existen funciones para habilitar y deshabilitar las interrupciones: sti, cli,

enable_irq, diable_irq, …

Arquitectura de Sistemas Paralelos (65)

El S.O. Linux y la programación de drivers

Gestión de interrupciones (II)

• El problema que presenta la gestión de interrupciones es que no pueden

realizarse tareas demasiado largas en el manejador

• El manejador necesita acabar cuanto antes para desbloquear las

interrupciones (sobre todo en las rápidas)

• Solución: Dividir la funcionalidad del manejador en dos rutinas: top-half

y bottom-half

• La diferencia principal entre ellas es que todas las interrupciones están

habilitadas durante la ejecución de la rutina bottom-half

• La rutina top-half (manejador) realizará lo qué debe hacerse de manera

inmediata (operación de E/S) mientras que la rutina bottom-half hará el

resto (procesado de la información)

• Existen diferentes formas de que el kernel comience la ejecución de la

rutina bottom-half (se establecen colas)

• En la rutina de interrupción (top-half) hay que insertar la tarea

planificada (rutina bottom-half) en una de las colas de tareas e indicarle

al kernel que la tarea está lista para su ejecución

Arquitectura de Sistemas Paralelos (66)