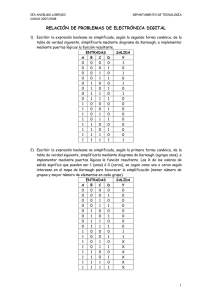

Tema 3: Representación y minimización de funciones lógicas

Anuncio

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

Tema 3: Representación y minimización de

funciones lógicas

3.1. Teoremas y postulados del álgebra de Boole

Definiciones

El álgebra de Boole se utiliza para la resolución de problemas de tipo

lógico-resolutivo, desarrollado en 1947 por George Boole.

Actualmente es muy utilizada en electrónica digital (en computadoras), y

sobre todo en síntesis de circuitos digitales.

El álgebra de Boole son las matemáticas de los sistemas digitales.

Variable lógica:

Sea el conjunto B = { 0, 1 }. Con este conjunto podemos codificar la

información en un computador.

Decimos que una variable x es lógica si su dominio es el conjunto B, es

decir, si x solo puede tomar los valores 0 y 1.

Complemento:

El complemento de una variable es su inverso, y se indica con una barra

encima, ó con un apóstrofe.

Lo más utilizado siempre es la barra, pero en estos apuntes utilizamos

un apóstrofe por comodidad en la escritura.

Por ejemplo, el complemento de A es A'.

Si A = 0, entonces A' = 1

Si A = 1, entonces A' = 0

1

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

Postulados del algebra de Boole

Un conjunto B = { 0, 1 }, dotado de dos operaciones denotadas por + y ·,

es un álgebra de Boole si y sólo si se verifican los siguientes postulados o

leyes. En todos los casos consideramos ∀ a,b,c ∈ B.

1. Las operaciones + y · son conmutativas:

a+b=b+a

(conmutativa de la suma)

a·b =b·a

(conmutativa del producto)

2. Las operaciones + y · son asociativas:

a + (b + c) = (a + b) + c (asociativa de la suma)

a · (b · c) = (a · b) · c

(asociativa del producto)

3. Cada operación es distributiva respecto a la otra:

+ respecto ·: a + (b · c) = (a + b) · (a + c)

· respecto +: a · (b + c) = (a · b) + (a · c)

∀ a,b,c ∈ B

Un álgebra de Boole es simétrica con respecto a las operaciones + y ·, y a

los elementos identidad 0 y 1. Tal característica es el principio de dualidad,

es decir, si tenemos un teorema, podemos obtener otro dual, cambiando las

operaciones.

Reglas

Un álgebra de Boole B tiene las siguientes propiedades o reglas:

1.

2.

3.

4.

5.

6.

7.

8.

9.

Identidad (+):

Elementos dominantes (+):

Elementos dominantes (·):

Identidad (·):

Idempotencia (+):

Complemento (+):

Idempotencia (·):

Complemento (·):

Involutiva:

10. Ley de absorción (dual):

11. Ley del consenso (dual):

a+0=a

a+1=1

a·0=0

a·1=a

a+a=a

a + a' = 1

a·a=a

a · a' = 0

a'' = a

∀a∈B

∀a∈B

∀a∈B

∀a∈B

a + (a · b) = a y a · (a+b) = a

a + (a' · b) = a + b y a · (a’+b) = a · b

Las 2 últimas reglas se pueden obtener a partir de las leyes y de las otras

reglas más sencillas.

a' = Complementario de a

2

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

3.2. Teoremas de De Morgan

De Morgan propuso dos teoremas que constituyen una parte muy

importante del álgebra de Boole.

Teoremas de De Morgan:

1. El complemento de una suma de variables es igual al producto de los

complementos de las variables:

(a + b)' = a' · b'

∀ a,b ∈ B

2. El complemento de un producto de variables es igual a la suma de los

complementos de las variables:

(a · b)' = a' + b'

∀ a,b ∈ B

Estos teoremas son válidos para cualquier número de variables.

Ejemplos:

•

a · b · c = a' + b' + c'

•

(a + b + c)' = a' · b' · c'

•

(a' + b' + c') ' = a · b · c

•

((a + b + c) · d) ' = (a + b + c)' + d' = (a + b + c)' + d' = (a' · b' · c') + d'

•

((a·b·c) + (d·e·f)) ' = (a·b·c)' · (d·e·f)' = (a'+b'+c') · (d'+e'+f')

•

((a+b)·c'·d' + e + f') ' = ((a+b)·c'·d')' · e' · f = ((a+b)'+c+d) · e' · f =

= ((a' · b') + c + d) · e' · f

Funciones lógicas

Función lógica:

Dadas n variables lógicas x1, x2, ... xn , decimos que F es una función

lógica de las citadas variables si:

F(x1, x2, ... xn) ∈ B

es decir, si F sólo toma los valores 0 y 1. Al número de variables también se le

llama dominio.

3

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

Una función lógica puede definirse de dos formas:

a) Mediante una expresión algebraica, en la que intervengan las

variables x1, x2 , ... xn (y sus complementarias: x1', x2', ... xn')

relacionadas entre sí mediante las operaciones + y ·.

b) Mediante una tabla de verdad, que consiste en expresar en una

tabla todas las posibles combinaciones de las variables de entrada

x1, x2, ... xn , asociando un valor a la salida. El número de

combinaciones es 2n. Es posible tener más de una salida en la

misma tabla: multifunciones.

Ejemplos:

Sean x1 y x2 dos variables lógicas. Ejemplos de expresiones algebraicas

y sus correspondientes tablas de verdad serían:

F1 = x1'

F3 = x1 · x2'

F2 = x1 + x2

x1

F1

x1 x2

F2

x1 x2'

F3

0

1

1

0

0

0

1

1

0

1

1

1

0

0

1

1

0

0

1

0

0

1

0

1

1

0

1

0

Como podemos observar, para construir la tabla de verdad de una

función lógica, escribimos en las columnas de la izquierda todas las

combinaciones posibles de las variables independientes, y en la columna de la

derecha, los valores de la función correspondientes a cada combinación de las

variables independientes.

Las tablas de verdad permiten una representación compacta, pudiendo

además definir dos o más funciones en una sola tabla, siempre y cuando

dependan de las mismas variables independientes.

Una suma de productos es igual a 1 si y sólo si al menos uno de los

productos es igual a 1.

Un producto de sumas es igual a 0 solamente si al menos uno de los

términos es igual a 0.

Por otro lado, dadas dos expresiones algebraicas F1 y F2 diferentes, sus

valores en la tabla pueden coincidir. En ese caso diremos que ambas

funciones son equivalentes (F1 = F 2).

4

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

Ejemplos:

•

Suma de productos:

F1 = (a' · b' · c) + (a · b' · c' ) + (a · b · c)

(3 variables)

Los valores binarios que hacen que los productos de la expresión sean 1

son: 001 (a'·b'·c), 100 (a·b'·c'), 111 (a·b·c).

Para estas combinaciones, en la columna de salida de la tabla de verdad

pondremos un 1; en el resto pondremos 0.

•

a

b

c

F1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

0

1

0

0

1

Producto de sumas:

F2 = (a+b+c) · (a+b'+c) · (a+b'+c') · (a'+b+c') · (a'+b'+c)

Los valores binarios que hacen que los términos suma sean 0 son: 000

(a+b+c), 010 (a+b'+c), 011 (a+b'+c'), 010 (a'+b+c'), 110 (a'+b'+c).

Para estas combinaciones, en la columna de salida de la tabla de verdad

pondremos un 0; en el resto pondremos 1.

a

b

c

F2

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

0

1

0

0

1

Podemos comprobar que ambas funciones son equivalentes (F 1=F2).

5

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

Ejemplo:

Sean las dos funciones lógicas siguientes, que dependen ambas de las

mismas variables lógicas: a, b y c.

F1 = (a + b + c) · (a + b + c') · (a' + b + c) · (a' + b + c')

F2 = (a' · b · c') + (a' · b · c) + (a · b · c') + (a · b · c)

Podemos representarlas en una única tabla de verdad (multifunciones):

a

b

c

F1

F2

0

0

0

0

0

0

1

1

0

1

0

1

0

0

1

1

0

0

1

1

1

1

1

1

0

0

1

1

0

1

0

1

0

0

1

1

0

0

1

1

Podemos comprobar que ambas funciones son equivalentes (F 1 = F 2).

Obtención de la expresión algebraica a partir de la tabla

Podemos obtener la expresión algebraica a partir de la tabla de verdad.

Dada una función lógica F, ésta solo puede tomar los valores 0 y 1.

Podemos definir F indicando para qué combinaciones de las variables

independientes, toma el valor 1 (implementación por "1"), o bien, para qué

combinaciones toma el valor 0 (implementación por "0").

Implementación por "1":

Obtendremos una suma de productos. La función F será cierta para

alguna de las combinaciones (suma lógica) que sean ciertas (vale "1"). Cada

combinación será cierta cuando sean ciertas todas las variables que la

componen (producto lógico). Si alguna de las variables en la combinación

elegida es falsa (vale "0"), su negación será cierta (valdrá "1").

Implementación por "0":

Obtendremos un producto de sumas. La función F será cierta cuando no

se da ninguna de las combinaciones para las cuales es falsa (producto lógico).

Una de estas combinaciones no ocurre cuando es falsa (negación) alguna de

las variables (suma lógica) que componen la combinación.

6

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

Ejemplo:

Sea la tabla de verdad del ejemplo anterior (F 1 = F2 = F).

Recordamos que:

ó (OR Lógica)

y (AND Lógica)

=

=

+ (Suma lógica)

· (Producto lógico)

Implementación por "1":

La función F es cierta (vale 1) para las siguientes combinaciones:

a

b

c

F

Condiciones para que F=1

0

0

1

1

1

1

1

1

0

1

0

1

1

1

1

1

a' y b y c'

a' y b y c

a y b y c'

a ybyc

⇒

⇒

⇒

⇒

a' · b · c'

a' · b · c

a · b · c'

a · b·c

La función F será cierta cuando se cumpla la primera combinación, ó la

segunda, ó la tercera ó la cuarta, es decir, cuando se cumpla cualquiera de

esas cuatro combinaciones. Una combinación es cierta si y solo si son ciertos

todos los valores:

F = (a' · b · c') + (a' · b · c) + (a · b · c') + (a · b · c)

Podemos comprobar como hemos obtenido la misma función que la

función F 1 del ejemplo anterior (suma de productos).

Implementación por "0":

La función es cierta (vale 1) para las siguientes combinaciones:

a

b

c

F

Condiciones para que F=1

0

0

1

1

0

0

0

0

0

1

0

1

0

0

0

0

aóbóc

a ó b ó c'

a' ó b ó c

a' ó b ó c'

⇒

⇒

⇒

⇒

a+b+c

a + b + c'

a' + b + c

a' + b + c'

La función F será cierta (vale 1) si y solo si no se cumple la primera

combinación, y no se cumple la segunda, y no se cumple la tercera y no se

cumple la cuarta, es decir, cuando no se cumpla ninguna de esas cuatro

combinaciones. Una combinación no es cierta si y solo si no es cierto el primer

valor ó no es cierto el segundo ó no es cierto el tercero.

Un valor no es cierto si su complemento es cierto (vale "1").

7

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

Sustituyendo las "y" por productos lógicos, las "ó" por sumas lógicas e

incluyendo las complementaciones, tenemos como expresión de la función:

F = (a + b + c) · (a + b + c') · (a' + b + c) · (a' + b + c')

Podemos comprobar como hemos obtenido la misma función que la

función F 2 del ejemplo anterior (producto de sumas).

Hemos comprobado así mismo, que las funciones F1 y F2 son

equivalentes, y que cualquier función puede expresarse mediante las variables

independientes, relacionadas mediante las operaciones suma, producto y

negación.

Por tanto, tenemos dos formas de obtener la expresión algebraica de

una función a partir de la tabla de verdad.

Siguiendo el proceso inverso, ya hemos visto cómo fácilmente podemos, a

partir de la expresión algebraica, obtener:

q

q

las combinaciones de la tabla de verdad para las cuales la función vale 1

desde una suma de productos

las combinaciones de la tabla de verdad para las cuales la función vale 0

desde un producto de sumas.

Forma canónica de una función lógica

Se llama término canónico de una función lógica a todo producto o

suma en el cual aparecen todas las variables (o sus complementos) de esa

función. A los términos producto se les llama productos canónicos

(mintermus) y a los términos suma, sumas canónicas (maxtermus).

Cuando una función se expresa como una suma de productos canónicos

(mintermus) o como producto de sumas canónicas (maxtermus) se dice que se

encuentra en su forma canónica o estándar.

•

•

La implementación por "1" nos lleva a la forma canónica de suma de

productos.

La implementación por "0" nos lleva a un producto de sumas.

Aplicando los teoremas de De Morgan, podemos convertir una función

expresada en sumas de productos (mintermus) a producto de sumas

(maxtermus) y viceversa.

Aplicando las leyes distributivas, podemos convertir cualquier función

que no esté en forma canónica a suma de productos o productos de sumas

(forma canónica):

F = a·b + c·(d+e) = a·b + c·d + c·e

8

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

Ejemplo:

•

Producto de sumas è Suma de productos (maxtermusèmintermus)

F = ((a + b + c') · (a + b' + c)) ' =

= (a + b + c') ' + (a + b' + c) ' =

= (a' · b' · c) + (a' · b · c')

•

Suma de productos è Producto de sumas (MintermusèMaxtermus)

F = (a · b · c) + (a · b' · c') =

= ( (a · b · c) + (a · b' · c') ) '' =

= ( (a · b · c)' · (a · b' · c')' ) ' =

= ( (a' + b' + c') · (a' + b + c) ) '

Conversión de una suma de productos a su forma canónica

Utilizando lo siguiente podemos convertir un término producto que no

contenga todas las variables a otro que si las tenga:

• Regla 6 del álgebra de Boole:

(a + a' = 1)

• Propiedad distributiva:

a·(b+c) = (a·b) + (a·c)

Tenemos que multiplicar cada término producto que no esté en forma

canónica por un término formado por la suma de la variable que le falta y su

complemento. Multiplicar por 1 no altera el valor de un término. El número de

productos se duplica por cada variable que falta.

Ejemplo:

Convertir la siguiente expresión booleana al formato suma de productos

canónicos:

F = (a·b'·c) + (a'·b') + (a·b·c'·d)

Tenemos 4 variables: a,b,c,d. Consideramos cada término por separado.

a·b'·c = (a·b'·c) · (d+d') = (a·b'·c·d) + (a·b'·c·d')

a'·b' = (a'·b') · (c+c') = (a'·b'·c) + (a'·b'·c') =

= [ (a'·b'·c) · (d+d') ] + [ (a'·b'·c') · (d+d') ] =

= [ (a'·b'·c·d) + (a'·b'·c·d') ] + [ (a'·b'·c'·d) + (a'·b'·c'·d') ]

a·b·c'·d

=> Ya lo tenemos en forma canónica

Sustituyendo cada término por su equivalente término canónico:

F = (a·b'·c·d) + (a·b'·c·d') + (a'·b'·c·d) + (a'·b'·c·d') +

+ (a'·b'·c'·d) + (a'·b'·c'·d') + (a·b·c'·d)

9

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

Conversión de un producto de sumas a su forma canónica

Utilizando lo siguiente podemos convertir un término suma que no

contenga todas las variables a otro que si las tenga:

• Regla 8 del álgebra de Boole:

(a · a' = 0)

• Propiedad distributiva:

a+(b·c) = (a+b) · (a+c)

Tenemos que sumar a cada término suma que no esté en forma

canónica un término formado por el producto de la variable que le falta y su

complemento. Sumar 0 no altera el valor de una suma. El número de sumas se

duplica por cada variable que falta.

Ejemplo:

Convertir la siguiente expresión booleana al formato de producto de

sumas canónico.

F = (a+b'+c) · (b'+c+d') · (a+b'+c'+d)

Tenemos 4 variables: a,b,c,d. Consideramos cada término por separado.

(a+b'+c) = (a+b'+c) + (d · d') = (a+b'+c+d) · (a+b'+c+d')

(b'+c+d') = (b'+c+d') + (a · a') = (a+b'+c+d') · (a'+b'+c+d')

(a+b'+c'+d) ⇒ Ya lo tenemos en forma canónica

Sustituyendo cada término por su equivalente término canónico:

F = (a+b'+c+d) · (a+b'+c+d') · (a+b'+c+d') · (a'+b'+c+d') · (a+b'+c'+d)

10

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

Forma compacta de una función en forma canónica

Una expresión en forma canónica puede expresarse de una forma

compacta. La forma compacta de representar esta tabla o las expresiones

lógicas sería indicando las combinaciones que hacen cierta (suma de

productos) o falsa (producto de sumas) la función F de la siguiente forma:

Forma de la expresión

suma de productos

producto de sumas

Forma compacta

F = Suma de mi = ∑ (Combinaciones ciertas)

F = Producto de Mi = Π (Combinaciones falsas)

Sea la función F definida por la tabla de verdad siguiente:

a

0

0

0

0

1

1

1

1

b

0

0

1

1

0

0

1

1

c

0

1

0

1

0

1

0

1

F

0

0

0

1

0

1

1

0

Mintermus (m) Maxtermus (M)

M0 = a+b+c

M1 = a+b+c'

M2 = a+b'+c

m3 = a'·b·c

M4 = a'+b+c

m5 = a·b'·c

m6 = a·b·c'

M7 = a'+b'+c'

Valor

0 = 000

1 = 001

2 = 010

3 = 011

4 = 100

5 = 101

6 = 110

7 = 111

Por tanto, las expresiones lógicas equivalentes "suma de productos" y

"producto de sumas" son:

F = m3 +m5+m6

= (a'·b·c) + (a·b'·c) + (a·b·c')

F = M0 ·M1·M2·M4·M7 = (a+b+c) · (a+b+c') · (a+b'+c) · (a'+b+c) · (a'+b'+c')

Si expresamos en binario las combinaciones:

Suma de productos (directo):

011+101+110

Producto de sumas (complementados): 000·001·010·100·111

Las expresiones compactas son:

Suma de productos: F = ∑ (3,5,6)

Producto de sumas: F = Π (0,1,2,4,7)

F = ∑ (3,5,6) = Π (0,1,2,4,7)

Ambas expresiones compactas son equivalentes, como se demuestra aquí:

q

q

q

q

Sabemos que: Mi = mi' (DeMorgan)

Tenemos que: F = ∑ (3,5,6) = m3 + m5 + m6

Obtenemos la función complementada F', que valdrá 1 para aquellas

combinaciones que F=0 (y no estará definida para las mismas

combinaciones que F).

F' = ∑ (0,1,2,4,7) = m0+m1+m2+m4+m7

Complementamos en ambas partes de la igualdad:

F'' = F = (m0+m1+m2+m4+m7)' = m0'·m1'·m2'·m4'·m7' ⇒

⇒ F = M0·M1·M2·M4·M7 =

⇒ F = Π(M0,M1,M2,M4,M7) = Π(0,1,2,4,7)

11

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

3.3. Puertas lógicas

Introducción

Los computadores actuales utilizan como soporte tecnológico los

circuitos electrónicos, por lo que se consiguen grandes velocidades. Pero estos

circuitos electrónicos no pueden manejar directamente cifras ni caracteres. La

información se representa casi siempre mediante tensiones eléctricas.

Ahora bien, pueden utilizarse tensiones eléctricas de dos tipos:

•

Señales analógicas: las tensiones toman cualquier valor dentro de un

intervalo determinado. Permiten representar una magnitud y asignarle un

valor cualquiera.

•

Señales discretas: las tensiones sólo toman unos valores concretos.

Permiten representar un número limitado de valores diferentes. En el caso

de que el número de valores diferentes que pueda representar la tensión

sean solo dos, la señal se denomina lógica o digital.

En los computadores se utilizan señales lógicas para representar la

información. A los dos valores que puede tomar dicha señal, se les asigna

habitualmente como 0 y 1.

La razón de la utilización de este tipo de señales es, fundamentalmente

tecnológica. Existe un tipo de circuitos electrónicos, denominados circuitos

digitales, que trabajan solo con dos niveles de tensión, y que pueden realizar

una transición de un nivel a otro.

Las ventajas que presentan estos circuitos respecto a los analógicos

son:

•

•

•

•

•

•

•

Gran simplicidad de diseño

Velocidad de trabajo más elevada

Consumo más reducido

Inmunidad al ruido muy elevada (margen de error)

Posibilidad de diseño descendente, al poder confeccionar cualquier

circuito, por complejo que sea, con unidades más simples diseñadas

previamente.

Posibilidad de aumentar hasta el nivel que se desee, la precisión en

la representación de una información numérica.

Menor coste de fabricación, para las mismas prestaciones, ya que al

poder construir cualquier circuito con unidades básicas, permite

fabricar éstas en grandes cantidades.

El único inconveniente es una complejidad superior de los circuitos, que

no es tal inconveniente, gracias a la posibilidad de diseño y análisis

descendente.

12

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

Las únidades básicas más simples que componen los circuitos digitales

se denominan puertas lógicas, y son circuitos que implementan las funciones

lógicas elementales. Son bloques de construcción básicos de funciones más

complejas. Se representan por unos símbolos de acuerdo al estándard ANSI /

IEEE 91-1984.

Los valores lógicos "0" y "1" se representan por niveles de tensión

diferentes en las líneas de entrada y salida de estos circuitos.

Realmente estos dos niveles de tensión son bastante diferentes entre si.

Los circuitos digitales se diseñan de tal forma, que reconocen un valor lógico,

aunque la tensión no tome exactamente el nivel definido, siempre y cuando

esté dentro de una franja alrededor de dicho nivel, permitiendo una cierta

inmunidad ante variaciones en la señal de entrada (ruido).

Se dice que una lógica es positiva si la tensión correspondiente al "1"

lógico es mayor que la tensión del "0" lógico. En caso contrario, se trata de una

lógica negativa. La mayoría de las veces, el "0" lógico es la masa o tensión de

0 voltios. Los niveles de tensión utilizados vienen determinados por la

tecnología empleada en la fabricación de circuitos.

Puertas básicas

De la definición de álgebra de Boole, las puertas básicas son:

Puerta AND

La salida es 1 si y sólo si todas y cada una de las variables de entrada

toman el valor 1. La puerta AND realiza la función producto lógico de las

variables de entrada:

y = x1 · x2 · ... · xn

Representación gráfica:

Tabla de verdad:

a

b

AND

0

0

1

1

0

1

0

1

0

0

0

1

Ejemplo de aplicación:

Habilitar / impedir el paso de alguna señal. Si el cinturón de seguridad no

está abrochado, se activa una de las entradas, pero mientras el coche no esté

en marcha no nos avisará. Al arrancar, activamos la otra entrada, y una alarma

o mensaje nos advertirá de que debemos colocarnos el cinturón.

13

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

Puerta OR

La salida es 1 si y sólo si al menos una de las entradas toma el valor 1.

La puerta OR realiza la función de suma lógica:

y = x1 + x2 + ... + xn

Representación gráfica:

Tabla de verdad:

a

b

OR

0

0

1

1

0

1

0

1

0

1

1

1

Ejemplo de aplicación:

Un sistema de alarma, en el que tenemos varios sensores en puertas y

ventanas. En el momento en que cualquiera de los sensores detecte la

presencia de un intruso, el valor de la función OR será "1", y podría activar un

circuito de alarma (sirena, etc.).

Puerta NOT (inversor)

y = x'

Representación gráfica:

Tabla de verdad:

a

NOT

0

1

1

0

Ejemplo de aplicación:

Realizar el complemento a 1 de un número binario, con una serie de

inversores en paralelo, tantos como bits utilizados en el número binario.

14

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

Puerta NAND

La salida es 0 si y sólo si todas y cada una de las entradas toman el

valor 1. En el resto de caos, la salida es 1. Equivale a una puerta AND seguida

de una puerta NOT. Realiza la función:

y = (x1 · x2 · ... · xn)' = x1' + x2' + ... + xn'

Representación gráfica:

Tabla de verdad:

a

b

NAND / Neg-Or

0

0

1

1

0

1

0

1

1

1

1

0

La puerta NAND (AND+NOT) es equivalente a la puerta llamada

negativa-OR (NOT+OR). El uso de una u otra puerta depende de si nos

interesa detectar todas las entradas a nivel alto (NAND) o alguna a nivel bajo

(Negativa-OR). Recordar los teoremas de De Morgan.

Ejemplo de aplicación:

En un proceso de fabricación tenemos dos tanques A y B de líquido, con

sensores de nivel que se activan por nivel alto ("1"), es decir, cuando el nivel es

igual o supera al del sensor. Tenemos dos posibilidades:

Queremos que se nos encienda un testigo de color verde (LED

conectado a +V) en un panel de control en el caso de que el nivel de los dos

tanques esté por encima de unos valores correctos: NAND.

Queremos que se nos encienda un testigo de color rojo (LED conectado

a GND) en un panel de control en el caso de que el nivel de cualquiera de ellos

descienda por debajo de un determinado nivel: Negativa-OR.

Es decir, cuando la salida de estas puertas es 1 (3 casos) se enciende el

LED rojo, y cuando es 0, se enciende el LED verde.

15

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

Puerta NOR

La salida es 0 si y sólo si al menos una de las entradas toma el valor 1.

Equivale a una puerta OR seguida de una puerta NOT. Realiza la función:

y = (x1 + x2 + ... + xn)' = x1' · x2' · ... · xn'

Representación gráfica:

Tabla de verdad:

a

b

0

0

1

1

0

1

0

1

NOR / Neg-AND

1

0

0

0

La puerta NOR (OR+NOT) es equivalente a la puerta llamada negativaAND (NOT+AND). El uso de una u otra puerta depende de si nos interesa

detectar alguna de las entradas a nivel alto (NOR) o todas a nivel bajo

(Negativa-AND). Recordar los teoremas de De Morgan.

Ejemplo de aplicación:

Monitorizar el tren de aterrizaje de un avión. Este dispone de tres

mecanismos: rueda delantera y ruedas en las dos alas. Queremos que se

encienda una luz verde si, tras pulsar el interruptor de "bajar el tren de

aterrizaje", los tres mecanismos está correctamente extendidos, y una luz roja

si alguno de ellos ha fallado. Cuando uno de los mecanismos se extiende, el

sensor genera una corriente a nivel bajo; cuando se retrae, genera una

corriente a nivel alto.

El circuito sólo se alimentará al pulsar el botón de "bajar el tren de

aterrizaje". Las tres señales serán las entradas de dos puertas lógicas, una

NOR, que encenderá el LED Rojo, y una Negativa-AND que encenderá el LED

Verde

Realmente son dos puertas NOR, sólo que una de ellas funciona como

una puerta Negativa-AND, para detectar un nivel bajo de los sensores

(extendidos).

Cuando los tres sensores están a nivel bajo (extendidos), la puerta

Negativa-AND tiene como salida un nivel alto, que enciende el LED verde

(conectado a GND).

Si alguno de los tres sensores está nivel alto (retraidos), la puerta NOR

tiene salida a nivel bajo, que enciende el LED rojo (conectado a +V).

Es decir, cuando la salida de estas puertas es 0 (3 casos) se enciende el

LED rojo, y cuando es 1, se enciende el LED verde.

16

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

Puerta XOR (OR-Exclusiva)

Una puerta XOR de 2 variables de entrada es tal que la salida toma el

valor 1 cuando las dos entradas son diferentes, y toma el valor 0 cuando son

iguales. Sólo tiene 2 entradas.

Se representa por el símbolo ⊕.

Representación gráfica:

Tabla de verdad:

a

b

XOR

0

0

1

1

0

1

0

1

0

1

1

0

La función se expresa en forma canónica como:

y = (x1' · x2) + (x1 · x2') = (x1 + x2) · (x1' + x2')

La definición para más de 2 entradas es compleja, pero puede obtenerse

la expresión de la función en forma canónica fácilmente, sabiendo que la

función OR-exclusiva tiene la propiedad asociativa:

y = x1 ⊕ x2 ⊕ ... ⊕ xn = (((x1 ⊕ x2) ⊕ x3) ⊕ ... ⊕ xn)

Esta puerta se utiliza bastante en muchos circuitos, como los

generadores de paridad.

Ejemplo de aplicación: Suma de dos bits sin acarreo (semisuma).

Puerta XNOR (NOR-exclusiva)

Equivale a una puerta OR-exclusiva seguida de una puerta NOT, por

tanto, también tiene sólo 2 entradas.

Representación gráfica:

Tabla de verdad:

a

b

0

0

1

1

0

1

0

1

XNOR

1

0

0

1

17

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

Implementación de funciones con puertas NAND o NOR

Hasta ahora hemos visto que cualquier función lógica podía definirse

utilizando solamente las operaciones de complementación, suma y producto

(puertas NOT, AND y OR).

Vamos a ver ahora que cualquier función lógica (sistema digital) puede

implementarse solamente con puertas NAND, o bien con puertas NOR. Por

ello, a las puertas NAND y NOR se las conoce como puertas universales. Para

ello, es suficiente obtener las puertas básicas, implementándolas con puertas

NAND o NOR, es decir, debemos demostrar que es posible derivar las puertas

NOT, AND y OR utilizando únicamente puertas NAND, y luego, puertas NOR.

Las puertas básicas (NOT, AND y OR) pueden obtenerse con puertas

NAND de la siguiente forma:

Puerta

Función

básica

f = x’ = (x · x) '

NOT

f = x’ = (x · 1) '

Esquema

ó también

(el símbolo de una puerta NAND con

una sola sola entrada no es válido)

AND

f = x1 · x2 = (x1 · x2) ''

(complementando dos veces)

OR

f = x1 + x2 = (x1 + x2) '' = (x1' · x2') '

(complementando dos veces y

aplicando el teorema de De Morgan)

Este procedimiento nos lleva a un número excesivo de puertas,

pudiéndose simplificar a continuación el circuito. De todas formas, si se quiere

implementar una función con puertas NAND o NOR, lo más inmediato es

modificar la expresión algebraica de la función mediante los teoremas de De

Morgan.

18

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

Ejemplo:

Como ejemplo, vamos a implementar con puertas NAND y NOR una

función expresada en forma de suma de productos (F1) y otra expresada en

forma de productos de sumas (F2):

F1 = (a · b · c) + (a' · b · c') + (a' · b' · c')

F2 = (a + b + c)' ' · (a' + b + c)' ' · (a + b' + c')' '

Puertas NAND

(I)

Sumas de productos

F1 = (a · b · c) + (a' · b · c') + (a' · b' · c') =

= ( (a · b · c) + (a' · b · c') + (a' · b' · c') ) ' ' =

= ( (a · b · c)' · (a' · b · c')' · (a' · b' · c')' ) '

Lo que hemos hecho es complementar dos veces las función entera, con

lo cual la función sigue siendo equivalente. A continuación, aplicamos el

teorema de De Morgan, que convierte el complemento de una suma en el

producto de los complementos. Así obtenemos una expresión en la que sólo

tenemos productos seguidos de negaciones (NAND).

(II)

Productos de sumas

F2 = (a + b + c)' ' · (a' + b + c)' ' · (a + b' + c')' ' =

= (a' · b' · c')' · (a · b' · c')' · (a · b' · c')'

En este caso simplemente hemos aplicado el teorema de De Morgan a

cada uno de los términos.

Puertas NOR

(I)

Sumas de productos

F1 = (a · b · c) + (a' · b · c') + (a' · b' · c') =

= (a · b · c)' ' + (a' · b · c')' ' + (a' · b' · c')' ' =

= (a' + b' + c') ' + (a + b' + c) ' + (a + b + c) '

Hemos complementado dos veces cada uno de los sumandos, y luego

aplicamos De Morgan para transformar los productos en suma de negaciones.

(II)

Productos de sumas

F2 = (a + b + c)' ' · (a' + b + c)' ' · (a + b' + c')' ' =

= ( (a + b + c)' ' · (a' + b + c)' ' · (a + b' + c')' ' )' ' =

= ( (a + b + c)' ' ' + (a' + b + c)' ' ' + (a + b' + c')' ' ') ' =

= ( (a + b + c)' + (a' + b + c)' + (a + b' + c')' ) '

19

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

3.4. Métodos de simplificación de funciones

Hemos visto como dos funciones con expresiones algebraicas diferentes

eran equivalentes. Sin embargo, existen numerosas funciones con expresiones

diferentes equivalentes a dichas funciones. De entre ellas, habrá algunas que

poseerán un número menor de productos y sumas. Debemos buscar la más

sencilla, para simplificar procesos posteriores como el de diseñar un circuito

lógico para dicha función.

El proceso de simplificación de funciones lógicas consiste en pasar de

una expresión algebraica a otra equivalente con el menor número posible de

sumas y productos.

3.4.1 Simplificación mediante propiedades del álgebra de

Boole.

Este método requiere un profundo conocimiento del álgebra booleana y

una considerable experiencia en su aplicación.

Las propiedades más utilizadas para la simplificación de funciones son:

•

Distributiva:

+ respecto ·: a + (b·c) = (a + b) · (a + c)

· respecto +: a · (b+c) = (a · b) + (a · c) ∀ a,b,c ∈ B

•

∀ a ∈ B, ∃ ! a' ∈ B tal que:

a + a’ = 1

a · a’ = 0

•

Ley de absorción:

a + (a·b) = a

a · (a+b) = a

•

Teoremas de De Morgan

Ejemplos

1. F = (a·b'·c'·d) + (a·b'·c'·d')

Aplicamos la propiedad distributiva:

(a·b'·c'·d) + (a·b'·c'·d') = a·b'·c' · (d+d') = a ·b'·c' · 1 = a·b'·c'

De esta forma hemos reducido dos sumandos de 4 variables a uno solo

de tres variables.

20

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

2. F = (a+b'+c'+d) · (a+b'+c'+d')

Podemos aplicar las mismas propiedades que antes, en su versión dual.

(a+b'+c'+d) · (a+b'+c'+d') = (a+b'+c') + (d · d') =

= (a+b'+c') + 0 = (a+b'+c')

3. F = a·b + a·(b+c) + b·(b+c)

Comenzamos aplicando la propiedad distributiva.

a·b + a ·(b+c) + b·(b+c) = a·b + (a·b + a·c) + (b·b + b·c) =

= a·b + a ·c + b + b·c = a·b + a·c + b = a·c + b

Hemos terminado aplicando dos veces la propiedad 10.

4. Función F1 del ejemplo anterior

F1 = (a' · b · c') + (a' · b · c) + (a · b · c') + (a · b · c) =

= (a' · b) · (c' + c) + (a · b) · (c' + c) =

= (a' · b) · 1 + (a · b) · 1 = (a' · b) + (a · b) =

= (a' + a) · b = 1 · b = b

5. Función F2 del ejemplo anterior

F2 = (a + b + c) · (a + b + c') · (a' + b + c) · (a' + b + c') =

= (a + b + (c' · c)) · (a' + b + (c · c')) =

= (a + b + 0) · (a' + b + 0) = (a + b) · (a' + b) =

= (a · a') + b = 0 + b = b

Podemos comprobar que en los dos últimos ejemplos hemos llegado a la

misma expresión simplificada. Anteriormente habíamos visto que ambas

expresiones eran equivalentes. De este ejemplo no debe sacarse la

conclusión de que una expresión en suma de productos y otra equivalente

como producto de sumas, tras simplificar, conducen a la misma expresión.

Esto, en general, no es cierto.

El método de simplificación algebraica se utiliza poco, pues tiene varios

inconvenientes:

• No es sistemático (requiere ingenio y destreza).

• En una expresión compleja, es difícil detectar todas las posibles

simplificaciones.

• En la mayoría de los diseños, una función se define por su tabla de

verdad, debiendo obtener la expresión algebraica para poder

simplificarla.

21

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

3.4.2 Mediante tablas de Karnaugh

Un mapa de Karnaugh es una forma de presentar la tabla de verdad de

tal manera que la disposición de las combinaciones de valores es

particularmente útil, de tal forma que la simplificación de una determinada

expresión consiste en agrupar adecuadamente las celdas.

La forma de la tabla dependerá del número de variables independientes

con las que estemos trabajando. Los mapas de de Karnaugh pueden utilizarse

para expresiones de hasta 5 variables. En el caso de tener más de 5 variables,

tendríamos que recurrir a otro método que no vamos a ver, llamado método de

Quine-McClusky.

El número de celdas de un mapa de Karnaugh es igual al número total

de posibles combinaciones de las variables de entrada, al igual que el número

de filas de una tabla de verdad: 2 n.

Una sola variable (a):

Sólo habrá dos símbolos de entrada: 1 y 0. La tabla de Karnaugh tendrá

dos casillas, en donde el 0 indica el valor de 0 de entrada y el 1 indica el valor 1

de entrada. Para el proceso de simplificación que veremos a continuación,

conviene numerar las casillas según un criterio, aunque no es obligatorio. Para

ello pondremos un índice en la esquina superior derecha, comenzando desde

el 0.

a

0

0

a'

1

1

a

Puesto que esta tabla contiene todos los posibles valores de entrada,

cualquier función de una variable puede representarse en este diagrama,

asignando a cada casilla el valor que toma la función para el valor de la

variable de entrada indicada.

Por ejemplo, si la función es F(a) = a' tendremos la tabla:

a

0

1

1

0

22

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

Dos variables (a,b):

Ahora la tabla de Karnaugh debe contemplar las cuatro posibles

combinaciones de las variables: (0,0), (0,1), (1,0), (1,1).

a\b

0

1

0

0

1

a'·b'

a'·b

2

1

3

a·b'

a·b

El valor de una determinada celda es el valor binario de las dos variables

a y b, comenzando por la parte izquierda y luego la parte superior.

Sea la función F(a,b) = a + b. La representaremos del siguiente modo.

a\b

0

1

0

0

1

1

1

1

Tres variables (a,b,c):

Se puede representar de forma horizontal o vertical. En este caso y en

los restantes (con más variables), la forma de numerar las casillas depende de

la combinación que represente una determinada columna o fila, y para etiquetar

una determinada columna o fila hay que realizarlo de tal forma que el cambio

de una combinación a la siguiente sólo varíe un bit.

a \ bc

00

01

0

0

a'·b'·c'

1

a'·b'·c

4

1

a·b'·c'

11

3

a'·b·c

5

a·b'·c

10

2

a'·b·c'

7

a·b·c

6

a·b·c'

El código cíclico empleado para las combinaciones de filas y columnas

es algo importante. Como resultado de este código, las casillas que tienen en

común un lado corresponden a combinaciones que difieren en el valor de una

23

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

variable y se dice que son adyacentes; las casillas que tocan diagonalmente

alguna de sus esquinas no son adyacentes. Las casillas adyacentes son

clave en el proceso de simplificación.

La adyacencia se define por un cambio de una única variable. Las

celdas que difieren en una única variable son adyacentes. Las celdas cuyo

valor difiere en más de una variable no son adyacentes.

En la determinación de casillas adyacentes es necesario, para el caso

de tres variables, considerar el diagrama de Karnaugh como una superficie

cilíndrica en que los lados izquierdo y derecho están unidos. Siendo así, la

celda 0 es contigüa a 2, y la celda 4 es contigua a 6.

Cuatro variables (a,b,c,d):

La tabla será, de nuevo, cíclica, donde los lados izquierdo y derecho

están unidos, y de la misma forma, el superior e inferior.

Las variables a y b se encuentran en la parte izquierda, mientras que las

variables c y d en la parte superior.

El valor de una determinada celda es el valor binario de a y b en la parte

izquierda de la misma fila, combinado con los valores binarios de c y d en la

parte superior de la misma columna.

ab \ cd

00

01

0

00

11

1

10

3

2

a'·b'·c'·d'

4

5

7

6

01

12

13

15

14

11

8

10

9

11

10

a·b'·c·d'

Dos celdas son adyacentes si sólo cambia un dígito, aunque no lo sean

físicamente. Son adyacentes de extremo a extremo. Por ejemplo, son

adyacentes los siguientes pares de celdas:

0-8, 0-2, 1-9, 3-11, 2-10, 12-14, 8-10, 4-6

24

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

Cinco variables (a,b,c,d,e):

Al igual que en el caso de 4 variables, se pueden solapar las partes

laterales. Aquí se pueden solapar las partes extremas: laterales izquierda y

derecha, y superior e inferior.

Además, en este caso tenemos un eje central que actúa de espejo, de

tal forma que la celda 3 es adyacente con la celda 7. Para comprobarlo, se ven

las combinaciones y se observa que sólo cambia un bit.

ab \ cde

00

000

001

011

010

110

111

101

100

0

1

3

2

6

7

5

4

01

8

9

11

10

14

15

13

12

11

24

25

27

26

30

31

29

28

10

16

17

19

18

22

23

21

20

En definitiva, podemos sacar las siguientes conclusiones:

•

Las tablas consideradas establecen una correspondencia biunívoca entre

los valores de las variables de la función y el conjunto de casillas del

diagrama de Karnaugh.

•

Cada combinación de valores de las variables representa un término

canónico (producto o suma), es decir, existe también una correspondencia

entre el conjunto de los términos canónicos y el conjunto de las casillas de

la tabla de Karnaugh. Por ejemplo, para cuatro variables, la combinación

(0,0,0,0) representa:

Ø el producto canónico:

Ø la suma canónica:

•

a' · b' · c' · d' (de forma directa)

a + b + c + d (de forma complementada)

Las celdas que tienen un lado común son adyacentes, y corresponden a

términos canónicos que difieren en sólo el valor de una de las variables.

25

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

Construcción de una tabla de Karnaugh

Podemos construir una tabla de Karnaugh desde la expresión lógica

(suma de productos o producto de sumas), o bien, desde una tabla de verdad.

Vamos a explicar todos estos casos basándonos en el siguiente ejemplo

que ya vimos anteriormente.

Sea la función F definida por la tabla de verdad siguiente:

a

0

0

0

0

1

1

1

1

b

0

0

1

1

0

0

1

1

c

0

1

0

1

0

1

0

1

F

0

0

0

1

0

1

1

0

Mintermus (m) Maxtermus (M)

M0 = a+b+c

M1 = a+b+c'

M2 = a+b'+c

m3 = a'·b·c

M4 = a'+b+c

m5 = a·b'·c

m6 = a·b·c'

M7 = a'+b'+c'

Valor

0 = 000

1 = 001

2 = 010

3 = 011

4 = 100

5 = 101

6 = 110

7 = 111

Por tanto, las expresiones lógicas equivalentes "suma de productos" y

"producto de sumas" y compactas serían:

F = ∑ (3,5,6) = (a'·b·c) + (a·b'·c) + (a·b·c')

F = Π (0,1,2,4,7) = (a+b+c) · (a+b+c') · (a+b'+c) · (a'+b+c) · (a'+b'+c')

q

Desde la expresión lógica

La forma de construcción de la tabla de Karnaugh depende de la forma

de la expresión que tengamos (suma de productos o producto de sumas).

En ambos casos, la expresión debe estar expresada en forma canónica,

es decir, todos sus términos son canónicos (contienen todas las variables).

Podemos ver también la forma compacta que representa cada caso, poniendo

entre paréntesis los números de las combinaciones de que hacen cierta la

expresión lógica. Veremos algún ejemplo en el siguiente punto.

Dada una función con "n" variables, la construcción de la tabla de

Karnaugh correspondiente se efectúa indicando mediante un "1" o un "0" las

celdas que corresponden a términos canónicos que forman parte de la función,

y dejando en blanco las casillas correspondientes a los términos que no forman

parte de la función.

Partiendo de la expresión en su forma canónica, procedemos como

sigue.

26

Estructura de computadores

q

Tema 3: Representación y minimización de funciones lógicas

Desde la expresión "suma de productos":

Introduciremos un "1" en el mapa de Karnaugh por cada término

producto (mintermus) de la expresión. Consideramos los valores binarios de las

variables del término de forma directa (sin complementar).

En las casillas correspondientes a dichas combinaciones colocaremos

1's, pues consideramos los casos en los que la función es cierta; y para que

esto ocurra, por lo menos uno de los términos debe ser cierto (es una suma), y

para que un término (producto) sea cierto, todas sus variables deben ser

ciertas.

Siguiendo con el ejemplo, la expresión "suma de productos" es:

F = ∑ (3,5,6) ó también

F = (a'·b·c) + (a·b'·c) + (a·b·c') ==> 011 + 101 + 110 (directos)

Vamos a construir la tabla de Karnaugh:

a\bc

00

01

11

0

1

4

5

2

3

1

0

1

10

7

1

6

1

Podemos comprobar que hemos colocado un "1" en las casillas

correspondientes a las combinaciones indicadas por los términos canónicos de

la función compacta. El resto de casillas podemos poner "0" ó dejarlas en

blanco.

Otro ejemplo:

F = a'·b'·c' + a'·b'·c + a·b·c' + a ·b'·c'

000

001

110

100

a \ bc

00

01

0

1

1

1

1

11

10

1

27

Estructura de computadores

q

Tema 3: Representación y minimización de funciones lógicas

Desde la expresión "producto de sumas":

En este caso introduciremos un "0" en el mapa de Karnaugh por cada

término suma (maxtermus) de la expresión.

Aquí, los valores binarios de las variables de los términos van

complementados, ya que estamos considerando los valores que hacen que la

función sea falsa (0); y para que esto ocurra, basta con que uno de los términos

sea falso (es un producto), y para que un término (suma) sea falso, basta con

que una de sus variables sea falsa. Consideramos los valores binarios que

hacen falso cada término.

Siguiendo con el ejemplo, la expresión "producto de sumas" es:

F = Π (0,1,2,4,7) ó también

F = (a+b+c) · (a+b+c') · (a+b'+c) · (a'+b+c) · (a'+b'+c') ==>

==> 000 · 001 · 010 · 100 · 111 (complementados)

La tabla de Karnaugh del ejemplo ahora será:

a \ bc

00

01

0

0

0

10

3

5

7

0

4

1

11

1

0

2

0

6

0

Podemos comprobar que hemos colocado un "0" en las casillas

correspondientes a las combinaciones indicadas por los términos canónicos de

la función compacta: F = Π (0,1,2,4,7). El resto de casillas podemos poner "1" ó

dejarlas en blanco.

Otro ejemplo:

F = (a+b+c) · (a+b'+c) · (a'+b'+c) · (a'+b+c')

000

010

110

101

a \ bc

00

0

0

1

01

11

10

0

0

0

28

Estructura de computadores

q

Tema 3: Representación y minimización de funciones lógicas

Desde la tabla de verdad:

Recordemos que una tabla de verdad proporciona la salida de una

expresión lógica para todas las posibles combinaciones de las variables de

entrada. Lo único que tenemos que hacer es trasladar los "1" o los "0" de la

columna de salida (F) de la tabla de verdad directamente al mapa de Karnaugh,

a las celdas correspondientes a los valores asociados de las combinaciones de

variables de entrada.

Es el caso más sencillo, pues trabajamos de forma directa. Podemos

implementar por "1" (considerando los 1's) o por "0" (considerando los 0's). Lo

más rápido es considerar aquel que tenga menos ocurrencias, rellenar la tabla

de Karnaugh para dicho valor y finalmente rellenar el resto de casillas con el

otro valor o dejarlas en blanco.

Para el ejemplo tenemos aquí los dos casos:

a\bc

00

01

0

11

1

4

5

1

00

2

1

0

1

a\bc

10

3

0

0

1

0

6

7

1

01

0

11

1

10

3

0

4

2

0

5

7

0

6

Implementando por “1”: considerando los valores que hacen que la

función sea cierta (1). El resto de casillas podemos dejarlas en blanco o poner

"0".

Implementando por “0”, considerando los valores que hacen que la

función sea falsa (0). El resto de casillas podemos dejarlas en blanco o poner

"1".

NOTA: Independientemente de como hayamos construido la tabla de

Karnaugh (implementando por "1" o por "0"), después, para el proceso de

simplificación, podremos obtener la función simplificada como suma de

productos (implementando por "1")

o como producto de sumas

(implementando por "0").

29

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

Mecanismo de simplificación

Si dos celdas adyacentes están marcadas con 1, tenemos dos términos

canónicos que difieren sólo en una variable, que además, dicha variable

aparecerá como directa (valor 1) en un término canónico y como

complementada (valor 0) en el otro término. Podemos agrupar las dos celdas

adyacentes produciendo un único término canónico en que falta justo esa

variable en que diferían. Vamos a ver el mecanismo de simplificación:

1. Construir la tabla de Karnaugh adecuada según el número de variables,

indicando con un "1" y con "0" las celdas que correspondan.

2. Seleccionar la forma final que tendrá la función simplificada: suma de

productos (implementando por "1" ) o producto de sumas (implementando

por "0"). En los siguientes pasos suponemos que implementamos por "1".

3. Agrupar celdas adyacentes marcadas con "1". Primero, grupos de 2 unos

que no pueden formar grupos de 4. Luego formar grupos de 4 unos que no

pueden formar un grupo de 8, etc. Interesa buscar los grupos más

numerosos, para obtener el menor número de grupos posible. Cada celda

de un grupo tiene que ser adyacente a una o más celdas del mismo grupo,

pero no todas las celdas del grupo tienen que ser adyacentes entre si.

Además un "1" puede estar en varios grupos a la vez.

4. Tomar todas las celdas con "1" que no se pueden agrupar con ninguna

otra como grupos de un "1" (aislados).

5. Cuando se hayan considerado todos los "1" se ha finalizado el proceso. Los

grupos de "1" conseguidos y los "1" aislados son los términos que

expresarán la función lógica en una forma irreducible.

Este proceso de simplificación no es único, pudiéndose obtener por

tanto varias formas irreducibles de la misma función, dependiendo de las

distintas agrupaciones que podemos realizar.

Una vez realizadas las agrupaciones, para obtener la expresión de la

función lógica irreducible, realmente lo que haremos es utilizar de forma

sistemática las propiedades:

(a · b · c) + (a' · b · c) = (a + a') · b · c = 1 · b · c = b · c

(a + b + c) · (a' + b + c) = (a · a') + b + c = 0 + b + c = b + c

Es decir, las variables que aparecen complementadas y sin

complementar dentro del mismo grupo se eliminan (variables contradictorias).

NOTA: Siempre que un mapa de Karnaugh sea un tablero de ajedrez en

el que la casilla de la esquina inferior derecha sea un 0, la solución es la ORExclusiva (XOR) de las variables (F = a·b' + a'·b = a ⊕ b). Si dicha casilla es un

1, la solución es la OR-Exclusiva negada (XNOR) de las variables (F = a·b +

a'·b' = (a ⊕ b)'.

30

Estructura de computadores

Tema 3: Representación y minimización de funciones lógicas

Ejemplo: Sea la función F vista anteriormente. Como es suma de productos

implementamos por “1” (de forma directa) para construir la tabla de Karnaugh:

F = a'·b'·c' + a'·b'·c + a·b·c' + a ·b'·c'

000

001

110

100

Hacemos las agrupaciones, sobre su tabla de Karnaugh. Como

queremos obtener una suma de productos, implementamos por “1”:

a \ bc

00

01

0

1

1

1

1

11

10

1

La expresión irreducible será:

F = (a’ · b') + (a · c')

Ejemplo: Sea la siguiente tabla de Karnaugh obtenida directamente desde la

tabla de verdad siguiente, implementando por “1” o por "0" (no importa):

a

b

c

F

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

0

0

1

0

1

1

0

•

F = Σ (3,5,6)

Su tabla de Karnaugh será:

a \ bc

00

01

0

0

0

1

0

11

1

0

4

1

5

1

2

0

7

0

Implementando por "1" (suma de productos):

No podemos asociar ningún grupo de "1" que sea de 2, 4 u 8.

Por tanto, la función simplificada será:

F = (a'·b·c) + (a·b'·c) + (a·b·c')

Casilla 6

Casilla 5

Casilla 3

•

10

3

Implementando por "0" (producto de sumas):

No tenemos grupos de 8 ni de 4 "0".

Grupos de 2 "0":

casillas 0-1, 0-4, 0-2

"0" aislados:

casilla 7

31

6

1

Estructura de computadores

Tema 3

La función simplificada será:

F = (a+b) · (b+c) · (a+c) · (a'+b'+c')

Casilla 7

Grupo 0-2

Grupo 0-4

Grupo 0-1

Ejemplo: Sea la función F(a,b,c,d) = ∑ (0,4,5,7,8,9,13,15), construimos su tabla

de Karnaugh (implementando por “1”) y vamos a obtener la función simplificada

en forma de suma de productos (implementando por "1").

ab \ cd

00

01

00

11

10

1

3

2

4

5

7

6

15

14

11

10

1

1

1

12

11

10

01

0

1

13

1

1

8

1

9

1

Agrupando y simplificando según el mecanismo obtendríamos:

F = (b·d) + (a'·c'·d') + (a'·b'·c')

Grupo 2: 8,9

Grupo 2: 0,4

Grupo 4: 5,7,13,15

Dependiendo de las agrupaciones que hagamos, podríamos haber

obtenido otras formas irreducibles de la función, pero no todas serán la mínima.

Ejemplo: Sea la función F(a,b,c,d) = ∑ (5,6,9,10), construimos su tabla de

Karnaugh (implementando por “1”) y vamos a obtener la función simplificada

como producto de sumas (implementando por "0").

ab \ cd

00

01

0

00

0

01

0

11

0

10

0

11

1

0

4

0

5

1

12

7

13

6

1

15

0

9

1

2

0

0

0

8

10

3

14

0

11

0

10

1

32

Estructura de computadores

Tema 3

Si implementásemos por "1" (suma de productos), vemos que no

podemos agrupar, pues no hay celdas con "1" adyacentes. Esto quiere decir

que no se puede reducir, y su forma mínima como suma de productos es:

F = (a'·b·c'·d) + (a'·b·c·d') + (a·b'·c'·d) + (a·b'·c·d')

Agrupando por "0" y simplificando según el mecanismo obtendríamos la

función como producto de sumas:

F = (c+d) · (c'+d') · (a'+b') · (a+b)

Grupo 4: 0,1,3,2

Grupo 4: 12,13,15,14

Grupo 4: 3,7,15,11

Grupo 4: 0,4,12,8

Esta expresión contiene sólo 8 letras, en lugar de las 16 de la forma

suma de productos y es, por tanto, mínima.

Como conclusión, una función lógica o booleana puede representarse y

simplificarse, tanto en su expresión como suma de productos, como en la de

producto de sumas, mediante una tabla de Karnaugh.

Indiferencias en el mapa de Karnaugh

Algunas veces se producen situaciones en las que algunas

combinaciones de las variables de entrada no están permitidas o no están

determinadas para un problema concreto, ó bien, no nos importa la salida para

dichas combinaciones. Estos casos los llamaremos indiferencias, ó términos

indiferentes. Los representaremos por 'x'.

Esto significa que a estos términos les podemos asignar "1" ó "0".

Hemos visto que las funciones lógicas se pueden expresar de forma

compacta como suma de productos canónicos o producto de sumas

canónicas. En el primer caso considerábamos los casos en los que se cumple

la función ("1"), y en el segundo, los casos en los que la función es falsa ("0").

Ahora tenemos un tercer valor que nos puede aparecer en la función de salida.

Para representar una función en forma compacta que tiene indiferencias

en la salida hacemos lo siguiente:

Forma de la expresión Forma compacta

suma de productos

F = ∑ ( Combinaciones ciertas ) +

d ( Combinaciones indiferentes )

producto de sumas

F = Π ( Combinaciones falsas ) ·

d ( Combinaciones indiferentes )

donde "d(Combinaciones indiferentes)" representa una lista de las

combinaciones indiferentes de la función. En el caso de la "suma de

productos", las combinaciones van de forma directa. En el caso del "producto

de sumas", las combinaciones van complementadas, incluso las indiferentes.

33

Estructura de computadores

Tema 3

Ejemplo

Como ejemplo vamos a analizar el código BCD.

Hay muchas formas de representar datos numéricos en forma binaria.

Una puede ser escribir el número en base 2, que se denomina codificación

binaria directa. Otra forma es codificar los números decimales dígito por dígito.

Esta codificación se denomina BCD (Binary-Coded-Decimal). Hay varios tipos

de códigos BCD, pero en general, se trata simplemente de sustituir cada dígito

decimal (0-9) por su equivalente binario.

En BCD, al igual que en la codificación binaria directa, necesitamos 4

bits. Por tanto, el número de combinaciones posibles es 24 = 16. Sin embargo,

para el código BCD sólo utilizamos 10. Las 6 restantes combinaciones binarias

no se pueden dar en esta codificación.

Por ejemplo, para codificar el número decimal 469 en BCD:

4 6 9 10 = 0100 0110 1001 2-BCD

Vamos a diseñar un circuito que teniendo como código de entrada BCD,

encienda un foco de luz cuando tengamos la combinación BCD

correspondiente al 9 decimal.

Para ello, lo primero que hacemos es construir su tabla de verdad.

a

b

c

d

F

a

0

0

0

0

0

0

0

0

0

0

1

1

0

1

0

1

0

0

0

0

0

0

0

0

1

1

1

1

0

0

1

1

0

1

0

1

0

0

0

0

1

1

1

1

0

0

0

0

0

0

1

1

0

1

0

1

0

1

x

x

1

1

1

1

1

1

1

1

0

0

1

1

0

1

0

1

x

x

x

x

b

F

c

9

d

F = Σ(9) + d(10,11,12,13,14,15)

Su salida nos es indiferente.

No se pueden dar en el

código BCD.

34

Estructura de computadores

Tema 3

Implementando por “1”:

Haciendo uso de las indiferencias vamos a simplificar aun más la

función. Para ello construimos la tabla de Karnaugh, implementando por “1” (es

lo más rápido, pues sólo tenemos una combinación):

Sin utilizar términos indiferentes:

cd

ab

00

01

11

10

00

01

11

10

0

0

0

0

0

0

0

0

x

x

x

x

0

1

x

x

a · b' · c' · d

Sólo tenemos un "1" aislado (no podemos agrupar nada), por tanto, la

función no se puede simplificar, es decir, obtendríamos que: F = a·b'·c'·d

Utilizando términos indiferentes:

Los términos indiferentes (x) pueden utilizarse para aprovechar mejor el

método del mapa de Karnaugh, por que les podemos dar el valor que nos

interese para formar los grupos tan grandes como sea posible, pues cuanto

más grande sea el grupo, más simple será el término resultante. Utilizando los

términos indiferentes como si fueran "1" obtenemos una función más sencilla.

cd

ab

00

01

11

10

00

01

11

10

0

0

0

0

0

0

0

0

x

x

x

x

0

1

x

x

a·d

NOTA: debemos agrupar todos los 1's o 0's, utilizando "x", pero todas las

casillas con "x" no tienen por qué incluirse en un grupo.

Podemos realizar un grupo de 4 "1", con lo cual:

F=a·d

35

Estructura de computadores

Tema 3

Implementando por “0”

Construimos la tabla de Karnaugh del mismo modo que antes, es decir,

implementando por "1" ya que sólo tenemos una combinación, pero ahora

implementaremos por "0" a la hora de la simplificación (agruparemos "0").

Pondremos las condiciones indiferentes donde correspondan ("x"), y en el resto

de casillas pondremos "0".

Sin utilizar términos indiferentes:

cd

ab

00

01

11

10

00

01

11

10

0

0

0

0

0

0

0

0

x

x

x

x

0

1

x

x

a

a' + b + c + d

La expresión irreducible que obtenemos es:

F = a · (a'+b+c+d)

Utilizando términos indiferentes:

cd

ab

00

01

11

10

00

01

11

10

0

0

0

0

0

0

0

0

x

x

x

x

0

1

x

x

a

d

Tenemos dos grupos de 8.

Por tanto, la expresión irreducible es: F = a · d

Podemos observar que obtenemos la misma expresión irreducible, al

implementar por “1” y por “0” cuando tenemos en cuenta las indiferencias,

aunque esto, en general, no es así.

Como vemos, las expresiones se simplifican mucho más, y, por tanto, la

construcción del circuito. El inconveniente de estos circuitos es que si estos

estados indiferentes apareciesen, la reacción del circuito sería imprevisible.

36

Estructura de computadores

Tema 3

3.5. Funciones incompletas

Funciones incompletas

Las funciones incompletas o incompletamente definidas son aquellas

que no tienen su salida definida para alguna de las combinaciones de entrada.

Suponemos que las salidas para dichas combinaciones de entradas es

"indiferente". Como hemos visto, estas combinaciones se utilizan para

simplificar las funciones mediante mapas de Karnaugh.

Conjuntos completos

Un conjunto de funciones es completo en un álgebra de Boole si y sólo si

cualquier función booleana puede implementarse con dichas funciones.

Ejemplos de conjuntos completos:

• { AND, OR, NOT }

• { OR, NOT }

≡ { NOR }

• { AND, NOT } ≡ { NAND }

Ejemplos de conjuntos no completos:

• { AND, OR }

Nivel de un circuito

Dado un circuito con una serie de puertas lógicas, puesto que por cada

una de estas puertas que la señal eléctrica atraviesa se produce un retraso

(tiempo de propagación), es importante especificar el número de puertas que

atraviesa la información de entrada hasta llegar a la salida.

Una puerta se considera de nivel i, donde i > 1, si y sólo si:

a) no recibe ninguna entrada de puertas de nivel j, con j > i.

b) tiene al menos una entrada procedente de una puerta de nivel i-1.

Un circuito lógico es de nivel i, si al menos contiene una puerta de nivel i,

y no contiene ninguna puerta de nivel j, siendo j > i.

Dicho de otro modo, el nivel de un circuito lógico será el nivel máximo de

las puertas.

El coste económico de un circuito dependerá del número de puertas.

La velocidad de un circuito dependerá del nivel de dicho circuito.

Hemos visto como podemos simplificar el diseño de un circuito,

reduciendo el número de puertas y, por tanto su coste, pero en ocasiones, a

costa de que el circuito tenga un nivel mayor, es decir, sea más lento.

37

Estructura de computadores

Tema 3

Ejemplo

Sea la función F = (a' + b + c') · (b + d) · (c' + b · a)

Vamos a implementarla con puertas NAND y NOR. Posteriormente,

vamos a simplificarla, volviendo a expresarla con puertas NAND y NOR. Con

esto podremos averiguar el número de puertas y nivel de los circuitos obtenidos

en cada caso.

Puertas NAND

F = (a' + b + c') · (b + d) · (c' + b · a) =

= (a' + b + c')' ' · (b + d)' ' · (c' + b · a)' ' =

= (a · b' · c)' · (b' · d')' · (c · (b · a)')'

Si dibujamos el circuito, obtendremos un circuito con 8 puertas y

de nivel 4.

Puertas NOR

F = (a' + b + c') · (b + d) · (c' + b · a) =

= ( (a' + b + c') · (b + d) · (c' + b · a) ) ' ' =

= ((a' + b + c')' + (b + d)' + ( c' + (b · a)'' )' ) ' =

= ((a' + b + c')' + (b + d)' + ( c' + (b' + a')' )' ) '

Si dibujamos el circuito, obtendremos un circuito con 8 puertas y

de nivel 4, igual que en el caso anterior (puertas NAND).

Simplificación

Para simplificar la función mediante tablas de Karnaugh debemos

expresar la función en forma canónica, esto es, todos sus términos deben ser

canónicos:

F = (a' + b + c') · (b + d) · (c' + b · a) = x · y · z

x = (a' + b + c') + (d · d’) = (a’+b+c’+d) · (a’+b+c’+d’)

y = (b + d) + (a · a’) = [ (a+b+d) · (a’+b+d) ] + (c · c’) =

(a+b+d+c) · (a+b+d+c’) · (a’+b+c+d) · (a’+b+c’+d)

z = (c' + (b · a)) + (d · d’) = (a · b + c’ + d) · (a · b + c’ + d’)

Como la función F es un producto de sumas, implementamos por “0”, es

decir, las combinaciones de cada uno de los términos que nos indican las

casillas en la tabla de Karnaugh van complementadas, es decir, consideramos

los casos en los que la función F es falsa, que lo será cuando lo sea cualquiera

de sus términos.

38

Estructura de computadores

Tema 3

Los términos serán falsos para cualquiera de las combinaciones

siguientes:

x = 1010, 1011

y = 0000, 0010, 1000, 1010

z = (a·b)10, (a·b)11

ab\cd

00

01

11

10

00

0

(Para que (a·b) sea 0 ==> a=0 ó b=0)

01

1

11

3

0

4

10

2

0

5

7

0

6

0

0

12

13

15

14

8

9

11

10

0

0

b+d

a+c'

ab\cd

00

01

11

0

b+c'

10

00

0

01

1

1

0

4

5

1

12

b · c'

0

1

c' · d

0

14

1

11

1

0

6

15

9

0

0

1

1

10

2

7

13

8

11

3

1

10

0

0

a·b

Implementando por “0”:

F = (b+d) · (a+c’) · (b+c’)

Si ahora transformamos la función irreducible obtenida para

utilizar sólo puertas NAND y NOR y dibujamos el circuito

equivalente obtenemos:

NAND: circuito con 8 puertas y nivel 4

NOR: circuito con 4 puertas y nivel 3

Implementando por “1”:

F = (b·c’) + (c’·d) + (a·b)

Del mismo modo, si ahora transformamos la función irreducible

obtenida para utilizar sólo puertas NAND y NOR y dibujamos el

circuito equivalente, en este caso obtenemos:

NAND: circuito con 5 puertas y nivel 3

NOR: circuito con 8 puertas y nivel 4

Vemos que hemos obtenido varias expresiones irreducibles. De todas

ellas, sólo una será mínima. En este caso, se ha conseguido al implementar

por 0 y luego transformar la expresión para utilizar sólo puertas NOR.

39

Estructura de computadores

Tema 3

Apéndice A – Circuitos Integrados

Circuito Integrado

Los circuitos digitales se construyen con circuitos integrados (IC). Un

IC es un pequeño cristal semiconductor de silicio, llamado informalmente chip ,

que tiene los componentes electrónicos de las puertas digitales. Las puertas se

interconectan en el chip para formar el IC.

El chip se monta en un contenedor de cerámica o plástico y se sueldan

sus conexiones (entradas y salidas) a las patillas externas para formar el IC.

La cantidad de patillas puede variar, dependiendo del tamaño del IC,

desde 14 hasta varios cientos. Cada IC tiene una etiqueta impresa en la

superficie exterior que lo identifica mediante una designación numérica. Con

esta referencia, podremos consultar sus características en los catálogos del

fabricante.

Niveles de integración

A medida que avanza la tecnología de los IC, ha aumentado

considerablemente la cantidad de puertas que pueden colocarse en un único

chip de silicio. Dependiendo de la escala de integración de los IC tendremos

más o menos puertas.

SSI (Small-scale integrated): menos de 10 puertas.

MSI (Medium-scale integrated): de 10 a 100 puertas.

LSI (Large-scale integrated): de 100 a miles de puertas.

VLSI (Very large-scale integrated): varios miles o millones de puertas.

Familias lógicas digitales

Los IC digitales se clasifican no sólo por su operación lógica, sino

también por la tecnología de circuito a la que pertencen. La tecnología se

conoce como familia lógica digital. Cada una de las familias tiene su propio

circuito electrónico básico (NAND, NOR, NOT), sobre el que se desarrollan

circuitos digitales y funciones más complejos. Los componentes electrónicos

utilizados en la construcción del circuito básico suelen dar su nombre a la

tecnología.

40

Estructura de computadores

Tema 3

Las familias lógicas de circuitos integrados más importantes son:

•

•

•

•

•

•

•

RTL (resistor-transistor logic)

DTL (diode-transistor logic)

TTL (transistor-transistor logic)

ECL (emitter-coupled logic)

MOS (metal-oxide semiconductor)

CMOS (complementary metal-oxide semiconductor)

BiCMOS (bipolar complementary metal-oxide semiconductor)

Parámetros de las familias lógicas

Para analizar las características de las distintas familias lógicas digitales

estudiamos unos parámetros de las puertas básicas de cada familia:

•

•

•

•

•

•

•

Márgenes de tensión de entrada y salida: estos valores determinan el

intervalo de cada uno de los niveles lógicos ("1"/H y "0"/L) de la

familia.

Márgenes de corriente de entrada y salida: los valores de tensión

anteriores están directamente relacionados con la corriente que entre

o salga de las patillas.

Convergencia de entrada (fan-in): número de entradas de una puerta.

Divergencia de salida (fan-out): nos indica el número de puertas

(cargas) que podemos conectar a la salida sin que afecte a su buen

funcionamiento. Nos indica el número de “cargas estándar” que

soporta la salida; una “carga estándar” es la cantidad mínima de

corriente que necesita una entrada de otra puerta.

Margen de ruido: es el voltaje externo de ruido máximo superpuesto

a una entrada normal sin que afecte a la salida del circuito.

Disipación de potencia: es la potencia consumida por una puerta,

gran parte de la cual de disipa como calor.

Retardo de propagación: es el tiempo necesario para que el cambio

de valor de una entrada se propague a la salida. La velocidad de

operación está en relación inversa con los retardos de propagación

más grandes.

Márgenes de tensión de entrada y salida

•

•

•

•

VIH = mínima tensión que se reconoce en una entrada como nivel alto

(H) o "1" lógico. En el caso de un inversor es el valor mínimo de la

tensión de entrada que produce un "0" a la salida.

VIL = máxima tensión que se reconoce en una entrada como nivel

bajo (L) o "0" lógico. En el caso de un inversor es el valor máximo de

la tensión de entrada que produce un "1" a la salida.

VOH = mínima tensión de la salida de una puerta cuando el nivel es

alto (para una corriente de salida especificada).

VOL = máxima tensión de la salida de una puerta cuando el nivel es

bajo (para una corriente de salida especificada).

41

Estructura de computadores

Tema 3

Gráficamente:

H

H

VOH

NM H

VIH

VIL

NML

VOL

L

L

Entrada

Salida

La zona rayada representa la zona de incertidumbre entre los dos

estados, es decir, aquellos valores que no se reconocen ni como "0" ni como

"1".

Márgenes de corriente de entrada y salida

•

•

•

•

IIH = corriente que fluye por una entrada cuando se aplica un voltaje

de nivel alto. Para V e = V OH è obtenemos el mínimo valor.

IIL = corriente que fluye por una entrada cuando se aplica un voltaje

de nivel bajo. Para V e = V OL è obtenemos el mínimo valor.