Los Transistores JFET y MESFET según SPICE

Anuncio

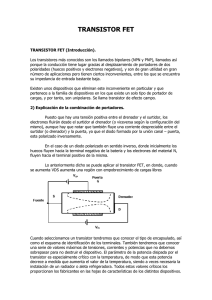

Los Transistores JFET y MESFET según SPICE G. González Díaz e I. Mártil de la Plaza (JFET), Equipo de NGSPICE (MESFET) d Traducido, adaptado y formateado por Francisco J. Franco 2 d ri El modelo usado por SPICE para el transistor JFET se denomina Parker-Skellern 1 y, para el MESFET, un modelo muy parecido llamado Statz . Ambos modelos consisten en un transistor RS , ( RS ) y RD RD3 ( M a intrínseco en serie con dos resistencias parásitas ). En las ecuaciones descrip- tivas del transistor que se verán a continuación, los potenciales se reeren al transistor intrínseco, las resistencias parásitas. Como es habitual, las corrientes se tomarán como e a posteriori positivas si entran en el dispositivo y negativas si salen. d añadiéndose la lu .e te s n se La expresión de las corrientes por los terminales de acuerdo con el modelo de la gura son: de IG = IGS + IGD p m (3) Corrientes de fugas en la puerta .u de 1. (2) c m o IS = − (IDS + IGS ) C alu m a d n os ID = IDS − IGD (1) w id Pa ra u so En un transistor MESFET, se supone que las corrientes de puerta en DC son, directamente, nulas. w w e rs Sin embargo, en un JFET las corrientes IGS e IGD se modelan como dos diodos. En ambos casos / iv se contemplan los efectos de generación-recombinación en la zona de vaciamiento y la posibilidad 1 Se :/ tt p U n de ionización por impacto. Según esto: IGS = IN RM + IREC ·KGEN + IREV (4) h describe el nivel por defecto de los transistores JFET. Algunas versiones de SPICE pueden implementar un segundo modelo modicado, llamado LEVEL =2, con sustanciales mejoras. Pueden consultarse las características en http://www.engineering.mq.edu.au/research/groups/cnerf/psfet.pdf 2 Este modelo es relativamente básico y se indica con LEVEL = 1. Aunque existen modelos más avanzados como los HFET, no se describirán debido a su inmadurez y poco uso en general. 3 Como viene siendo habitual, si un parámetro físico tiene un parámetro SPICE asociado, se pondrá a su lado resaltado en negrita. 1 M a d ri d Los transistores JFET y MESFET según SPICE IN es la corriente de Shockley, el segundo término el efecto generación-recombinación y el d donde e Figura 1: Modelo DC de un transistor JFET de canal N. lu .e te s n se tercero la corriente de avalancha. Las expresiones de los dos primeros términos son: VGS = IS · exp N ·VT de la IN RM C o KGEN = id + 0,005 4 y PB (7) IS ISR tienen su equivalente SPICE ( , , vale 2. que es la región de saturación directa, :/ IREV = IDRAIN ·α·VDIF ·exp − tt p n U NR #M/2 / 0 < VGS − VT 0 < VDS , iv 1. Para vale 1 y (6) IREV , que es la corriente de ionización por impacto, haremos los siguientes cálculos: e rs Pa ra u Para calcular N −1 2 IS , ISR , N , NR .u ). Por defecto, (5) w w y so , VGS NR ·VT −1 w de N NR PB VGS 1− PB c m " En estas ecuaciones, los parámetros p m alu m a d n os IREC = ISR · exp VK VDIF (8) h Para otros casos, En estas expresiones, IREV = 0 (9) VDIF = VDS − (VGS − VT 0 ). Los parámetros físicos que tienen expresión en SPICE son los siguientes: 2. VT 0 : Se expresa como 4 Potencial VT0 y no es sino la tensión de pinch-o del transistor JFET. Se calcula de contacto entre la puerta y el canal Electrónica Analógica Ingeniería Superior en Electrónica 2 Los transistores JFET y MESFET según SPICE de las características físicas del transistor JFET como: VT O = donde ND qND d² − PB 2·εSi (10) es el dopado del canal (supuesto de tipo N y con puerta mucho más dopada) y d su altura. 3. α: 4. VK : Es el coeciente de ionización por impacto y se simboliza como IGD ). (corriente de fugas entre puerta y drenador) se obtiene de la misma forma cam- d ri La corriente VK . d Tensión a partir de la cual aparece la avalancha ( ALPHA M a biando el terminal de fuente por el de drenador. Corriente de drenador a fuente (IDS ) Transistor JFET lu .e te s n se 2.1. d e 2. la La corriente de drenador se expresa en función de las tensiones de puerta-fuente y drenador-fuente p m (región de corte): (11) IDS = β ·VDS · [2· (VGS − VT O ) − VDS ] · (1 + λ·VDS ) (12) .u w w / :/ tt p (región de saturación): IDS = β · (VGS − VT O )2 · (1 + λ·VDS ) (13) h U id e rs iv VGS − VT O ≤ VDS n Si lineal): w VDS ≤ VGS − VT O (región Pa ra u c) IDS = 0 de Si so b) c m VGS − VT O ≤ 0 o Si C a) o modo normal: os VDS ≥ 0, alu m a d n 1. Si de de acuerdo con el modelo aproximado siguiente: 2. Para VDS < 0, o modo invertido, se deben cambiar la fuente por el drenador en las expresiones anteriores. Se han introducido dos parámetros nuevos muy importantes. En primer lugar, las ecuaciones tienen BETA β , representado en SPICE como , que es la transconductacia del transistor JFET. Otro término es λ, o coeciente de modulación del canal, que se simboliza en SPICE como 2 . El parámetro β tiene unidades de A/V y está relacionado con otro parámetro de los transistores un término DA Electrónica Analógica Ingeniería Superior en Electrónica LAMB3 Los transistores JFET y MESFET según SPICE reales, IDSS , a través de la ecuación IDSS = β VT2O (14) Este parámetro está relacionado con la corriente que atraviesa el transistor en saturación ya que la ecuación 13 puede convertirse en: IDS = IDSS · 1 − LAMBDA VGS VT O 2 · (1 + λ·VDS ) (15) es un parámetro que se introduce de forma empírica para modelar el acortamiento VDS (conductancia del canal), formalmente similar d ri de drenador presenta una pendiente frente a d del canal cuando el transistor está más allá del borde de saturación. Como se sabe la corriente en las ecuaciones del modelo, LAMBDA tiene unidades de V −1 M a (aunque la razón física es diferente) al efecto Early en un transistor bipolar. Tal como está expresado y correspondería con la inversa del potencial (en módulo) en el que se cortan las prolongaciones de las características de salida en Transistor MESFET la 2.2. lu .e te s n se d e saturación. de Estos transistores utilizan unos parámetros comunes al JFET pero en un modo más elaborado. Así, siguen vigentes los parámetros VT O VTO ( ), β BETA ( ) y λ ( LAMBDA ), con el mismo 5 2. Si VGS > VT O , VDS > h si 3. m o ( ALPHA ), ), relacionado con la forma de la zona dopada. En .u w / " :/ IDS ( α·VDS (VGS − VT O )2 = β· · 1− 1− 1 + Θ· (VGS − VT O ) 3 tt p n U b) 3 α w w e rs 0 < VDS < iv si id so Pa ra u a) Θ α c m VGS < VT O , IDS = 0. de 1. Si C alu m a d n o parámetro de la tensión de saturación , y estas circunstancias, B p os signicado que en el JFET. En cambio, se deben incorporar dos parámetros nuevos, 3 α IDS 3 # · (1 + λ·VDS ) (VGS − VT O )2 = β· · (1 + λ·VDS ) 1 + Θ· (VGS − VT O ) (16) (17) Capacidades Básicamente, las capacidades que aparecen en los transistores JFET están asociadas a la unión PN entre la puerta y el canal. En los transistores MESFET, la unión no es PN sino Schottky pero la 5 Como puede verse, no tiene nada que ver con el parámetro homónimo de los JFET, descrito en la página anterior. Electrónica Analógica Ingeniería Superior en Electrónica 4 Los transistores JFET y MESFET según SPICE descripción es similar a la que sigue. Por comodidad, se supone que la capacidad de unión de estos transistores se divide en dos partes que unen la puerta bien con el drenador, bien con la fuente. Obviamente, se sobreentiende que los contactos de la unión están más adentro del transistor que las resistencias parásitas RD RS y . A semejanza de las uniones PN, es necesario introducir un parámetro llamado FC , de valor por defecto es 1. De este modo 1. Capacidad entre puerta y fuente (CGS ). −M −(1+M ) VGS · 1 − F C · (1 + M ) + M · PB lu .e te s n se CGS = Area·CGS0 · (1 − F C) e VGS > F C · P B , Para (18) (19) d b) VGS PB M a CGS = Area·CGS0 · 1 − d VGS < F C · P B , Para d ri a) la 2. Capacidad entre puerta y drenador (CGD ). de VGD < F C · P B , p m o alu m a d n VGD > F C · P B , C Para .u de b) CGD = Area·CGD0 · 1 − c m Para os a) −(1+M ) w −M (20) VGD · 1 − F C · (1 + M ) + M · PB (21) w w id e rs Pa ra u so CGD = Area·CGD0 · (1 − F C) VGD PB En estas ecuaciones aparecen los siguientes parámetros SPICE: En primer lugar, un parámetro cuyo valor depende del carácter abrupto o gradual de la unión PN presente en el JFET. / M iv llamado :/ n En general, se toma 0.5 como valor por defecto. Asimismo, en los modelos que se pueden construir 0 V bien CGD0 CGD tt p U en SPICE, cada una de las capacidades de unión asociadas a la puerta tiene un valor a potencial de ( ), bien CGS0 CGS ( ). El último factor que aparece es Area. Su signicado es el h siguiente: Si construyéramos un JFET en un circuito integrado, podríamos caracterizarlo mediante una serie de aparatos y obtener sus parámetros SPICE. Sin embargo, podríamos construir un JFET con las mismas características pero con un área diferente. Ello conlleva una variación de estas capacidades. Para solucionarlo, se incorpora un parámetro a cada transistor en la descripción circuital conteniendo el área relativa del transistor especíco respecto al valor por defecto. Es un parámetro similar al de los transistores bipolares y, curiosamente, distinto de los transistores MOSFET, en los que hay que denir la anchura y longitud del canal. Electrónica Analógica Ingeniería Superior en Electrónica 5 Los transistores JFET y MESFET según SPICE 4. Efectos de la temperatura Debe reseñarse que el modelo del MESFET es tan simplicado que no se ha implementado en su descripción un comportamiento con la temperatura. Por ello, este apartado es aplicable solo a los JFET. En general, los parámetros que dependen de la temperatura son los siguientes: 1. Tensión de Pinch-o : VT 0 (T ) = VT O + VT 0T C · (T − TN OM ) pinch-o por K. 2. Transconductancia: β (T ) = β ·1,01βT CE (T −TN OM ) · ( BETATCE ) el parámetro característico. (23) e βT CE VT 0T C d siendo y d ri ) la variación de la tensión de en M a VT0TC ( TEMP .OPTIONS d donde, lógicamente, T es la temperatura declarada como (22) " lu .e te s n se 3. Corrientes de saturación inversa y de recombinación de las uniones PN: la T TN OM m o alu m a d n ISR (T ) = ISR ·exp " T p os de IS (T ) = IS ·exp # EG T −1 · · N ·q ·VT TN OM (24) # EG T · −1 · NR ·q ·VT TN OM TN OM I XT N I XT N R (25) C XTI EG no es un .u , ya explicados en el tema del diodo. Por otra parte, de parámetros como c m Expresiones en las que, aparte de los parámetros ya conocidos, se han incorporado otros w w e rs Pa ra u 4. Potencial de contacto: T / TN OM − 3·VT ·ln T TN OM − EG (TN OM ) · T TN OM + EG (T ) :/ iv P B (T ) = P B · n w id so parámetro denible en el modelo del JFET. Así, su valor es 1.11 eV y no es modicable. tt p U En este caso, SPICE corrige el ancho de la banda prohibida por medio de la ecuación EG (T ) = T2 . T +1108 h 1,16 − 0,000702· (26) 5. Capacidades de contacto a potencial nulo: " !# P B (T ) CGX (T ) = CGX · 1 + M · 1 − + 0,0004· (T − TN OM ) PB en la que CGX puede ser tanto Las resistencias parásitas, Electrónica Analógica RS RD y CGS como (27) CGD . , no tienen dependencia de la temperatura. Ingeniería Superior en Electrónica 6 Los transistores JFET y MESFET según SPICE 5. Ruido Como muchos dispositivos electrónicos, el ruido en un JFET 6 o MESFET consta de dos partes. Un ruido blanco asociado a las resistencias parásitas y otro coloreado de disparo y de centelleo o icker. El ruido es calculado asumiendo una anchura espectral de 1 Hz, con las siguientes densidades de potencia espectral de ruido. 1. Ruido térmico asociado a resistencias parásitas: (28) d RS Area d ri 2 ID = 4·k ·T 4·k ·T RD Area 2. Ruidos de otro tipo: (30) d e 2 I AF 2 = ·gm ·4·k ·T + KF · D ID 3 f (29) M a IS2 = ∂ID , f es la frecuencia de interés y ∂VGS y AF , simbolizados en SPICE como KF , los coecientes del ruido de centelleo. de C o 2N3819 c m m alu m a d n 6.1. p Ejemplos de transistores reales os 6. KF la AF y gm = lu .e te s n se donde Este modelo corresponde a un transistor JFET de canal N obtenido de las bibliotecas de LTSPICE- .u w w id / :/ n iv Is=33.57f Isr=322.4f N=1 Nr=2 Xti=3 Alpha=311.7u Vk=243.6 Cgd=1.6p M=.3622 Pb=1 2N5114 h 6.2. tt p Fc=.5 Cgs=2.414p Kf=9.882E-18 Af=1) U + + e rs Pa ra u 2.5m w 2N3819 NJF(Beta=1.304m Betatce=-.5 Rd=1 Rs=1 Lambda=2.25m Vto=-3 Vtotc=- so .model de IV. Modelo de transistor JFET de canal N obtenido de las bibliotecas de LTSPICE-IV .model 2N5114 PJF(Beta=510.2u Betatce=-.5 Rd=1 Rs=1 Lambda=40m Vto=-8.095 Vtotc=- 2.5m + Is=461.5f Isr=4.402p N=1 Nr=2 Xti=3 Alpha=32.54u Vk=393.2 Cgd=6.5p M=.2789 Pb=1 Fc=.5 6 Por otra parte, debe recordarse que, por construcción, los JFET son muy poco ruidosos. Electrónica Analógica Ingeniería Superior en Electrónica 7 Los transistores JFET y MESFET según SPICE + Cgs=9p Kf=32.96E-18 Af=1) 6.3. MESFET genérico No existen modelos comerciales de transistores MESFET. Por ello, se ofrece el modelo genérico desarrollado en NGSPICE. mesmod nmf (level =1 rd =46 rs =46 vt0 =-1.3 lambda =0.03 alpha =3 beta =1.4 e-3) p .u c m m o w :/ / w w id e rs tt p h U n iv Pa ra u so de C alu m a d n os de la lu .e te s n se d e M a d ri d .model Electrónica Analógica Ingeniería Superior en Electrónica 8