Practica No 1 - Electrónica Digital II. Prof.Zulay Franco (Unexpo

Anuncio

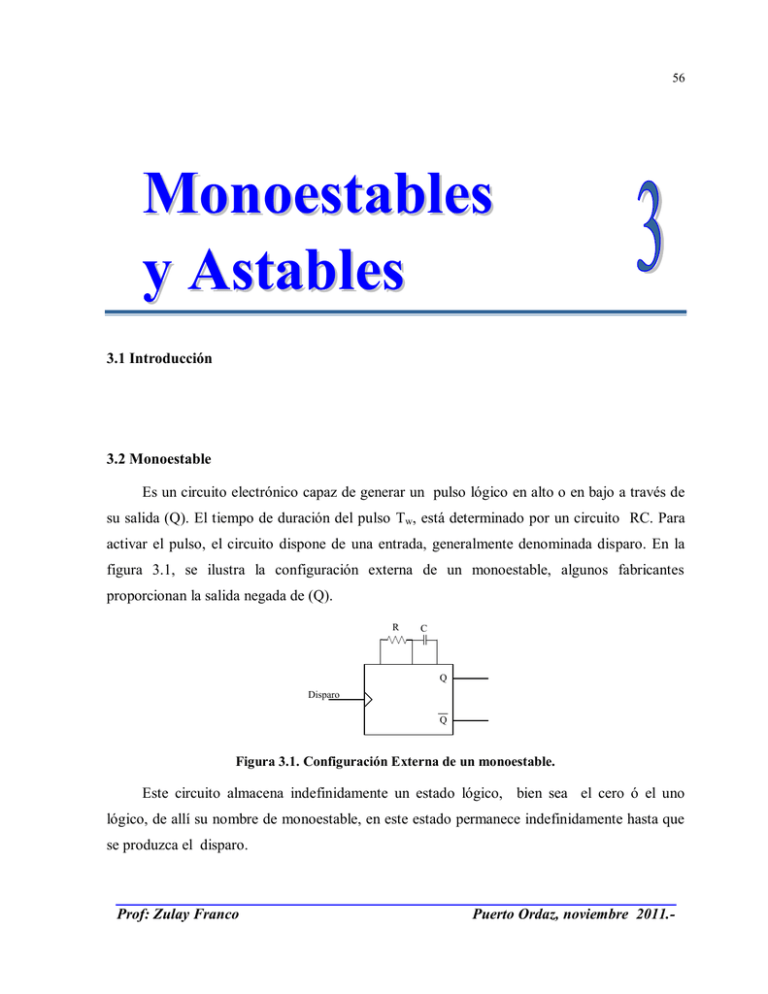

56 Monoestables y Astables 3.1 Introducción 3.2 Monoestable Es un circuito electrónico capaz de generar un pulso lógico en alto o en bajo a través de su salida (Q). El tiempo de duración del pulso Tw, está determinado por un circuito RC. Para activar el pulso, el circuito dispone de una entrada, generalmente denominada disparo. En la figura 3.1, se ilustra la configuración externa de un monoestable, algunos fabricantes proporcionan la salida negada de (Q). R C Q Disparo Q Figura 3.1. Configuración Externa de un monoestable. Este circuito almacena indefinidamente un estado lógico, bien sea el cero ó el uno lógico, de allí su nombre de monoestable, en este estado permanece indefinidamente hasta que se produzca el disparo. Prof: Zulay Franco Puerto Ordaz, noviembre 2011.- 57 Si bien hay curvas para el cálculo del tiempo de temporización Tw, este se puede calcular con mayor precisión empleando la expresión: Tw = KRC (1) La constante K es suministrada por el fabricante y en algunos casos se puede calcular. La entrada de disparo puede ser por flanco de subida o por flanco de bajada. figura 3.2 se puede observar el diagrama de tiempo de la respuesta del monoestable. Disparo Disparo Salida Tw Salida a) Tw b) Figura 3.2. Respuesta del monoestable. a) Activado por flanco de subida. b) Activado por flaco de bajada. 3.3 Clasificación de los monoestables Los monoestables se clasifican en no redisparable y redisparable. Los monoestables no redisparable son aquellos monoestable que comienza su temporización ( Tw ) una vez sea activada su entrada de disparo y su salida se encuentra en su estado estable. En la figura 3.3 se muestra la salida de un circuito monoestable no redisparable con la entrada de disparo activa por flanco de subida y el estado estable de la salida es el cero lógico. 1 2 3 Disparo Salida Tw Tw Figura 3.3. Respuesta del monoestable no redisparable disparado por flanco de subida. Prof: Zulay Franco Puerto Ordaz, noviembre 2011.- 58 En el punto 1 de la figura 3.3, se observa que cuando se tiene un flanco de subida en la entrada de disparo del monoestable y la salida del circuito se encuentra en su estado estable (Q=0), la salida del circuito se coloca en su estado inestable (Q=1) durante un tiempo Tw. En el punto 2 se observa que si durante este tiempo tw ocurre un flanco de subida en su entrada de disparo, el circuito hace caso omiso a este flanco y no comienza de nuevo la temporización Tw, En el punto 3 se observa que se comienza una nueva temporización, tw, ya que la salida del circuito se encuentra en su estado estable ( Q=0) y ocurre el flanco de subida. Los monoestables redisparable son aquellos monoestable que comienza su temporización ( Tw ) cada vez que se active su entrada de disparo, sin importar si la salida se encuentra en su estado estable ó inestable. En la figura 3.4 se muestra la salida de un circuito monoestable redisparable disparado por flanco de subida y el estado estable en la salida es el cero lógico. 1 2 3 Disparo Salida Tw Figura 3.4. Respuesta del monoestable redisparable disparado por flanco de subida. En el punto 1 de la figura 3.4, se observa que cuando se tiene un flanco de subida en la entrada de disparo del monoestable y la salida del circuito se encuentra en su estado estable (Q=0), la salida del circuito se coloca en su estado inestable (Q=1) durante un tiempo Tw. En el punto 2 y 3 se observa que si durante este tiempo t w ocurre un flanco de subida en su entrada de disparo, el circuito comienza de nuevo la temporización Tw. Prof: Zulay Franco Puerto Ordaz, noviembre 2011.- 59 3.4 Algunos circuitos integrados de tipo monoestables 74121: Monoestable no redisparable con entrada Schmitt Trigger. La configuración de sus pines y su tabla de funcionamiento se presenta en la figura 3.5. El circuito se puede disparar por flanco de subida (B) o por flanco de bajada (A1 ó A2), se configura por uno o por el otro según la tabla de funcionamiento suministrada por el fabricante. La entrada B de tipo Schmitt Trigger permite velocidades de transiciones del pulso de entrada tan bajas como 1v/seg. A continuación se ilustra la configuración de pines del integrado 74121 y su tabla de funcionamiento Figura 3.5. Pines y tabla de funcionamiento del monoestable 74121. El ancho del pulso es programable desde 30nseg a 28seg. Utilizando la resistencia interna (Rint), es decir colocando este pin a Vcc y dejando abiertas las entradas C ext y Rext/Cext se obtiene un pulso a la salida de 30 nseg o 35 nseg típicos. Utilizando Rext/Cext se puede obtener pulso desde pocos nseg hasta 28seg. Para Cext < 1000 pF el ancho de pulso está determinado por los valores dados por la curva de la figura 3.7. Prof: Zulay Franco Puerto Ordaz, noviembre 2011.- 60 Figura 3.7. Duración del ancho del pulso en función de Rext y Cext Para Cext ≥ 1000 pF la salida está definida como: TW = K RextCext donde Rext es en KΩ Cext es en pF Tw es en nseg y K≈ 0,7 El coeficiente K no es constante varía según el capacitor, como puede verse en la figura 3.8. Prof: Zulay Franco Puerto Ordaz, noviembre 2011.- 61 Figura 3.8. Valor K en función del capacitor En la figura 3.9, se puede observar las condiciones de operación recomendadas por el fabricante. Figura 3.9. Condiciones de operación recomendadas por el fabricante Prof: Zulay Franco Puerto Ordaz, noviembre 2011.- 62 74LS123 y 74123: Monoestable redisparable. La configuración de sus pines y su tabla de funcionamiento se presenta en la figura 3.10. El circuito se puede disparar por flanco de subida (B) o por flanco de bajada (A), se configura por uno o por el otro según la tabla de funcionamiento suministrada por el fabricante, el pulso comienza cuando detecta un flanco en la entrada de disparo (A ó B). Figura 3.10. Pines y tabla de funcionamiento para el 74123 ó 74LS123. 74LS123 En la figura 3.11 se puede observar la conexión del condensador y la resistencia externa a los terminales del 74LS123. Vcc Rext C Terminal Cext Terminal Cext/Rext Figura 3.11. Conexión a los terminales del 74LS123 Prof: Zulay Franco Puerto Ordaz, noviembre 2011.- 63 En la figura 3.12, se puede observar las condiciones de operación recomendadas por el fabricante para el 74LS123. Figura 3.12. Condiciones de operación recomendadas por el fabricante para 74LS123 Para Cext<1000 pF el ancho de pulso está determinado por los valores dados por la curva de la figura 3.13. Prof: Zulay Franco Puerto Ordaz, noviembre 2011.- 64 Figura 3.13. Duración del ancho del pulso en función de Rext y Cext PARA 74LS123 Para Cext ≥ 1000 pF la salida está definida como: TW = K RextCext donde Rext es en KΩ Cext es en pF Tw es en nseg y K≈ 0,37 El coeficiente K no es constante varía según el capacitor, como puede verse en la figura 3.14 Prof: Zulay Franco Puerto Ordaz, noviembre 2011.- 65 Figura 3.14. Valor K en función del capacitor Por otra parte, si se utiliza un condensador con polaridad el terminal negativo del condensador debe estar conectado al pin "CEXT" del dispositivo como se muestra en la figura 3.15, donde se presenta la conexión para obtener un ancho de pulso de TW, cuando es configurado para activarse o dispararse por flanco de bajada. Figura 3.15. Conexión del integrado 74LS123 para obtener un ancho de pulso de tw Prof: Zulay Franco Puerto Ordaz, noviembre 2011.- 66 74123 En la figura 3.16 se puede observar la conexión del condensador y la resistencia externa a los terminales del 74123. Vcc Rext C Terminal Cext Terminal Cext/Rext Figura 3.16. Conexión a los terminales del 74123 En la figura 3.17, se puede observar las condiciones de operación recomendadas por el fabricante para el 74123. Prof: Zulay Franco Puerto Ordaz, noviembre 2011.- 67 Figura 3.17. Condiciones de operación recomendadas por el fabricante para 74123 Para Cext<1000 pF el ancho de pulso está determinado por los valores dados por la curva de la figura 3.18. Prof: Zulay Franco Puerto Ordaz, noviembre 2011.- 68 Figura 3.18. Duración del ancho del pulso en función de Rext y Cext para 74123 Para Cext ≥ 1000 pF la salida está definida como: TW = K RextCext (1+07/Rext) donde Rext es en KΩ Cext es en pF Tw es en nseg y K≈ 0,28 Como ejemplo de aplicación de este monoestable redisparable, veamos el siguiente problema: Se necesita implementar un circuito que sea capaz de detectar cuando se produce la caída de una línea de señal digital de clock cuya frecuencia es de 100KHz. Para diseñar el circuito requerido podemos emplear un monoestable redisparable el cual se dispare permanentemente con alguno de los dos flancos de la señal de clock que hay que testear. El periodo de la señal de clock es de 1/100KHz ó 10us. Si ajustamos el tiempo de TW a un valor superior a 10us, la salida del mismo estará permanentemente en alto ( si empleamos pulso positivo) ya que siempre aparecerá un flanco que dispare al monoestable. Solamente Prof: Zulay Franco Puerto Ordaz, noviembre 2011.- 69 bajará cuando al haber pasado los T W segundos no se haya presentado otro flanco de la señal de clock, lo cual significará que la misma ha caído. 555: Este componente se puede configurar mediante componentes externos como monoestable ó como astable. Se puede observar en la figura 3.19, su configuración interna. Figura 3.19. Configuración interna del Circuito Integrado 555 Pines: 1.- Tierra 2.- Entrada de disparo, normalmente debe estar a 1 lógico, al producir el disparo el voltaje debe caer por debajo de 1/3 Vcc y se activa la entrada SET del biestable. 3.- Pin de Salida 4.- Pin de reset, activo en bajo. Prof: Zulay Franco Puerto Ordaz, noviembre 2011.- 70 5.- Pin de control, a través de este pin se puede modificar los voltajes de comparación. 6.- Voltaje umbral, el voltaje debe estar por encima de 2/3 Vcc para activar la entrada RESET del biestable. 7.- Pin de descarga permite que un condensador ( C ) se cargue y se descarga. 8.- Voltaje de alimentación. En la figura 3.20 se presenta el C.I 555 en su configuración como monoestable. Vcc Disparo 1 8 2 7 1K Pulsador R 555 Salida 3 Salida 6 TW 4 5 C 0,01 uF 2/3 vcc 0V b) a) Figura 3.20. a) C.I 555 en su configuración como monoestable. b) Diagramas de tiempo de la entrada de disparo, salida y de la carga y descarga del condensador. Realicemos el análisis del circuito monoestable de la figura 3.20, basado en la configuración interna del 555 mostrada en la figura 3.19. Al activar el pulsador de la figura 3.20, el voltaje en el pin 2 es menor que 1/3 de Vcc, entonces: la entrada SET del biestable se activa, la salida del 555, pin 3, se coloca en 1 lógico, el transistor se corta y el condensador comienza a cargarse a través de la resistencia R. Cuando el valor del voltaje del condensador es mayor a 2/3 de Vcc, entonces la entrada de RESET del biestable se activa, la salida va a cero lógico, el transistor conduce y el condensador se descarga a través de él (ver figura 3.20). Por tanto después del disparo la salida permanece en 1 lógico en un tiempo igual al tiempo que tarda el condensador en cargarse a 2/3 de Vcc. Ver la parte b) de la figura 3.20. Prof: Zulay Franco Puerto Ordaz, noviembre 2011.- 71 El tiempo de duración del pulso Tw se puede determinar según la ecuación 2, que es la ecuación de carga de un condensador, −𝑡 𝑉𝑐 = 𝑉𝑓 − 𝑉𝑓 − 𝑉0 𝑒 𝑅𝐶 (2) donde Vc=2/3 de Vcc, Vf= Vcc y Vo= 0V. −𝑇𝑊 2 𝑉𝑐𝑐 = 5 − 5 − 0 𝑒 𝑅𝐶 3 −𝑇𝑊 2 𝑉𝑐𝑐 = 5 − 5𝑒 𝑅𝐶 3 𝑒 −𝑇𝑊 𝑅𝐶 =1− 2 3 𝑇𝑊 = −𝑅𝐶 ln (1/3) 𝑇𝑊 = 1,1𝑅𝐶 (3) Consideraciones: El voltaje de la entrada de disparo (pin 2), debe estar normalmente en alto y al disparar el voltaje en este pin debe estar por debajo de 1/3 de Vcc. El ancho del pulso de disparo debe ser menor que la duración del pulso TW, pues si el disparo es mayor se tendrá activa la entrada de SET y RESET del biestable, y la salida caerá a 0 lógico solo al desaparecer el disparo. Asignación: Consultar ene el manual tiempo máximo de temporización, valor máximo del condensador y de la resistencia. Prof: Zulay Franco Puerto Ordaz, noviembre 2011.- 72 74xx14: Para generar un pulso de un ancho TW, utilizando el 74xx14 se debe presionar y liberar el pulsador del circuito mostrada en la figura 3.21. Vcc Entrada Vcc Vt+ R Pulsador Salida 0V 74xx14 C Salida TW b) a) Figura 3.21. a) Circuito utilizado el C.I 74xx14 para obtener un pulso de duración de Tw b) Diagramas de tiempo de la descarga y carga del condensador y de la salida Modo de funcionamiento: Inicialmente el condensador, C, se encuentra cargado a un voltaje igual a Vcc, es decir se tiene un uno lógico en la entrada del 74xx14 y a la salida se tiene un cero lógico. Al presionar el pulsador el condensador se descarga, aplicando así un cero lógico en la entrada y obteniéndose un 1 lógico a la salida. Al liberar el pulsador la salida permanece en 1 lógico durante un tiempo (TW,) igual al tiempo que tarda el condensador en cargarse a través de la resistencia R desde el voltaje inicial 0V hasta el voltaje que el 74xx14 interpreta como uno lógico en la entrada, es decir VT+. Ver la parte b) de la figura 3.21. Para implementar este circuito es recomendable colocar una resistencia para descargar el condensador como se muestra en la figura 3.22. Prof: Zulay Franco Puerto Ordaz, noviembre 2011.- 73 Vcc Entrada Vcc Vt+ R1 Pulsador R2 Salida Vo C Salida TW Figura 3.22. a) Circuito utilizado el C.I 74xx14 para obtener un pulso de duración de Tw b) Diagramas de tiempo de la descarga y carga del condensador y de la salida Para este caso al presionar el pulsador el condensador se descarga a un voltaje, Vo dado por la expresión: Vo R2 * Vcc R2 R1 (4) Este valor de voltaje debe ser menor ó igual que VT- , valor indicado por el fabricante del 74xx14 para tener un 0 lógico aplicado en la entrada, y así garantizar que se tendrá un uno lógico en la salida. Al liberar el pulsador la salida permanece en 1 lógico durante un tiempo (TW,) igual al tiempo que tarda el condensador en cargarse a través de la resistencia R1 desde el voltaje inicial Vo hasta el voltaje que el 74xx14 interpreta como uno lógico en la entrada, es decir VT+. Ver la parte b) de figura 3.22. El tiempo de duración del pulso Tw se puede determinar según la ecuación (2), que es la ecuación de carga de un condensador, t Vc V f (V f Vo ) e RC Donde Prof: Zulay Franco Puerto Ordaz, noviembre 2011.- 74 Vo=Voltaje que tiene el condensador cuando comienza la carga, 0V si no tiene resistencia de descarga y viene dado por la ecuación 4, cuando se le coloca la resistencia de descarga. Vc= Voltaje del condensador para el tiempo Tw, es decir VT+; Vf=Voltaje al cual tiende a cargarse el condensador, es decir Vcc Luego remplazando en la ecuación de carga tenemos, TW VT Vcc (Vcc Vo ) e R1C TW (VT Vcc ) e R1C (Vcc V0 ) TW (Vcc VT ) e R1C (Vcc Vo ) TW (Vcc VT ) Ln R1C (Vcc Vo ) (Vcc VT ) TW R1C Ln ( Vcc V ) o (5) Considerando R1>> R2, el voltaje inicial, V o se puede asumir de 0V, quedando la ecuación 4 de la siguiente forma. 𝑉𝑐𝑐 − 𝑉𝑡+ 𝑇𝑊= − 𝑅1𝐶 𝑙𝑛 𝑉𝑐𝑐 (6) 3.5 Astable Circuito electrónico que no tiene un estado lógico estable en su salida (Q). Son los llamados osciladores, donde la frecuencia de oscilación va depender de una red RC. Este tipo Prof: Zulay Franco Puerto Ordaz, noviembre 2011.- 75 de circuito no dispone de una señal de entrada de disparo externa. La expresión para calcular la frecuencia de oscilación viene dada por la expresión 7, como sigue: F 1 , (7) T Donde T es el periodo de la señal y es igual a T= t alto+ t bajo (8) 74xx14: En la figura 3.23 se presenta la implementación de un astable utilizando 74xx14. VOH R Salida VOL t1 t2 Vt+ C Vt- a) b) Figura 3.23. a) Circuito utilizado el C.I 74xx14 para obtener un pulso de duración de Tw. b) Diagramas tiempo de la salida y de la carga y descarga del condensador Modo de funcionamiento Comencemos el análisis suponiendo que inicialmente el condensador, C, se encuentra cargado a un voltaje igual a VT -, es decir se tiene un cero lógico en la entrada del 74xx14 y a la salida se tiene un uno lógico, VOH. Como el voltaje del condensador es menor que VOH el condensador trata de cargarse a través de la resistencia R, al voltaje de salida, sin embargo cuando el condensador tiene un voltaje igual a VT+, el 74xx14 comienza a ver un uno lógico en la entrada y la salida se va a cero lógico, VOL. Para este instante de tiempo el voltaje del condensador es mayor que VOL y comienza a descargarse a través de la resistencia R, sin embargo cuando el condensador tiene un voltaje igual a VT-, el 74xx14 comienza a ver un cero Prof: Zulay Franco Puerto Ordaz, noviembre 2011.- 76 lógico en la entrada y la salida se va a uno lógico, en este punto se repite de nuevo el ciclo. La carga y descarga se puede observar en la figura 3.23. Para el cálculo de la frecuencia se debe determinar el periodo de la señal, y para ello se debe calcular el tiempo t1, que es el tiempo que tarda el condensador para cargarse desde VThasta VT+ y el tiempo t2 que es el tiempo que tarda el condensador para descargarse desde VT+ hasta VTEcuación de carga del condensador t1 Vc V f (V f Vo ) e RC Donde Vo=Voltaje que tiene el condensador cuando comienza la carga, es decir VTVc= Voltaje del condensador para el tiempo de t1= VT+ Vf=Voltaje al cual tiende a cargarse el condensador, es decir VOH Despejando t1 y remplazando valores en la ecuación de carga tenemos. t1 VT VOH (VOH VT ) e RC (VT VOH ) (VOH VT ) (VOH VT ) (VOH VT ) t1 e RC t1 e RC (V VT ) t 1 Ln OH RC (VOH VT ) (VOH VT ) t1 RC Ln (V V ) OH T Prof: Zulay Franco (9) Puerto Ordaz, noviembre 2011.- 77 Ecuación de descarga del condensador t 2 Vc V f (V f Vo ) e RC Donde Vo=Voltaje que tiene el condensador cuando comienza la descarga= VT+ Vc= Voltaje del condensador para el tiempo t2= VTVf=Voltaje al cual tiende a descargarse el condensador=V OL Despejando t2 y remplazando valores en la ecuación de descarga tenemos. t 2 VT VOL (VOL VT ) e RC (VT VOL ) (VOL VT ) (VOL VT ) (VOL VT ) t 2 e RC t 2 e RC (V VT ) t 2 Ln OL RC (VOH VT ) (VOL VT ) t 2 RC Ln (V V ) OL T (10) Remplazando t1 y t2 en la ecuación (8) Prof: Zulay Franco Puerto Ordaz, noviembre 2011.- 78 (V VT ) (V VT ) Ln OL T Ln OH RC RC ( V V ) ( V V ) OH T OL T (VOH VT ) (VOL VT ) T Ln RC Ln RC (V V ) ( V V ) OH T OL T T Ln (VOH VT ) (VOH VT ) RC (VOL VT ) (VOL VT ) (VOH VT )(VOL VT ) T RC Ln (V V )(V V ) OH T OL T (11) 555: : En la figura 3.24 se presenta la implementación de un astable utilizando el 555 Vcc 1 8 2 7 3 6 4 5 RA Salida t1 RB Vcc t2 D1 2/3 vcc C 0,01 uF 1/3 vcc a) b) Figura 3.24. C.I 555 en su configuración como astable. b) Diagramas tiempo de la salida y de la carga y descarga del condensador Realicemos el análisis del circuito astable de la figura 3.24, basado en la configuración interna del 555 mostrada en la figura 3.19. Cuando el voltaje del condensador es menor que 1/3 Vcc la entrada SET del biestable es activada y la salida, pin 3, se coloca en 1 lógico, el transistor, pin 7, se corta, y el condensador comienza a cargarse a través de la resistencia Prof: Zulay Franco Puerto Ordaz, noviembre 2011.- 79 RA+RB. Como el condensador también se encuentra conectado en la entrada umbral, pin 6 entonces cuando el valor de voltaje del condensador es mayor de 2/3 de Vcc la entrada de RESET del biestable se activa y la salida baja a cero lógico, el transistor conduce y el condensador comienza a descargue a través de la resistencia R B hasta llegar al voltaje menor a 1/3 Vcc donde se repite el ciclo descrito anteriormente. Para calcular estos tiempos se utilizan las ecuaciones de carga y descarga del condensador como sigue: Para calcular t 1 Ecuación de carga del condensador t1 Vc V f (V f Vo ) e( RA RB )C Donde Vo=Voltaje que tiene el condensador cuando comienza la carga= 1/3Vcc Vc= Voltaje del condensador para el tiempo de t1= 2/3Vcc Vf=Voltaje al cual tiende a cargarse el condensador= Vcc Despejando t2 y remplazando valores en la ecuación de carga del condensador tenemos:. 2 / 3Vcc Vcc (Vcc 1 / 3Vcc ) e t1 ( R A RB ) C t1 (1 2 / 3) e ( R A RB ) C (1 1 / 3) t1 (1 / 3) e ( R A RB ) C (2 / 3) t1 Ln(1 / 2) ( R A R B )C t1 0,693( R A R B )C Prof: Zulay Franco (12) Puerto Ordaz, noviembre 2011.- 80 Para calcular t 2 Ecuación de descarga del condensador t2 Vc V f (V f Vo ) e RBC Donde Vo=Voltaje que tiene el condensador cuando comienza la descarga= 2/3Vcc Vc= Voltaje del condensador para el tiempo t2= 1/3Vcc Vf=Voltaje al cual tiende a descargarse el condensador=0 Despejando t1 y remplazando valores en la ecuación de descarga del condensador tenemos:. t2 1 / 3Vcc 0 (0 2 / 3Vcc ) e RB C t 2 (1 / 3) e RB C (2 / 3) t 2 (1 / 2) e RB C t2 Ln(1 / 2) RB C t 2 0,693R B C (13) Remplazando t1 y t2 en la ecuación (8) Prof: Zulay Franco Puerto Ordaz, noviembre 2011.- 81 T 0,693( R A R B C 0,693R B C T 0,693R A 2 R B C F (14) 1 T La señal obtenida con el 555 no es simétrica, es decir el tiempo en alto es diferente al tiempo en bajo, el tiempo en alto depende de la carga del condensador a través de la resistencia (RA + RB) el tiempo en bajo depende de la descarga del condensador a través de la resistencia (RB). Para obtener una señal simétrica se debe colocar un diodo entre el pin 6 y el pin 7 y las resistencias RA y RB deben ser iguales para que el tiempo de carga y el tiempo de descarga del condensador también sea iguales como se muestra en la figura 3.25. El tiempo de carga, es decir el tiempo en alto (t 1) dado por la ecuación 12, solo va depender de R A. Vcc 1 8 RA Salida 2 7 3 6 4 5 RB D1 Vcc C 0,01 uF Figura 3.25. C.I 555 en su configuración como astable para obtener una señal simétrica Prof: Zulay Franco Puerto Ordaz, noviembre 2011.- 82 T 0,693R A C 0,693RB C pero R A RB R T 2(0,693RC ) (15) F 1 T Figura 3.23. C.I 555 en su configuración como astable para obtener una señal simétrica T 0,693RC 0,693RC T 2(0,693RC ) (15) F 1 T Monoestables y Astables (Ejercicios) 1- Calcule los valores de R y C para el circuito No. 1 para que entregue a la salida un pulso de 100 milisegundos después de pulsar y liberar SW1. Prof: Zulay Franco Puerto Ordaz, noviembre 2011.- 83 2.-Calcule los valores de R y C en el circuito No. 2 para obtener una frecuencia de 60 khz. 1. 3.- Diseñe un multivibrador monoestable con los CI :74221 y 74123 con un ancho de pulso de 500 milisegundos. 4.- Diseñe un multivibrador monoestable con el CI 555 con un ancho de pulso de 500 milisegundo. 5.-Diseñe un multivibrador astable con el CI 555 cuya frecuencia sea 1 Hz y tenga un ciclo útil del 70%. 6.-Realice el diseño de un monoestable de duración 400mseg, utilizando: 74123, 74121 y un LM555. Establezca la diferencia entre cada uno de ellos. 7.- Realice el diseño de un astable de 60Khz utilizando un 7414 y un 74LS14. Prof: Zulay Franco Puerto Ordaz, noviembre 2011.-