Diseño de Circuitos Integrados Digitales 2005. PROYECTO.

Anuncio

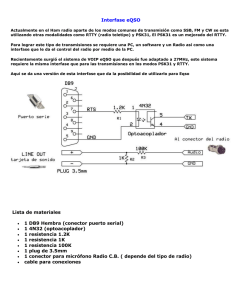

Diseño de Circuitos Integrados Digitales 2005. PROYECTO. OBJETIVO.- Se tienen un microcontrolador y un transmisor / receptor de radio configurable. Se quiere obtener un transceptor inteligente que cumpla con la norma IEEE 802.15.4 mediante la realización de un circuito de interfase entre ambos. CIRCUITO El circuito a diseñar se comunica con el micro controlador mediante un puerto SPI desde el cual recibe los bytes de configuración y control así como los datos a transmitir y usará dichos bytes para controlar y comunicarse con el transceptor. El transceptor funciona en la banda de 915 MHz., con un data rate de 40 Kb/s, modulación BPSK y usa DSSS como indica la norma. La interfase configura el transceptor, carga los datos a transmitir en una cola FIFO, arma el paquete físico (PPDU), codifica los datos, realiza el mapeo “Bit-to-Chip” entregando los bits serial izados al modulador y emitiendo las salidas de control hacia el transceptor. SEÑALES DE CONTROL Las señales de control consistirán en: 1) Prender / Apagar el oscilador a cristal de 16 MHz. 2) Habilitar el modo RX 3) Habilitar modo TX 4) Deshabilitar RX / TX y PLL. 5) Programar la frecuencia del PLL TRAMA De acuerdo a la norma el paquete PPDU deberá tener un preámbulo de sincronización de largo programable por el usuario, un delimitador de trama de 1 byte programable y una longitud de MPDU variable (ver norma IEEE 802.15.4). A los efectos de su realización práctica se divide el proyecto en tres partes: 1) Protocolo de la interfase SPI, registros de configuración y programación de dichos registros. 2) Cola FIFO, máquina de estados de la interfase. 3) Extracción de datos de la cola armado del paquete PPDU, codificación diferencial y conversión Bit - to - Chip. En una primera instancia los tres grupos trabajaran en forma conjunta para definir los tres bloques y sus interfases. Máquina de estados para controlar el transmisor PWR_ON Chip Reset cualquier estado SXOSC_OFF Apagado (PD) [0] Oscilador deshabilitado Acceso a registros habilitado Acceso a FIFO deshabilitado SXOSC_ON De todo estado excepto Apagado (PD) Esperar tiempo de arranque del oscilador o “pollear” el bit XOSC16M_STABLE del registro de status SRF_OFF STX_ON Tx completa TX_UNDERFLOW [4] underflow Comandos strobe IDLE [1] SXOSC_ON SXOSC_OFF STX_ON SRF_OFF TX_PREAMB [2] TX_FRAME [3] Prendido del oscilador Apagado del oscilador Prendido del transmisor Apagado de la RF La máquina de estados permite conmutar entre los diferentes estados de operación. Hemos distinguido 5 estados posibles, los cambios de estado pueden provenir de comandos strobe del micro (como SXOSC_ON) o bien originarse de la actividad interna (como transmisión completa o underflow). Interfase SPI.El puerto SPI trabaja con un reloj de 10 Mhz. SO Serial Output SI Serial Input SCLK Serial Clock CSn Chip Select negado SO SI SCLK CSn SLAVE Todas las transferencias de direcciones y datos en la interfase SPI comienzan con el MSB (Most Significant Bit). SCLK, SI y CSn son entradas de alta impedancia. SO es una salida que se pone en alta impedancia cuando CSn está alto. La tansmisión comienza cuando baja CSn y los datos se transfieren en la subida de reloj SCLK