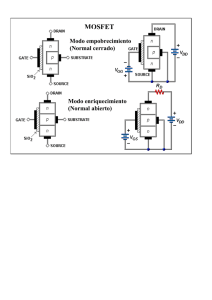

el mosfet de enriquecimiento canal n

Anuncio

40

ELECTRICIDAD

EL TRANSISTOR

DE EFECTO DE

CAMPO (FET)

Autor: Ing. Raúl Carrillo

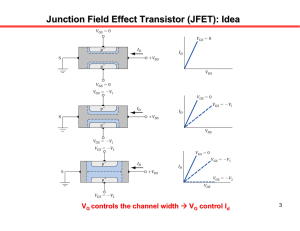

El FET es un dispositivo activo que opera como una fuente de corriente controlada por voltaje. Los más comunes son

los transistores de compuerta aislada

llamados MOSFET y los de compuerta

de unión llamados JFET. Posee cuatro

zonas de operación, óhmica o lineal,

saturación, corte y ruptura.

Desventajas

El Transistor de Efecto de Campo

(Field Efect Transistor) es un dispositivo semiconductor cuyo funcionamiento

se basa en el control de la corriente por

medio de un campo eléctrico. Estos

fueron propuestos inicialmente en su

versión JFET por W. Shockley en 1952.

• De puerta aislada, MOSFET (Metal Oxide - Semiconductor FET).

• De puerta de unión, MESFET o bien,

JFET ( junction FET).

• Alta impedancia de entrada 10 -10 [Ω]

• Ideal como etapa de entrada para

todo amplificador.

• Mejor estabilidad a To que el BJT.

• Niveles de ruido más bajo.

• Tecnología de fabricación más sencilla.

7

-12

Funcionamiento

De acuerdo con el diagrama de la figura 2 a, la compuerta está aislada por

FET

Puerta Aislada

Puerta de Unión

MOSFET

Enriquecimiento

JFET

Empobrecimiento

Canal N Canal P Canal N

D

D

D

G

G

G

S

S

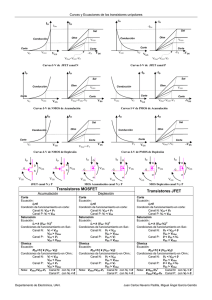

Figura 1. Tipos de FET

G

S

D

G

Sustrato

p

D

D

D

G

S

S

S

S

S

D

D

G

G

G

MESFET

Canal N Canal P

Canal P

D

D

n

n

Ventajas

También recibe el nombre de MOSFET

de Acumulación, Incremental o Acrecentamiento. El símbolo se muestra en

la figura 2 b. Si el sustrato está unido a

la fuente, se simplifica de acuerdo a la

figura 2 c - d.

Tipos de FET

Características Generales

El FET tiene tres terminales: Fuente

(Source), Drenador (Drain) y Compuerta (Gate). Este último es el terminal de control. El voltaje aplicado entre

la compuerta y la fuente controlará la

corriente entre la fuente y el drenador.

Es un dispositivo unipolar, pues, la corriente es transportada por portadores

de una polaridad, será canal N si la

corriente se debe a e¯, o canal P, si la

corriente se debe a h+.

EL MOSFET DE

ENRIQUECIMIENTO

CANAL N

• Respuesta en frecuencia no muy

aceptable, debido a su alta capacidad de entrada.

• No poseen buena linealidad.

• Muy sensibles a descarga s

electrostáticas.

G

G

S

S

S

Sustrato

a

b

c

d

Figura 2. (a) MOSFET canal n. (b) Símbolo. (c) Símbolo, sustrato unido a la fuente. (d) Símbolo abreviado del MOSFET.

ELECTROSECTOR | Septiembre 2016

ELECTRICIDAD

41

una película de SiO2 (dióxido de silicio); el transistor se polariza de acuerdo a la figura 3 a.

iD

D

G

+ v

DS

+

vGS

S

a

n

n

p

D

+

vDS

b

Figura 3. Polarización del MOSFET

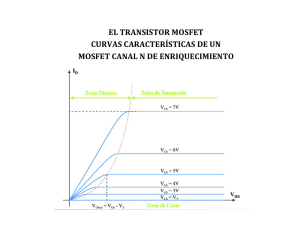

El análisis se realiza de acuerdo con

la variación del voltaje en la compuerta y el voltaje vDS. Para vGS = 0,

de acuerdo a la figura 4 a se observan dos junturas, sustrato-drenador

y sustrato-fuente, donde la primera

está polarizada inversa debido a vDS,

así iD = 0, por lo tanto se dice que el

transistor está en corte. El MOSFET

permanecerá en corte para valores

de vGS menores al voltaje umbral V T.

vG S = 0

iD

G

S

n

n

D

+

vDS

p

en la compuerta, de acuerdo con la figura 4 b, ésta atrae a los e¯ del sustrato

ubicado entre los terminales D y S , lo

que implica que dichos e¯ se acumulan

en la superficie inferior de la compuerta

(G), formándose un canal conductor tipo

n, produciéndose una corriente iD para

vGS > VT . Al aumentar levemente vDS, la

corriente iD aumenta de acuerdo a (1),

lo cual ocurre mientras vDS < (vGS - VT ).

distintos valores de vGS es posible

obtener distintas curvas iD - vDS, luego

para valores de vGS3 > vGS2 > vGS1 se tendrán las curvas de la figura 6 b.

iD [mA]

iD = k {2 (vGS - VT ) vDS - v2DS } (1)

Esta zona se conoce como zona óhmica o lineal, sin embargo, al aumentar

vDS, el canal se empieza a estrechar

hasta que se produce el estrangulamiento (pinch-off) como se indica en

la figura 4 c. Esto ocurre para valores

de vDS = vGS -VT. Dado que se produce

un aumento de la resistencia del canal,

para un nuevo aumento de vDS, el aumento de iD será pequeño, por lo tanto

el FET se encuentra en saturación y su

comportamiento estará dado por (2).

VT

S

iD = k (vGS - VT )2

iD

G

n - - - - -n-

D

+

vDS

p

b

vGS> VT

+

S

iD

iD

G

n

n

p

D

+

vDS < vGS - VT

v DS > v

GS

- VT

vDS> vGS _ TV

c

Figura 4. (a) vGS = 0. (b) Formación del canal

Ohmica

Saturación v

DS

n. (b) Estrangulamiento del canal.

Figura 5. Zona óhmica y saturación

Si se incrementa vGS, la tensión positiva

La curva iD-vGS se indica en la 6 a. Para

v

GS3

v

GS2

v

GS1

C orte

vDS

[V]

b

(2)

Donde k depende de la estructura física del FET. La curva indicada en la figura 5 muestra el comportamiento de

la ecuación (1) y (2) para un valor vGS

fijo mayor que V T , en función de vDS.

[V]

vGS

iD [mA]

a

vGS> VT

+

a

Región

Saturación

iD

G

S

Región

Óhmica

vGS

+

Figure 6. (a) Curva iD-vGS. (b) Curva iD-vDS del

MOSFET de acumulación.

Características del MOSFET

de enriquecimiento

• No existe IDSS:

• Se utilizan para fabricación de circuitos integrados.

• Requiere una vGS > 0.

• Para canal n, vT > 0 y vGS > 0; para

canal p, VT < 0 y vGS < 0:

Para vGS > vT ) iD = k (vGS - VT )2, donde

k es una constante dependiente del

método de fabricación, su dimensión

es

:

[ mA

]

V2

Septiembre 2016 | ELECTROSECTOR