Circuitos integrados adaptadores de comunicación serial más

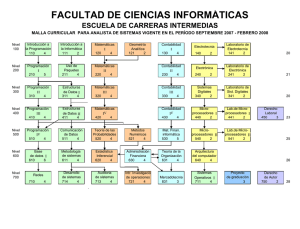

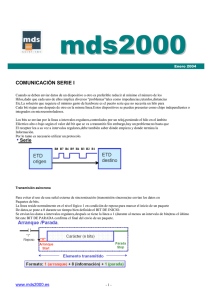

Anuncio

El UART MICROPROCESADORES Sistema de comunicación serial Dato al destino Dato de la fuente 8 bits 1 bit a la vez Buffer de dato transmitido 8 bits Registro de corrimiento entrada paralelo/salida serie 8 bits Buffer de dato recibido 8 bits Registro de corrimiento entrada serie/salida paralelo Reloj del Receptor Reloj del Transmisor Transmisor Receptor Carlos E. Canto Quintal El UART MICROPROCESADORES Ci rrccui ttos nt Ci ui osii ntegr egrados adosadapt adaptador adores esde de ccomuni ccac óón n sser al ásus omuni acii erii almmás usados ados UART (Universal Asynchronous Reciever Transmitter). ACIA ( Asynchronous Communications Interfase Adapter). Z80 SIO (Serial Input/Output) USART (Universal Synchronous Asynchronous Reciever Transmitter) Carlos E. Canto Quintal El UART MICROPROCESADORES FUNCIONES DE UN UART 3 CONVIERTE LOS DATOS DE PARALELO A SERIE YVICEVERSA 3 GENERA YCHECA LA PARIDAD DE LOS DATOS 3 GENERA BIT DE ARRANQUE 3 INSERTA BIT DE PARADA 3 CONTROLA ELNÚMERO DE BITS POR CARÁCTER 3 ALMACENA TEMPORALMENTE ELMENSAJE 3 CONTROLA LA VELOCIDAD DE TRANSMISIÓN-RECEPCIÓN Carlos E. Canto Quintal El UART Bus de datos MICROPROCESADORES PUERTO SERIE RS232C NIVEL TTL NIVEL RS232 UART Paralelo/serie CPU Manejador RS-232 Serie/paralelo Periférico serie de salida Periférico serie de entrada DIAGRAMA DE BLOQUES DE UN PUERTO SERIE RS232C USANDO UN UART Carlos E. Canto Quintal El UART MICROPROCESADORES Protocolo de comunicación asíncrona de bitde arranque/bitde parada Bit de paridad opcional de 7 ú 8 bits de datos Línea ociosa b0 b1 b2 b3 b4 b5 b6 b7 P Bit(s) de parada Bit de arranque Carlos E. Canto Quintal El UART MICROPROCESADORES Bufferdel busde datos Bufferdelreceptor Registro de corrimiento delreceptor D0-D7 Temporización ycontroldel receptor Registro controlde línea Latchdivisor (LS) Latchdivisor(MS) Arquitectura interna delUART 8250 Registro de Statusde línea Retén de transmisor Generador de baudaje habilitadorde interrupciones identificadorde interrupciones Rclk Baudout Temporización ycontroldel transmisor Registro de corrimiento deltransmisor controlde modem Statusde modem Sin Lógica de controldel modem Lógica de controlde interrupciones Sout RTS CTS DTR DSR DCD RI OUT1 OUT2 Intr Carlos E. Canto Quintal El UART MICROPROCESADORES Manual Carlos E. Canto Quintal El UART MICROPROCESADORES 9Orden de lasseñalesde “handshaking”o decontrolen unacomunicación Half duplexvía puerto RS232. Carlos E. Canto Quintal El UART MICROPROCESADORES Registro de Control de Línea (Line Control Register LCR) b7 b6 DLAB DLAB b5 Break Break Control Control 0=off 0=off 1=on 1=on b4 000 001 011 101 111 = = = = = b3 b2 Número Número de destops stops bits bits 0=1 0=1 1=2 1=2 Paridad ninguna impar par marca espacio b1 b0 Número de bits de Datos 10=7 11=8 Divisor DivisorLatches LatchesAccess AccessBit: Bit: Bit de Acceso a los Bit de Acceso a losLatches Latches Divisores Divisores Carlos E. Canto Quintal El UART MICROPROCESADORES Registro de Status de Línea (Line Status Register LSR) b7 b6 b5 b4 Buffer Buffer de Tranmisor Detección Detección de Tranmisor Siempre Siempre Transmisor vacío de de Transmisor vacío 00 Vacío (TXE) Break Break Vacío (TXE) (TBE) (TBE) b3 Error Error de de tramado tramado b2 Error Error de de paridad paridad b1 Error Error de de Overrun Overrun b0 Dato Dato Listo Listo (RxRDY) (RxRDY) Carlos E. Canto Quintal El UART MICROPROCESADORES Registro de Habilitación de Interrupciones (Interrupts Enable Register IER) b7 Siempre Siempre 00 b6 b5 Siempre Siempre 00 b4 Siempre Siempre 00 b3 Siempre Siempre 00 b2 Entrada Entrada RS232 RS232 b1 b0 Error Buffer Buffer Error del del Dato del Dato del Receptor Transmisor Recibido Receptor Transmisor Recibido oo Vacío (RxRDY) Vacío (RxRDY) break (TBE) (TBE) break Carlos E. Canto Quintal El UART MICROPROCESADORES Registro de Identificación de Interrupciones (Interrupts Identificación Register IIR) b7 Siempre Siempre 00 b6 b5 Siempre Siempre 00 Bit 2 b4 Siempre Siempre 00 b3 Siempre Siempre 00 b2 b1 b0 Siempre Siempre 00 Bit 1 Bit 0 Prioridad * Interrupción identificada 0 0 1 Ninguna Ninguna 1 1 0 0 Error de serialización o Break 1 0 0 1 Dato Recibido 0 1 0 2 0 0 0 3 Buffer del Transmisor vacío Entrada RS232 * 0 Es la más alta Carlos E. Canto Quintal El UART MICROPROCESADORES Tabla de Registros y el DLAB A0 Lectura / Escritura Registro DLAB A2 A1 0 0 0 0 __ Receptor(lectura) Transmisor (escritura) 0 0 0 1 R/W Habilitación de interrupciones X 0 1 0 LECTURA Identificación de Interrupción X 0 1 1 R/W X 1 0 0 R/W Registro de Control del Modem X 1 0 1 R/W Registro de Status de Línea X 1 1 0 R/W Registro de Status del Modem X 1 1 1 R/W Scratch Pad 1 0 0 0 R/W Latch Divisor Menos Significativo 1 0 0 1 R/W Latch Divisor Más Significativo de Control de Línea Carlos E. Canto Quintal El UART MICROPROCESADORES Carlos E. Canto Quintal El UART MICROPROCESADORES Configuración de pines del UART National 8250 D7-D0 DISTR DOSTR INTRPT MR A0 A1 A2 SOUT SIN RTS DTR DSR DCD CTS RI XTAL1 ADS “0” 3.072 MHZ DOSTR DISTR CS2 CS1 “1” A conector RS-232 Manejadores EIA RS-232 CS0 XTAL2 BAUDOUT RCLK Carlos E. Canto Quintal El UART MICROPROCESADORES CONFIGURACIONES DE PINES DEL NS16650 Carlos E. Canto Quintal El UART MICROPROCESADORES DISTRIBUCIÓN DE TERMINALES DEL UART16650 Carlos E. Canto Quintal El UART MICROPROCESADORES TERMINALES DEL UART16650 ADS, Address Strobe, Pin 25: The positive edge of an active Address Strobe (ADS) signal latches the Register Select (A0, A1, A2) and Chip Select (CS0, CS1, CS2) signals. Note: An active ADS input is required when the Register Select (A0, A1, A2) and Chip Select (CS0, CS1, CS2) signals are not stable for the duration of a read or write operation. If not required, tie the ADS input permanently low. BAUDOUT, Baud Out, Pin 15: This is the 16 X clock signal from the transmitter section of the UART. The clock rate is equal to the main reference oscillator frequency divided by the specified divisor in the Baud Generator Divisor Latches.The BAUDOUT may also be used for the receiver section by tying this output to the RCLK input of the chip. CS0, CS1, CS2, Chip Select, Pins 12±14: When CS0 and CS1 are high and CS2 is low, the chip is selected. This enables communication between the UART and the CPU. The positive edge of an active Address Strobe signal latches the decoded chip select signals, completing chip selection. If ADS is always low, valid chip selects should stabilize according to the tCSW parameter. Carlos E. Canto Quintal El UART MICROPROCESADORES TERMINALES DEL UART16650 DDIS, Driver Disable, Pin 23: This goes low whenever the CPU is reading data from the UART. It can disable or control the direction of a data bus transceiver between the CPU and the UART. MR, Master Reset, Pin 35: When this input is high, it clears all the registers (except the Receiver Buffer, Transmitter Holding, and Divisor Latches), and the control logic of the UART. The states of various output signals (SOUT, INTR, OUT 1, OUT 2, RTS, DTR) are affected by an active MR input (Refer to Table I.) This input is buffered with a TTLcompatible Schmitt Trigger with 0.5V typical hysteresis. RCLK, Receiver Clock, Pin 9: This input is the 16 c baud rate clock for the receiver section of the chip. Carlos E. Canto Quintal El UART MICROPROCESADORES FIFO CONTROL REGISTER This is a write only register at the same location as the IIR (the IIR is a read only register). This register is used to enable the FIFOs, clear the FIFOs, set the RCVR FIFO trigger level, and select the type of DMA signalling. Bit 0: Writing a 1 to FCR0 enables both the XMIT and RCVR FIFOs. Resetting FCR0 will clear all bytes in both FIFOs. Carlos E. Canto Quintal El UART MICROPROCESADORES CONEXIÓN DEL UART USANDO INTERRUPCIONES Bus Bus de de Datos Datos CPU CPU INTR Bus Bus de de Direcciones Direcciones UART UART Driver Driver RS232 RS232 MODEM MODEM LÍNEA LÍNEA TELEFÒNICA TELEFÒNICA LÍNEAS DE CONTROL Y DE STATUS (HANSDSHAKING) Carlos E. Canto Quintal El UART MICROPROCESADORES Carlos E. Canto Quintal El UART MICROPROCESADORES PRACTICA NUM. 10 IMPLEMENTACIÓN DE UN PUERTO SERIE USANDO EL UART NS8250 +5v 40 2 INT 7414 12 13 30 1 21 18 22 19 25 35 IORD IOWR RESET BUS DE DATOS BUS DE DIRECCIONES A0 A1 A2 OUT1 OUT2 RD WR RD WR ADS RESET 1 2 3 4 5 6 7 8 D0-D7 VCC CS0 CS1 INT RXD DCD DSR CTS RI D0 D1 D2 D3 D4 D5 D6 D7 28 27 26 TXD RTS DTR SALIDA SERIE TTL 11 32 33 RS232 (MAX232) 10 38 37 36 39 ENTRADA SERIE RS232 ENTRADA SERIE TTL DDIS NC CSOUT +5v 23 29 24 220 XTAL1/CLK 1M 17 A2 1 A3 2 A4 3 A B C A5 6 A6 4 A7 5 G1 G2A G2B Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 AL 8255 AL 15 8254 AL 14 ADC0804 13 12 11 10 9 7 fxtal=1.8432 3.072 Mhz RCLK 1 15 9 74LS08 ó XIN 90H-97H 3 XOUT 74LS138 2 7414 SIN USO 1 2 GND BAUDOUT CS2 40-60pf XTAL2 20 Indicador de que el UART se ha seleccionado 14 10-30pf 1.5k SALIDA SERIE RS232 MANEJADORES 8250 A0 A1 A2 16 34 31 A7 A6 A5 A4 A3 A2 A1 A0 1 0 0 1 0 X X X 16 2 1 17 3 4 7414 REOJ EXTERNO SALIDA OPCIONAL DEL RELOJ USANDO UN OSCILADOR EXTERNO, QUE PODRIA SER EL OSCILADOR USADO PARA E LCPU AL UART DIRECCIONES DE SELECCIÓN DEL UART 90H AL 97H Carlos Canto Carlos E. Canto Quintal El UART MICROPROCESADORES Programa para transmitir datos por el puerto Serial con un UART sin usar interrupciones Inicio Inicio Definir Definir formato formato del del dato dato Selección Selección velocidad velocidad de de transmisión transmisión Leer Leer dato dato de de memoria memoria NUM_DAT EQU ALMACEN EQU PAL_CTRL EQU LCR EQU LATCH_DIVL EQU LATCH_DIVM EQU BUFF_TX EQU LSR EQU N_LSB EQU N_MSB EQU Transmitir Transmitir dato dato ¿Terminó ¿Terminó transmisión transmisión ?? No Si No ¿Es ¿Es último último dato dato ?? Si 10H 800H 87H 93H 90H 91H 90H 95H 14H 00H LD B, NUM_DAT LD HL,ALMACEN-1 LD A,PAL_CTRL OUT (LCR),A LD A, N_LSB OUT (LATCH_DIVL),A LD A,N_MSB OUT (LATCH_DIVM),A IN A,(LCR) AND 7FH OUT (LCR),A OTRO: INC L LD A,(HL) OUT (BUFF_TX),A DE_NUEVO: IN A,(LSR) AND 60H CP 60H JP NZ,DE_NUEVO DJNZ,OTRO END End End Carlos E. Canto Quintal El UART MICROPROCESADORES GEN DE BAUDAJE Carlos E. Canto Quintal