Organización procesador MIPS

Anuncio

Organización

procesador MIPS

Procesador MIPS

Organización MIPS

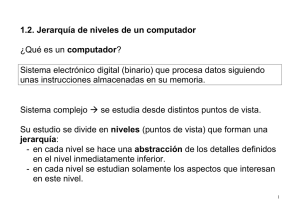

Memoria

CPU

Alu

Registros

FPU

Registros

Mul Div

Hi

Lo

U. Aritmética

Traps Manejo de Memoria

Procesador MIPS

Organización MIPS

Unidad

Aritmética y Lógica (ALU).

Unidad Aritmética entera, operaciones de

multiplicación y división.

Unidad punto flotante (FPU).

Coprocesador

dedicado al manejo de

memoria caché y virtual.

Procesador MIPS

Memoria

Se

denomina palabra (word) al contenido de

una celda de memoria.

MIPS posee palabras de 32 bits. Las

direcciones de memoria correspondes a

datos de 8 bits (byte). 4 bytes en una palabra.

Para acceder a una palabra se leen 4 bytes.

Procesador MIPS

Memoria

Dos

formas de numerar los bytes contenidos

en una palabra:

Big endian (IBM, Motorola, MIPS)

Byte 0

Byte 1

Byte 2

Byte 3

La dirección del byte más significativo termina en

00 (en binario), sólo si la palabra está alineada

Direcciones

Aumentan

Hacia abajo

Byte 3

Byte 2

Byte 1

Byte 0

Dirección de palabra

Dirección de palabra

Procesador MIPS

Memoria

Dos

formas de numerar los bytes contenidos

en una palabra:

Little endian (Intel, Dec)

Byte 3

Byte 2

Byte 1

Byte 0

La dirección del byte menos significativo termina

en 00 (en binario), sólo si la palabra está alineada

Direcciones

Aumentan

Hacia abajo

Byte 0

Byte 1

Byte 2

Byte 3

Dirección de palabra

Dirección de palabra

siguiente

Procesador MIPS

Memoria

El

ancho de la dirección define el espacio de

direccionamiento.

Las instrucciones ocupan una palabra

alineada. Implica que las direcciones de

instrucciones son múltiplos de 4.

El alineamiento requiere que un objeto

comience a ser almacenado en una dirección

que sea un múltiplo de su tamaño.

Procesador MIPS

Nombres de los Tipos de Datos

Bit:

0,1

Bit String

4 bits

8 bits

16 bits

32 bits

64 bits

nibble

byte

half-word

word

double-word

Procesador MIPS

Nombres de los Tipos de Datos

Character

ASCII Código de 7 bits por símbolo.

Decimal(BCD)

Dígitos de 0-9 codificados desde 0000 hasta 1001

Enteros

Sin signo y con signo en complemento dos.

Las representaciones de números binarios con signo se

tratarán más adelante.

Reales

Precisión Simple. Precisión Doble.

Las representaciones de números reales en binario se

tratarán más adelante.

Procesador MIPS

Características

Puede

mover bytes, medias palabras y

palabras, desde registro hacia la memoria y

viceversa.

Puede procesar números enteros binarios de

32 bits, con y sin signo .

Capacidad de procesar números binarios

reales o de punto flotante en simple y doble

precisión.

El procesador MIPS no tiene operaciones al

bit.

Procesador MIPS

Registros

Posee 32 registros de 32 bits cada uno.

Se requieren 5 bits para especificar un

registro.

Poseen nombres simbólicos y números.

Su uso además se rige bajo algunos

convenios.

Procesador MIPS

Registros

Nombre Registro

Número

Uso

zero

0

Constante 0

at

1

Reservado para el assembler

v0

2

v1

3

Para evaluación de expresiones y

retorno de resultados de una función

a0

4

Argumento 1

a1

5

Argumento 2

a2

6

Argumento 3

a3

7

Argumento 4

t0

8

Temporal (no se preserva a través de los llamados)

t1

9

Temporal (no se preserva a través de los llamados)

t2

10

Temporal (no se preserva a través de los llamados)

t3

11

Temporal (no se preserva a través de los llamados)

t4

12

Temporal (no se preserva a través de los llamados)

t5

13

Temporal (no se preserva a través de los llamados)

t6

14

Temporal (no se preserva a través de los llamados)

t7

15

Temporal (no se preserva a través de los llamados)

Procesador MIPS

Registros

Nombre Registro

Número

Uso

s0

16

Temporal que debe preservarse entre llamados a funciones

s1

17

Temporal que debe preservarse entre llamados a funciones

s2

18

Temporal que debe preservarse entre llamados a funciones

s3

19

Temporal que debe preservarse entre llamados a funciones

s4

20

Temporal que debe preservarse entre llamados a funciones

s5

21

Temporal que debe preservarse entre llamados a funciones

s6

22

Temporal que debe preservarse entre llamados a funciones

s7

23

Temporal que debe preservarse entre llamados a funciones

t8

24

Temporal (no se preserva a través de los llamados)

t9

25

Temporal (no se preserva a través de los llamados)

k0

26

Reservado para el núcleo del Sist. Operativo

k1

27

Reservado para el núcleo del Sist. Operativo

gp

28

Puntero al área global de datos

sp

29

Puntero al tope de la pila. Stack pointer

fp

30

Puntero a zona de variables en la pila. Frame pointer

ra

31

Dirección de retorno (usado en invocaciones a funciones)

Procesador MIPS

Ciclo de Ejecución

Corresponde

a una secuencia repetitiva de los

siguientes pasos:

Búsqueda de instrucción:

Obtiene desde la memoria la instrucción que será ejecutada.

Decodificación de Instrucción:

Determina el tipo de instrucción y su largo en caso de que la

instrucción esté compuesta de varias palabras.

Debe especificarse cómo estarán codificados los operandos, la

operación y la dirección de la próxima instrucción.

Procesador MIPS

Ciclo de Ejecución

Búsqueda de Operandos:

Localiza y obtiene los datos que son los operandos de la

instrucción.

Accesar registros o la memoria, o decodificar valores que vienen

contenidos en la misma instrucción (operandos inmediatos), lo

cual debe especificarse en la instrucción.

Ejecución:

Realiza la operación con los operandos de entrada para generar

un resultado y determina el estado de éste.

Procesador MIPS

Ciclo de Ejecución

Almacenamiento de resultados:

Deposita los resultados en la memoria de datos o en registros.

Esto se especifica en el código de la instrucción.

Determinación de próxima instrucción:

Determina cual será la próxima instrucción a ejecutarse.

Incluye mecanismos para saltos incondicionales, bifurcaciones o

llamado a subrutinas.

Procesador MIPS

Formato de Instrucciones MIPS

MIPS

posee tres formatos de instrucciones

denominados R, I y J

Procesador MIPS

Formato de Instrucciones MIPS

Formato

Op 6

R para operaciones.

Rs 5

Rt 5

Rd 5

Shamnt 5

Funct 6

Tres registros, dos para especificar las fuentes de datos y el

lugar para almacenar el resultado.

Instrucciones de corrimiento utilizan el campo Shamnt (Shift

Amount), especifica el número de posiciones de bits que se

desplazará uno de los operandos.

Un campo para expandir el código de operación.

Procesador MIPS

Formato de Instrucciones MIPS

Formato

I para

bifurcaciones.

Op 6

Rs 5

Rt 5

inmediatas,

transferencias

y

Inmediato 16

Se emplean 16 bits, para programar un valor constante.

Basta un registro de operando y otro para depositar el

resultado.

Las operaciones lógicas se extienden los 16 bits a 32 con

ceros en la parte más significativa.

Las operaciones aritméticas se extienden con signo.

Procesador MIPS

Formato de Instrucciones MIPS

Formato

I para

bifurcaciones.

Op 6

Rs 5

Rt 5

inmediatas,

transferencias

y

Inmediato 16

En transferencias el registro especificado en rs se emplea

como registro base y el valor inmediato se interpreta como

desplazamiento con signo, rt especifica el registro donde se

leerá o será escrito desde o hacia la memoria

Procesador MIPS

Formato de Instrucciones MIPS

Formato

Op 6

J para saltos

Dirección 26

Posee un campo de 26 bits que se emplea para generar la

dirección efectiva de salto

Procesador MIPS

Repertorio MIPS (tipo carga-almacenamiento)

Aritméticas y Lógicas.

Formato R. (10 instrucciones). Todas de tres operandos.

Add, AddU, Sub, SubU, And, Or, Xor, Nor, SLT, SLTU

Instrucción

Ejemplo

Significado

add

add

$t1,$t2,$t3

$t1 = $t2 + $t3

add unsigned

addu

$t1,$t2,$t3

$t1 = $t2 + $t3

subtract

sub

$t1,$t2,$t3

$t1 = $t2 – $t3

subtract unsigned subu

$t1,$t2,$t3

$t1 = $t2 – $t3

and

and

$t1,$t2,$t3

$t1 = $t2 & $t3

or

or

$t1,$t2,$t3

$t1 = $t2 | $t3

xor

xor

$t1,$t2,$t3

$t1 = $t2 ^ $t3

nor

nor

$t1,$t2,$t3

$t1 = ~($t2 | $t3)

set on less than slt

$t1,$t2,$t3

if ($t2 < $t3) $t1=1; else $t1=0;

Procesador MIPS

Repertorio MIPS (tipo carga-almacenamiento)

Corrimientos

Aritméticos y Lógicos.

SLL, SRL, SRA, SLLV, SRLV, SRAV (6 instrucciones)

La palabra shift significa corrimiento. Left significa izquierdo. Right significa

derecha.

Instrucción

Ejemplo

Significado

shift left logical

sll

$t1,$t2,10

$t1 = $t2 << 10

shift right logical

srl

$t1,$t2,10

$t1 = $t2 >> 10

shift right arithm.

sra

$t1,$t2,10

$t1 = $t2 >> 10

shift left logical var.

sllv

$t1,$t2,$t3

$t1 = $t2 << $t3

shift right logical var

srlv

$t1,$t2,$t3

$t1 = $t2 >> $t3

Procesador MIPS

Repertorio MIPS (tipo carga-almacenamiento

Formato

I Aritméticas y Lógicas. Inmediatas.

AddI, AddIU, AndI, OrI, XorI, SLTI, SLTIU, LUI (8 instrucciones)

Instrucción

Ejemplo

Significado

add immediate

addi $t1,$t2,100

$t1 = $t2 + 100

add imm. unsigned

addiu $t1,$t2,100 $t1 = $t2 + 100

and immediate

andi $t1,$t2,10

$t1 = $t2 & 10

or immediate

ori $t1,$t2,10

$t1 = $t2 | 10

xor immediate

xori $t1,$t2,10

$t1 = $t2 ^10

set less than imm

slti $t1,$t2,100

if ($t2 < 100) $t1=1;

else $t1=0;

Procesador MIPS

Repertorio MIPS (tipo carga-almacenamiento)

Formato

I Accesos a Memoria.

LB, LBU, LH, LHU, LW, LWL, LWR

(7 instrucciones)

SB, SH, SW, SWL, SWR

(5 instrucciones)

Instrucción

Ejemplo

Significado

Load byte

lb

$t1, 40($t2)

$t1 = M[ ($t2) + 40]

Load byte unsigned

lbu

$t1, 40($t2)

$t1 = M[ ($t2) + 40]

Load halfword

lh

$t1, 40($t2)

$t1 = M[ ($t2) + 40]

Load halfword unsig.

lhu

$t1, 40($t2)

$t1 = M[ ($t2) + 40]

Load word

lw

$t1, 40($t2)

$t1 = M[ ($t2) + 40]

Store byte

sb

$t1, 41($t2)

M[ ($t2)+ 41] = $t1

Store half

sh

$t1, 42($t2)

M[ ($t2)+ 42] = $t1

Store word

sw

$t1,100($t2)

M[ ($t2)+ 100] = $t1

Procesador MIPS

Repertorio MIPS (tipo carga-almacenamiento)

Multiplicación

y división entera

Instrucción

Ejemplo

multiply

mult $t2,$t3

multiply unsigned multu $t2,$t3

divide

div $t2,$t3

divide unsigned

divu

$t2,$t3

Significado

Hi, Lo = $t2 * $t3

Hi, Lo = $t2 * $t3

Lo = $t2 ÷ $t3

Lo = cuociente

Hi = $2 mod $3 Hi = resto

Lo = $t2 ÷ $t3

Hi = $t2 mod $t3 resto

Procesador MIPS

Repertorio MIPS (tipo carga-almacenamiento)

Move

result from.

Mueve el resultado de la multiplicación o división a un registro del

procesador. MFHI, MFLO

Instrucción

Ejemplo

Significado

Move from Hi

mfhi $t1

$t1 = Hi

Move from Lo

mflo $t1

$t1 = Lo

Procesador MIPS

Repertorio MIPS (tipo carga-almacenamiento)

Move

to HI or LO .

MTHI, MTLO rd

Instrucción

Move to Hi

Move to Lo

Ejemplo

mthi $t1

mtlo $t1

Significado

Hi = $t1

Lo = $t1

Procesador MIPS

Repertorio MIPS (tipo carga-almacenamiento)

Formato

I Comparación y bifurcaciones

Instrucción

Ejemplo

branch on equal beq $t1,$t2,100

branch on not eq. bne $t1,$t2,100

Significado

if ($t1 == $t2)

PC = (PC+4)+100*4;

if ($t1!= $t2)

PC = (PC+4)+100*4;

Comparación con cero

bgtz rs, offset if R[rs] > 0 then PC =( PC+4) + offset*4;

bltz rs,offset if R[rs] < 0 then PC =( PC+4) + offset*4;

bgez rs,offset if R[rs] >= 0 then PC =( PC+4) + offset*4;

bltzal rs, offset if R[rs] < 0 then {ra = (PC+4); PC =(PC+4) + offset*4;}

bgezal rs,offset if R[rs] >= 0 then {ra = (PC+4); PC =(PC+4) + offset*4;}

Procesador MIPS

Repertorio MIPS (tipo carga-almacenamiento)

Formato

J Saltos incondicionales

J, JR, JAL

Instrucción

Jump

jump and link

(Formato R)

jump register

jump and link

Ejemplo

j rótulo

jal rótulo

Significado

salto rótulo.

$ra = (PC + 4); salto rótulo;

jr $t1

jr $ra

jalr $t1

PC = $t1;

PC = $ra

$ra = (PC + 4); PC = $t1;

Procesador MIPS

Repertorio MIPS (tipo carga-almacenamiento)

Control

de coprocesadores

10 instrucciones, en formato R).

ejemplo: syscall, break, nop, etc..

Procesador MIPS

Modos de direccionamiento MIPS.

Registro

(directo):

El valor efectivo del operando es el contenido en el registro.

Inmediato:

El valor del operando es el campo inmediato de 16 bits.

Si el operando es un valor lógico, se extiende a 32 agregando

ceros.

Si el operando es aritmético se extiende con signo a 32 bits.

Base+índice:

Se usa en load, store.

El contenido de rs + inmediato (extendido en forma aritmética) es la

dirección efectiva.

El campo inmediato se interpreta como el número de bytes relativo

al registro base.

Procesador MIPS

Modos de direccionamiento MIPS.

Relativo

En bifurcaciones

a PC:

Al valor de PC se le suma el valor inmediato extendido en

forma aritmética.

El valor inmediato es el número de instrucciones que salta.

En saltos ( j, jal,jr):

El valor inmediato (que en este caso es de 26 bits)

Se multiplica por cuatro (de esta forma quedan 28 bits)

Los primeros 4 bit se toman del valor de PC de la instrucción

siguiente (formando así los 32 de la dirección).

Procesador MIPS

Niveles de Representación

Lenguaje

de alto nivel, ejemplo C.

a[x] = a[x+1];

x++;

Assembler

Simbólico.

add $t1, $t2, $t3

lw $t5, 4($t1)

Lenguaje

de Máquina. Binario.

1010 1110 0100 1001 0000 0000 0000 0000

Procesador MIPS

Niveles de Representación

Transferencias

Transferencias Lógicas

Ej. R[8] = MEM[ R[18] + sign_ext(0)]; PC = PC + 4;

Transferencias Físicas.

Ej.

IR = MemInst[PC], PC=PC+4; Unidad Instrucción.

A = R[18];

Unidad Registros. Lectura.

S = A + signext(4);

Unidad Operaciones.

M = MemDat[S];

Unidad Memoria Datos.

R[9] = M

Unidad Registros. Escritura.

Procesador MIPS

Niveles de Representación

Control

Puede describirse las secuencias de las señales

de control que activan las transferencias físicas.

nPC_sel = “+4”, WEPC , WEIR ;

Unidad Instrucción.

WEA ;

Unidad Registros. Lectura.

AluSrc = "Op32", ExtOp = “sign”, AluCtr = “add”, WES ; Unidad Operaciones.

MemRd, WEM ;

Unidad Memoria Datos.

RegDst = "rt", Memtoreg = "mem", RegWr. Unidad Registros. Escritura.

Procesador MIPS

Los enteros se representan en una palabra de la

memoria, y sus valores dependen del ancho de

palabra que tenga la memoria (en MIPS son de

32 bits).

El

procesador

emplea

representación

complemento a dos para representar números

con signo.

El complemento a dos es el complemento a uno

más uno (sumarle uno en binario).

Para obtener un número en complemento a uno,

basta cambiar sus unos por ceros y sus ceros

por unos.

Procesador MIPS

Por ejemplo para una palabra de tres

cifras (3 bits).

El negativo de un número se obtiene

complementándolo, excepto para el mayor

negativo que no tiene complemento en

tres cifras.

De esta manera para restar, basta sumar

el complemento.

Procesador MIPS

El complemento a uno de una palabra de tres

bits:

Si Comp ==1 se tiene que B es complemento uno

de A; en caso contrario: B = A.

Procesador MIPS

Realizar sumas o restas en complemento

dos. Mediante un sumador binario, basta

incorporar un uno a la reserva de entrada

y pasar el sustraendo en complemento a

uno, para realizar restas.

Procesador MIPS

Sumador completo de un bit, tiene tres

entradas y dos salidas, con la siguiente

tabla de verdad: