Circuito Integrado Programable para la Conversión Serie Paralelo

Anuncio

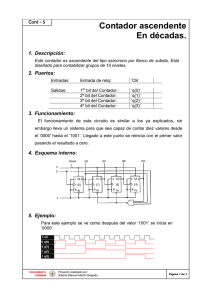

Revista Argentina de Trabajos Estudiantiles 1 Circuito Integrado Programable para la Conversión Serie Paralelo De 32bits Martín Di Federico† Pedro Julián ‡ † Universidad Nacional del Sur mdife@uns.edu.ar ‡ Universidad Nacional Del Sur - CONICET pjulian@ieee.org Resumen— Este trabajo es la descripción de un circuito integrado conversor serie-paralelo de 32 bits, implementado en una tecnología CMOS estándar de 1.5µm. Abstract—This work is the description of an integrated circuit serial-parallel converter of 32 bits, implemented in a CMOS standard technology of 1.5µm I. INTRODUCCIÓN En este trabajo se presenta un circuito integrado diseñado en la UNS (Universidad Nacional Del Sur), para la Materia Análisis y Diseño de Circuitos Digitales. Una de las limitaciones comunes en circuitos integrados (CI) es la cantidad de pads disponibles para monitorear señales internas, y también para acceder al interior del mismo con un bus de señales externas [1] [2]. Una posible solución consiste en el diseño de una interfaz programable serie, que permita leer o escribir una cadena de registros, que funcionen extrayendo datos del CI o introduciéndolos. El circuito integrado que se propone en este trabajo, es una memoria de 32 bits serie, donde por medio de un pin de Entrada / Salida (E/S) se realiza la lectura y escritura de la información. En un ciclo de lectura o escritura, se puede acceder tanto a un bit como a los 32 bits en una sola trama de comunicación. Este tipo de arquitectura también puede ser utilizada para establecer comunicaciónes de datos dentro del mismo chip a altas velocidades y para intercambiar datos entres distinto niveles de un chip, en tecnologías de integración 3D [3]. II. TECNOLOGÍA El CI se integró en un proceso n-well CMOS estándar de 1.5µm (λ=0.8 µm), con 2 capas de metal, 2 capas de poly, opción a transistores NPN y condensadores Pip (poly sobre poly) de 600 af/µm². Todos los transistores implementados son de tamaño mínimo, siendo los PMOS de 8 µm x 1,6µm (W=10 λ, L= 2 λ) y los NMOS de 4,8 µm x1,6 µm (W =6 λ, L=2 λ). El circuito integrado (CI) es una memoria serie de 32 bits, donde se realiza la lectura y escritura de la información por medio de un único pin de Entrada / Salida (E/S). En un ciclo de lectura o escritura, se puede acceder tanto a un bit como a los 32 bits, mediante una sola trama de comunicación. La salida paralelo está multiplexada en 2 canales de 16 bits. Con la entrada Mux en estado bajo se tienen en la salida los bits de la dirección 00H a la 0FH, con Mux en estado alto se tienen los bits de la 10H a la 1FH. Se define un protocolo serie sincrónico, el cual permite establecer las operaciones de lectura o escritura, tanto para un bit como para los 32 bits (Palabra). La trama del protocolo puede verse en la Fig. 1. 1 Bit L/E 1 Bit B/P 5 Bits / 32 Bits Dir/Pal 1 Bit B Figura 1: Trama de comunicación serie La función de cada uno de los segmentos de la trama se explica a continuación: L / E: Primer bit de la trama, indica si la operación que se va a realizar es de lectura (0 lógico) o de escritura (1 lógico). B / P: Indica si la operación de lectura o escritura se realiza en solo bit (1 lógico) o una palabra (0 Lógico). Dir / Pal: La longitud de este segmento de trama depende si se escribe una palabra o un bit. Si se opera sobre una palabra, este segmento tiene una longitud de 32 bits y es la palabra que se escribe o se lee de la memoria, donde el primer bit corresponde a la dirección 00h y el último a la 1Fh. Para operaciones sobre un bit este segmento tiene una longitud de 5 bits, los cuales indican la dirección del bit que se va a acceder. B: Este segmento solo existe para operaciones con bit, siendo este el valor que se escribe o se lee de la memoria. Para comenzar el envío de la información, junto con el bit L/E es necesario establecer un nivel bajo en la entrada En para indicar comienzo de la trama, como lo muestra la Fig. 2. En la Figura 2 se puede observar un ejemplo de la lectura de un bit, y en la Fig. 3 la lectura de una palabra. III. DESCRIPCIÓN TRATE06-004 Vol. I - Nº 2 - Marzo 2006 18 Revista Argentina de Trabajos Estudiantiles L=2*L W=10*L 2 Out0 W=6*L A3 B A4 C L=2*L A W=10*L L=2*L A2 Out1 W=6*L W=10*L Habilitación L=2*L L=2*L Out2 W=6*L W=10*L L=2*L L=2*L Out3 W=6*L L=2*L B A B A B A B A Salidas decodificador Entradas deco 2x4 A1 Figura 2: Lectura de Bit A0 Figura 4: Decodificador de bloque Como muestra la Figura 5, cada registro de memoria tiene una entrada de habilitación (Sel), que es manejada por el decodificador. Tiene una entrada de dato (In), una entrada de Lectura (R), que habilita la salida de información, una entrada de escritura (W), que guarda el Bit de la entrada In en el registro. Para borrar la información tiene reset (Clr), y dos fases del reloj (F1 y F2). La salida Dout esta conectada al multiplexor de salida paralelo y la salida Out está conectada a través de un buffer de tres estados al bus de salida serie. Figura 3: Lectura de palabra IV. ARQUITECTURA A La memoria de 32 bits está formada por 32 registros, los cuales están agrupados en 8 bloques de 4 registros. Cada bloque cuenta con un decodificador de 2x4, que habilita a cada uno de los registros en el bloque. A su vez, cada decodificador tiene una habilitación de 3 entradas; cada uno de los 8 grupos de registros se habilita con estos 3 bits, obteniéndose así el decodificador de 5x32. En la Figura 4 puede verse el esquemático del decodificador de bloque. A Sel B R B W Clr El circuito funciona con un reloj de dos fases no solapadas. El CI contiene a nivel de bloques, una memoria de 32 Bits y un decodificador de 5 líneas de entrada a 32 líneas de salida (5x32) para la habilitación de cada registro de memoria. También cuenta con un contador que regula los tiempos y genera las direcciones de memoria, un registro serie que guarda la dirección del bit que se va a acceder y dos multiplexores: uno para los datos la salida paralelo y otro para seleccionar si la habilitación de los registros lo realiza el contador o el registro serie. Además posee una máquina de estados que se encarga de sincronizar los tiempos y las señales internas de control y comunicación. In CLB DATA Q 0 1 Enn Out QB F1 F2 F1 S F2 DOut Figura 5: Esquemático de un registro de memoria Cada uno de los registros esta formado por un Flip-Flop D Maestro Esclavo con reloj bifásico, donde el maestro lee el dato de la entrada con un “1” en la fase uno (1) y mantiene el dato leído a la salida con un “0” en la fase 1, y el esclavo copia y mantiene de igual forma, pero con la fase dos (2). En la Figura 6, se puede observar una de las celdas de memoria que esta formada por 56 transistores de tamaño mínimo con un área de 0,024mm², teniendo 304µm de ancho y 80µm de alto. Figura 6: Layout de un registro de memoria Para comenzar el envío de información se tiene que habilitar la máquina de estados por medio de la entrada de habilitación (En). La maquina de estados tiene 7 estados TRATE06-004 Vol. I - Nº 2 - Marzo 2006 19 Revista Argentina de Trabajos Estudiantiles codificados mediante tres bits X0, X1 y X3. Al resetear la máquina, esta se establece en el estado inicial (I) y en función del bit de E/S evoluciona a los siguientes estados: E: Se realizara una operación de escritura L: Se realizara una operación de lectura LP: Lectura de Palabra LB: Lectura de Bit EP: Escritura de Palabra EB: Escritura de Bit En la Tabla1 se presentan la transiciones posibles de la máquina de estados. Tabla 1: Tabla de transiciones de estado Estado I E L EB EP LB LP X2 X1 X0 0 0 0 0 0 1 0 1 0 1 0 1 1 0 0 1 1 1 1 1 0 Transiciones Entrada 0 Entrada 1 X2 X1 X0 X2 X1 X0 L 0 1 0 E 0 0 1 EP 1 0 0 EB 1 0 1 LP 1 1 0 LB 1 1 1 EB 1 0 1 EB 1 0 1 EP 1 0 0 EP 1 0 0 LB 1 1 1 LB 1 1 1 LP 1 1 0 LP 1 1 0 3 registro serie, y en el sexto bit se habilita el lugar de memoria apuntado por el registro serie. El registro serie esta formado por 5 Flip-Flop D Maestro Esclavo en cascada, cuya entrada está conectada al pin E/S. El registro serie, se habilita solo en los estados LB y EB. Al escribir o leer los 32 bits las direcciones se generan solas por medio de un contador. Las salidas del registro serie y del contador, van a un multiplexor, y en función del estado en que se encuentre la maquina de estados, selecciona una u otra entrada para ingresar la dirección al decodificador. El contador es de 5 bits y tiene una estructura modular. La Figura 8 muestra el esquemático de cada uno de los cinco módulos del contador donde la salida Out es la entrada del modulo siguiente. La figura 9 muestra el layout de un modulo del contador. El contador completo esta formado por cinco de estos módulos. In A Out B B A Como se puede observar en la figura 7, el layout completo de la máquina de estados mide aproximadamente 0,09mm²; con un alto de 320µm, y un largo de 280µm. Clr CLB DATA Q Cont QB F1 F2 F1 S F2 Figura 8: Modulo del contador Esquemático. Figura 9: Modulo del contador Layout. En los estados LP y EP se está 32 periodos de reloj, para volver al estado inicial en el período 33. En los estados LB y EB solo se está 6 periodos de reloj; en el séptimo periodo, se vuelve al estado inicial. Además, se generan dos señales internas para manejar los tiempos que se transcurre en cada estado. Una señal se genera cuando el contador es 6 y otra cuando el contador es 32, y estas señales se utilizan para volver al estado de Inicio. Figura 7: Layout de la máquina de estados. El direccionamiento de los registros se realiza en formas distintas dependiendo si se esta operando sobre un bit, o sobre los 32 bits. Al escribir o leer un bit, se especifica la dirección en la trama que tiene una longitud de 5 bits, estos se guardan en un TRATE06-004 V. DESCRIPCIÓN DE ENTRADAS/SALIDAS Y PROTOTIPO FABRICADO El CI viene en un encapsulado DIP 40, del cual se utilizan 38 de las patas. Para conectar cada una de las patas del encapsulado con el CI se utilizan los pads. Hay varios tipos de pads, como se puede ver en la Fig. 10. Para alimentar los Vol. I - Nº 2 - Marzo 2006 20 Revista Argentina de Trabajos Estudiantiles 4 inversores y los buffers de estos pads, se utiliza una entrada especial VDD_Pad, de manera que hay dos entradas de alimentación, una para el circuito y otra para los pads. La Figura 11 muestra un diagrama del funcionamiento del Circuito integrado y las interacciones entre las distintas partes del circuito. 5 x 3 2 Buf PADOUT PADOUT PADAREF PADBIDIRHE PADAREF LP Contador 0 32Bits Contar L 1 InAux 0 Hab Out 32 L B Inici o Registro serie Contar F 6 EP 1 IN Contar 0 E Resetear Contador Figura 10: Pads de Salidas y Entradas 1 E B A continuación se detalla cada una de las entradas y salidas del CI, y la función que cumplen. Entradas del circuito: Mux: Selecciona los primero 16 bit o los segundos 16 bits de la salida paralelo. En: Indicador de comienzo de trama. Clr: Reset de los Flip-Flop F1,F2: Entrada de las fases del Reloj.. InAux: Entrada auxiliar de datos CI. Buf: Habilitación externa del buffer de salida del pad E/S. Salidas del circuito: D0..D15: Salida de 16 bits de la memoria. Ep: La máquina de estados se encuentra en el estado EP, escribir palabra. Lp: La máquina de estados se encuentra en el estado LP, leer palabra. Eb: La máquina de estados se encuentra en el estado EB, escribir bit. Lb: La máquina de estados se encuentra en el estado LB, leer bit. CINCO: Señal que indica que el contador llego a cinco. FLAG: Esta señal indica que se terminó de ejecutar la tarea en la memoria y en el próximo ciclo de reloj la máquina de estados retorna a el estado inicial. X0, X1, X2: Las variables de estado, que indican en que estado se encuentra la máquina. Out: Salida Auxiliar Hab: Señal generada internamente que habilita el pad E/S como salida. Figura 11: Grafo del circuito integrado. En la tabla 2 se puede ver un resumen de las áreas de cada uno de los componentes del CI, y también la cantidad de transistores utilizados. Tabla 2: Cantidad de transistores y área de los componentes del circuito. W λ µm 4 40 32 275 325 260 190 1130 904 Trans Buffer Contador Registro Serie Multiplexor Salida Maquina Estados Celda Memoria Bloque memoria Completo 96 1050 H λ 75 480 90 Área µm mm² 60 0,0019 384 0,0998 72 0,0651 840 75 60 0,0504 182 350 280 370 296 0,0829 56 380 304 100 80 0,0243 2346 2500 2000 1050 840 1,6800 3223 3200 2560 1250 1000 2,5600 En la fotografía del integrado que se muestra en la Fig. 12 se pueden ver todas las partes del circuito: El registro serie (1), el contador (2), la máquina de estados (3), los 32 bits de memoria (4) El multiplexor de salida (5), y los buffer del Clr y del Reloj (6). Para utilizar el pin de E/S como salida, hay que habilitar el buffer de salida. La señal que activa dicho buffer se encuentra en la salida Hab, como se puede observar en la Fig 10, y la habilitación del buffer en la Entrada Buf. En funcionamiento normal, los pines Hab y Buf están interconectadas. Para el caso de que falle la habilitación del Pad de E/S, se cuenta con una salida y una entrada auxiliar. TRATE06-004 Contar Vol. I - Nº 2 - Marzo 2006 Figura 12: Fotografía del integrado 21 Revista Argentina de Trabajos Estudiantiles 5 El CI ocupa un tamaño total de 4.4mm x 2.2m. La Figura 13 es una fotografía completa del CI incluyendo las conexiones de los Pads al encapsulado. En la Tabla 3 se muestra un resumen de las áreas en general que ocuparon las distintas partes en la implementación del CI. Una parte importante del Circuito son las conexiones tanto de las señales como del los datos. En la tabla 3 se puede ver que casi un 7% del espacio del CI es para realizar las conexiones entre sus componentes. Tabla 3: Especificaciones de áreas utilizadas Total PADS Para utilizar Chip Conexiones Vacío Área % mm² 9,68 100 5,23 53,98 4,45 46,02 2,56 26,45 0,67 6,88 1,22 12,60 VI. CONCLUSIONES En este trabajo se describió un conversor serie paralelo integrado en tecnología CMOS estándar de 1,5µm, en un área de 4.4mm x 2.2mm. Este proyecto se desarrolló como parte del curso de pregrado Análisis y Diseño de Circuitos Digitales de la carrera de Ingeniería Eléctrica de la UNS, en el marco de un programa de desarrollo y formación de recursos humanos en Diseño de Circuitos Integrados. Una de las aplicaciones directas de este CI es el testeo de futuros desarrollos en el que sea necesario realizar una o varias interfaces de entrada o salida con un CI. Figura 13: Fotografía del Integrado REFERENCIAS [1] Neil H. E. Weste and Kamran Eshraghian, “Principles of CMOS VLSI design”, Addison-Wesley EEUU (1993) [2] Jan M. Rabaey, Anantha Chandrakasan, Borivoje Nikolic, “Digital Integrated Circuits”, Second Edition, ISBN: 013-090996-3, Prentice Hall (1996) [3] Koyanagi, M. Kurino, H. Kang Wook Lee Sakuma, K. Miyakawa, N. Itani, H. Tohoku Univ., Sendai, “Future system-on-silicon LSI chips,” Micro, IEEE, Jul/Aug 1998 Volume: 18, Issue 4, pp. 17-22. TRATE06-004 Vol. I - Nº 2 - Marzo 2006 22