Universidad de Alcalá I. T. Informática de Sistemas Departamento de Automática

Anuncio

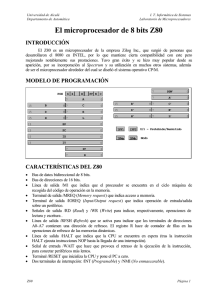

Universidad de Alcalá Departamento de Automática I. T. Informática de Sistemas Laboratorio de Microprocesadores El microprocesador de 8 bits Z80 INTRODUCCIÓN El Z80 es un microprocesador de la empresa Zilog Inc., que surgió de personas que desarrollaron el 8080 en INTEL, por lo que mantiene cierta compatibilidad con este pero mejorando notablemente sus prestaciones. Tuvo gran éxito y se hizo muy popular desde su aparición, por su incorporación al Spectrum y su utilización en muchos otros sistemas, además de ser el microprocesador alrededor del cual se diseñó el sistema operativo CP/M. MODELO DE PROGRAMACIÓN PSW S Z H PV N C 7 A 0 15 B 8 7 C 0 15 D 8 7 E 0 15 H 8 7 L 0 15 SP 0 15 PC 0 15 IX 0 15 IY 0 7 IV 0 7 R 0 7 PSW’ 0 7 A’ 0 15 B’ 8 7 C’ 0 15 D’ 8 7 E’ 0 15 H’ 8 7 L’ 0 IFF1 IFF2 0/1 – Prohibido/Permitido IFMa IFMb 1 Modo CARACTERÍSTICAS DEL Z80 Bus de datos bidireccional de 8 bits. Bus de direcciones de 16 bits. Línea de salida /M1 que indica que el procesador se encuentra en el ciclo máquina de recogida del código de operación en la memoria. Terminal de salida /MREQ (Memory request) que indica acceso a memoria. Terminal de salida /IOREQ (Input/Output request) que indica operación de entrada/salida sobre un periférico. Señales de salida /RD (Read) y /WR (Write) para indicar, respectivamente, operaciones de lectura y escritura . Línea de salida /RFSH (Refresh) que se activa para indicar que los terminales de direcciones A0-A7 contienen una dirección de refresco. El registro R hace de contador de filas en las operaciones de refresco de las memorias dinámicas. Línea de salida /HALT que indica que la CPU se encuentra en espera (tras la instrucción HALT ejecuta instrucciones NOP hasta la llegada de una interrupción). Señal de entrada /WAIT que hace que provoca el retraso de la ejecución de la instrucción, para conectar periféricos más lentos. Terminal /RESET que inicializa la CPU y pone el PC a cero. Dos terminales de interrupción: /INT (Programable) y /NMI (No enmascarable). Z80 Página 1 Universidad de Alcalá Departamento de Automática I. T. Informática de Sistemas Laboratorio de Microprocesadores Señal de entrada /BUSREQ (Bus request) para la petición del bus y señal de salida /BUSACK (Bus acknowledge) para la confirmación de bus cedido que permiten implementar los protocolos de gestión del bus para el DMA y el multiproceso. BITS SIGNIFICATIVOS EN EL REGISTRO DE ESTADO (PSW) C es el indicador de acarreo. N es el indicador de operación de resta, para tenerse en cuenta en las instrucciones de ajuste decimal (DAA). P/V es el indicador de paridad en operaciones de entrada o desplazamiento (si está a 1 indica paridad par) o indica desbordamiento en operaciones aritméticas. H es el bit acarreo auxiliar o acarreo mitad, usado en las instrucciones de ajuste decimal. Z es el indicador de cero. Se pone a 1 si el resultado fue nulo. S es el indicador del signo del resultado. MODOS DE DIRECCIONAMIENTO IMPLÍCITO: El operando está referenciado implícitamente por el código de operación. SCF Pone a 1 el flag C. DE REGISTROS: El propio código de operación indica los registros cuyos contenidos serán los operandos. ADD A,B Suma el contenido del acumulador (A) con el contenido del registro B, dejando el resultado en el acumulador. INMEDIATO: El operando que se incluye en la instrucción (sin ningún símbolo adicional) es el dato a utilizar, que puede ser de uno o de dos bytes. LD C,3Fh Carga el registro C con el número 3Fh. LD HL,1234h Carga el par HL con el dato 1234h. DIRECTO EXTENDIDO: La dirección del dato se da directamente en la instrucción, en los dos bytes que siguen al del código de operación. LD A,(1234h) Carga el acumulador con el dato contenido en la posición 1234h. LD HL,(1234h) Carga el registro L con el contenido de la dirección 1234h y el registro H con el contenido de la dirección 1235h. PÁGINA CERO: Solo se utiliza en la instrucción RST, que salta y continua ejecutando la instrucción contenida en la posición en página cero cuya dirección se incluye en la instrucción, que puede ser 0, 8, 10h, 18h, 20h, 28h, 30h y 38h. RST 10h Carga el PC con el valor 0010h, con lo que se ejecutará la instrucción contenida en esa dirección. RELATIVO: Es utilizado exclusivamente en las instrucciones de salto condicional (Jump relative). El operando de un byte incluido en la instrucción es un offset expresado en complemento a 2 que se suma al contador de programa (PC) actualizado si se cumple la condición, pasando el PC a apuntar a la dirección de continuación del programa. JR Z,7Ah Salta, si el resultado anterior fue cero, a la dirección que resulta de sumar al PC actualizado el número 7Ah en complemento a dos. Z80 Página 2 Universidad de Alcalá Departamento de Automática I. T. Informática de Sistemas Laboratorio de Microprocesadores INDEXADO: Los registros índices IX o IY contienen un dato de 16 bits que, sumado al offset en complemento a 2, que se incluye en la instrucción, permite obtener la dirección efectiva. SUB (IX+34h) Resta al acumulador el contenido de la posición de memoria que se obtiene al sumar 34h al contenido del registro IX. INDIRECTO POR REGISTRO: La dirección del dato (de 16 bits) está almacenada en uno de los pares de registros. OR (HL) Realiza la OR entre el acumulador y el dato contenido en la dirección indicada en el par HL. INTERRUPCIONES La línea /NMI provoca una interrupción no enmascarable (siempre será atendida) y actúa del siguiente modo: 1. Copia IFF1 en IFF2. 2. Pone IFF1 a cero (prohibe las interrupciones enmascarables). 3. Guarda el PC en la pila. 4. Salta a la rutina que comienza en 0066h y que debe finalizar con la instrucción RETN para que se restaure el contenido original de IFF1. La interrupción /INT solo será atendida si IFF1 está a 1 (los biestables IFF1 y IFF2 constituyen la máscara de interrupciones) y puede funcionar de tres modos diferentes (las instrucciones IM0, IM1 e IM2 seleccionan cada uno de ellos): Modo 0: Cuando se produce la interrupción la CPU espera, en el bus de datos, un código de operación que será ejecutado en lugar de la siguiente instrucción de la memoria. Normalmente el código de operación enviado será el de la instrucción RST que producirá un salto a una posición en página cero. Modo 1: Cuando se produce la interrupción se ejecuta la instrucción RST 38h, es decir, comienza a ejecutar el programa que se localice a partir de la dirección 0038h. Modo 2: Al producirse la interrupción, en el bus de datos se espera un vector de 8 bits que constituirá la parte baja de una dirección de memoria, la parte alta de esa dirección deberá encontrarse en el registro IV. La dirección de comienzo de la rutina de atención a la interrupción se obtiene de forma indirecta: byte bajo en (IV[vector]) y byte alto en (IV[vector+1]). EJEMPLOS DE PROGRAMAS PARA EL Z80 Programa que suma sin signo los contenidos de las direcciones 18A0h y 18A1h y guarda el resultado en las posiciones 18B0h y 18B1h. INICIO: FIN: Z80 ORG 1800H LD B,0 LD IX,18A0h LD A,(IX+0) ADD A,(IX+1) LD IY,18B0h LD (IY+0),A LD A,0 ADC A,B LD (IY+1),A HALT END ;Asegura un cero en B ;Dirección del primer dato ;Carga el primer operando ;Suma con el segundo ;Dirección del resultado ;Guarda LSB del resultado ;Acarreo, si existe, a A ;Guarda MSB del resultado Página 3 Universidad de Alcalá Departamento de Automática Programa que inicializa a FFh las posiciones de memoria comprendidas entre la 1880h y 188Fh. INICIO: BUCLE: FIN: BUCLE: ;En B el dato ;A es el contador ;En IX la dirección base ;Actualizamos la posición ;Siguiente dirección ;Contador del bucle ;Salta si no terminó ORG 1800H LD A,00H LD IX,1900H LD (IX+00H),A INC IX INC A CP 20H JP NZ,BUCLE HALT END ;En A el dato y contador ;En IX la dirección base ;Actualizamos la memoria ;Siguiente dirección ;¿Llegó al final ;Si no, salta a BUCLE Programa anterior modificado para que la inicialización se realice en orden inverso (de la 1900h a la 191Fh con los valores 1Fh, 1Eh, ...0). INICIO: BUCLE: ORG 1800h LD B,0FFh LD A,10h LD IX,1880H LD (IX+00H),B INC IX DEC A JP NZ,BUCLE HALT END Programa que inicializa el bloque de memoria entre las direcciones 1900h y 191Fh con los valores 0, 1, 2, ..., 1Fh. INICIO: I. T. Informática de Sistemas Laboratorio de Microprocesadores ORG 1800H LD A,1Fh LD IX,1900H LD (IX+00H),A INC IX DEC A CP 0FFh JP NZ,BUCLE HALT END ;En A el dato y contador ;En IX la dirección base ;Actualizamos la memoria ;Siguiente dirección ;¿Llegó al final ;Si no, salta a BUCLE Programa que copia el bloque de memoria comprendido entre las direcciones 1900h y 191Fh a partir de la dirección 1A00h. INICIO: BUCLE: FIN: Z80 ORG 1800h LD IY,1900h LD IX,1A00h LD A,020h LD B,(IY+0h) LD (IX+0h),B INC IX INC IY DEC A JP NZ,BUCLE HALT END ;En IY dirección origen ;En IX dirección destino ;En A el contador ;Lee el dato ;Copia ;Incrementa índices ;Decrementa contador ;Si no fin, salta a BUCLE Página 4 Universidad de Alcalá Departamento de Automática I. T. Informática de Sistemas Laboratorio de Microprocesadores Programa que localiza el mayor y el menor de los 16 datos de un byte almacenados a partir de la posición 1850h y los almacena, respectivamente, en las posiciones 18A0h y 18B0h. ;Números sin signo INICIO: BUCLE: SALTO1: SIGUE: FIN: ORG 1800h LD IX,1850h LD A,(IX+00h) LD H,A LD L,A LD B,0Fh INC IX LD A,(IX+0h) CP H JP C,SALTO1 LD H,A JP SIGUE CP L JP NC,SIGUE LD L,A INC IX DJNZ BUCLE LD IX,18A0H LD (IX+00H),H LD (IX+10H),L HALT END ;En IX la dirección base ;En A el primer dato ;El mayor en H ;El menor en L ;Contador en B ;Siguiente dirección ;Cargamos otro dato ;Comparamos A-H ;A es menor que H ;A es mayor y se pasa a H ;Comparamos A-L ;A es mayor que L ;A es menor y se pasa a L ;Decrementa B y comprueba ;Actualiza la dirección ;Guarda el mayor ;Guarda el menor ;Números CON signo INICIO: BUCLE: VCEROH: VUNOH: CAMBIAH: SALTO1: VCEROL: VUNOL: CAMBIAL: SIGUE: Z80 ORG LD LD LD LD LD INC LD CP JP JP 1800h IX,1850h A,(IX+00h) H,A L,A B,0Fh IX A,(IX+0h) H Z,SIGUE PE,VUNOH JP JP JP LD JP CP JP JP M,SALTO1 CAMBIAH P,SALTO1 H,A SIGUE L Z,SIGUE PE,VUNOL JP P,SIGUE JP CAMBIAL JP M,SIGUE LD L,A INC IX DJNZ BUCLE LD IX,18A0H ;En IX la dirección base ;En A el primer dato ;Guardamos el mayor en H ;Guardamos el menor en L ;Contador en B ;Siguiente dirección ;Cargamos otro dato ;Comparamos A-H ;Si son iguales, sigue ;Si A>H entonces ;(S)xor(P/V)=0 (S=P/V) ;PE (paridad par, bit ;P/V=1) ;P/V=0 y S=1. A es menor y no hay cambios ;P/V=1 y S=0. A es menor y no hay cambios ;A es mayor y se pasa a H ;Comparamos A-L ;Si son iguales, sigue ;Si A<L entonces ;(S)xor(P/V)=1 (S<>P/V) ;PE (paridad par, bit P/V a 1) ;P/V=0 y S=0. A es mayor y no hay cambios ;P/V=1 y S=1. A es mayor y no hay cambios ;A es menor y se pasa a L ;Decrementa B y repite si ;no es cero ;Actualiza la dirección Página 5 Universidad de Alcalá Departamento de Automática FIN: LD (IX+00H),H LD (IX+10H),L HALT END I. T. Informática de Sistemas Laboratorio de Microprocesadores ;Guarda el mayor ;Guarda el menor Programa que suma dos datos de 8 bytes que comienzan en las posiciones 1850h y 1860h y almacena el resultado a partir de la dirección 18A0h. Como el Z80 almacena los datos en memoria con los bytes de pesos mayores en las direcciones mayores, en caso de producirse acarreo final, este deberá almacenarse en la dirección 18A8h, si no hay acarreo, deberá ponerse a cero. INICIO: BUCLE: FIN: ORG 1800h LD IX,1850h LD B,08h SCF CCF LD A,(IX+00h) ADC A,(IX+10h) LD (IX+50h),A INC IX DJNZ BUCLE LD A,0 ADC A,0 LD (IX+50h),A HALT END ;En IX la dirección base ;En B el contador de bytes ;Carry a 1 ;Complementación del carry ;En A byte del primer ;Guarda byte del resultado ;No afecta al carry ;Decrementa B y repite si no es cero ;Guarda byte de mayor peso REPERTORIO DE INSTRUCCIONES El repertorio de instrucciones del Z80 es, probablemente, uno de los más completos y complejos de los microprocesadores de su categoría, además de mantener la compatibilidad con el juego del 8080. (Ver hojas adjuntas). Z80 Página 6 Universidad de Alcalá Departamento de Automática Z80 I. T. Informática de Sistemas Laboratorio de Microprocesadores Página 7 Universidad de Alcalá Departamento de Automática Z80 I. T. Informática de Sistemas Laboratorio de Microprocesadores Página 8 Universidad de Alcalá Departamento de Automática Z80 I. T. Informática de Sistemas Laboratorio de Microprocesadores Página 9 Universidad de Alcalá Departamento de Automática Z80 I. T. Informática de Sistemas Laboratorio de Microprocesadores Página 10 Universidad de Alcalá Departamento de Automática Z80 I. T. Informática de Sistemas Laboratorio de Microprocesadores Página 11 Universidad de Alcalá Departamento de Automática Z80 I. T. Informática de Sistemas Laboratorio de Microprocesadores Página 12 Universidad de Alcalá Departamento de Automática Z80 I. T. Informática de Sistemas Laboratorio de Microprocesadores Página 13 Universidad de Alcalá Departamento de Automática Z80 I. T. Informática de Sistemas Laboratorio de Microprocesadores Página 14 Universidad de Alcalá Departamento de Automática Z80 I. T. Informática de Sistemas Laboratorio de Microprocesadores Página 15 Universidad de Alcalá Departamento de Automática Z80 I. T. Informática de Sistemas Laboratorio de Microprocesadores Página 16 Universidad de Alcalá Departamento de Automática Z80 I. T. Informática de Sistemas Laboratorio de Microprocesadores Página 17