Task Switch y Scheduling

Anuncio

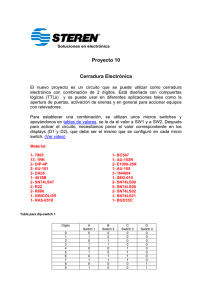

Menú del dı́a Task Switch y Scheduling 1 Task Switch à la Intel 2 Task Switch a mano 3 Carga de tareas Alejandro Deymonnaz Progrmación Sistemas Operativos 14 de Abril de 2011 - 1c2011 Sabi (PSO - DC) Task Switch y Scheduling 14 de Abril de 2011 1 / 24 Sabi (PSO - DC) Task Switch à la Intel Task Switch y Scheduling 14 de Abril de 2011 2 / 24 Task Switch à la Intel Definiciones Estructura de una tarea El procesador Intel está diseñado teniendo en cuenta el concepto de tarea. En este diseño, una tarea involucra: Un TSS o Task-State Segment (valores de los registros) Estructura de una tarea El descriptor de la TSS. El selector o Task Register (TR) de la tarea actual. Segmento de código de la tarea. Segmento de datos de la tarea. Segmentos de stack de la tarea. Un directorio de tablas de página (CR3). Sabi (PSO - DC) Task Switch y Scheduling 14 de Abril de 2011 3 / 24 Sabi (PSO - DC) Task Switch y Scheduling 14 de Abril de 2011 4 / 24 Task Switch à la Intel Task Switch à la Intel Task-State Segment Task-State Segment (cont.) El estado de una tarea consiste en su memoria y los valores de sus registros. Especı́ficamente: Con todos los registros guardados en el TSS, más las páginas de memoria alcanzables desde el CR3 se define el estado de una tarea. Los 8 registros de propósito general. Selectores de segmento: cs, ss, ds, es, fs, gs Pará, pará, pará, ¿y la pila de nivel 3? En ss:esp se guarda la pila actual, que puede ser Los flags (EFLAGS), el Instruction Pointer (EIP) y un Task link. La pila de nivel 3, si la tarea se encuentra ejecutando en nivel 3. La pila de otro nivel, si la tarea se encuentra dentro de alguna interrupción. Acá la pila de nivel 3 está guardada en el stack de la interrupción. El directorio de tablas de página (CR3) Las pilas de nivel 0, 1 y 2, (ssN y espN). Task-State Segment de 32 bits Sabi (PSO - DC) Task Switch y Scheduling 14 de Abril de 2011 Sabi (PSO - DC) 5 / 24 Task Switch à la Intel Task Switch y Scheduling 14 de Abril de 2011 6 / 24 Task Switch à la Intel Preguntas Task Switch - jmp far ¿Cómo sabemos en qué nivel de privilegio está ejecutando una tarea, mirando su estado? Por el valor del RPL del selector de código cs que está en la TSS. El procesador define todo esto (TSS, etc.) porque provee una forma de hacer cambio de tareas en hardware, entre otras formas, con la instrucción jmp 1 : jmp far sel:offset Esta instrucción, dependiendo de sel hace: un far jump a un segmento de código (conforming o no). un far jump usando una Call Gate. un task switch. 1 Sabi (PSO - DC) Task Switch y Scheduling 14 de Abril de 2011 7 / 24 Vea “Far Jumps in Protected Mode” en la instrucción jmp del Volumen 2A. Sabi (PSO - DC) Task Switch y Scheduling 14 de Abril de 2011 8 / 24 Task Switch à la Intel Task Switch à la Intel Task Switch - jmp far Task Switch - qué hace el procesador ¿Qué valor debe tener sel? Veamos: Un TSS o Task-State Segment es un segmento, como lo es el de código. La ejecución (etapa “execute”) de la instrucción jmp far a un descriptor de TSS hace lo siguiente: Un TSS tiene un descriptor de TSS en la GDT que lo define. Cada tarea tiene su TSS y su descriptor de TSS en la GDT. jmp far hace un cambio de tarea, si sel es un selector de un descriptor de TSS. ¿y qué valor debe tener offset? 1 Guarda los registros de la tarea actual en el TSS correspondiente. 2 El EIP en el TSS lo asigna a la instrucción siguiente al jmp far. 3 Carga los registros de la nueva tarea desde la TSS 4 Ahora la tarea actual es la nueva. En el medio, realiza los checkeos (segmentos válidos, presentes, etc) y falla en caso contrario. CUALQUIERA El valor de offset se ignora. El procesador siempre usa el segmento de TSS entero. Sabi (PSO - DC) Task Switch y Scheduling 14 de Abril de 2011 9 / 24 Sabi (PSO - DC) Task Switch à la Intel Task Switch y Scheduling 14 de Abril de 2011 10 / 24 Task Switch à la Intel Task Switch - Tarea actual Task Switch - Dinámica Una única tarea utiliza el CPU en cada momento, la tarea actual, hasta que debe desalojarse por motivos como: Agotó su tiempo de CPU (proveer concurrencia sin necesidad de simultaneidad) Como está definido el concepto de tarea, existe también en el procesador la idea de la tarea actual. Se decide pasar a otra tarea de mayor prioridad (scheduler con prioridades) Se bloqueó o terminó Tarea actual La tarea actual es la que está en el descriptor de TSS apuntado por el Task Register Siempre se pasa el CPU a otra tarea. Nunca se vuelve. Si no hay más, entonces siempre hay una IDLE TASK para ejecutar. Importante: La decisión de cambiar de tarea se produce en el kernel (anillo 0). El kernel decide y el hardware hace todo el cambio de contexto. Cuando se quiera volver a ejecutar una tarea se pasa de nuevo a el TSS de esa tarea. Sigue ejecutando donde diga el EIP (la instrucción siguente al jmp far). Task Register Sabi (PSO - DC) Task Switch y Scheduling 14 de Abril de 2011 11 / 24 Sabi (PSO - DC) Task Switch y Scheduling 14 de Abril de 2011 12 / 24 Task Switch à la Intel Task Switch a mano Alternativas relacionadas Del dicho al hecho Se puede hacer un call a una tarea, lo que involucra las tareas Busy y los Task Link para poder volver a una tarea anterior. No lo vamos a usar. Se puede hacer cambio de contexto para atender interrupciones (IDT) Todo lo definido por Intel permite un control muy detallado de las tareas con ayuda del procesador. Pero... ...el uso que se le dió es más simple: Modelo de segmentación FLAT 2 . Todos los selectores de datos apuntan al mismo único segmento de datos del nivel correspondiente. Se usan sólo dos niveles de privilegio: Usuario (anillo 3) y supervisor (anillo 0), a la unidad de paginación. Habiendo pocos segmentos (acotados en cantidad), no se usa la LDT. No se usan las Call Gates, todo pasa por interrupciones. La protección de memoria se hace en la unidad de paginación. Task Gate Descriptor 2 Sabi (PSO - DC) Task Switch y Scheduling 14 de Abril de 2011 13 / 24 Vea Sección 3.2 Using Segments del Volumen 3A del manual Sabi (PSO - DC) Task Switch a mano Task Switch y Scheduling 14 de Abril de 2011 14 / 24 Task Switch a mano Situación del TSS Alternativa a la TSS De las 26 palabras obligatorias de la TSS, no se usan (son los mismos valores para todas las tareas): Una alternativa es no usar el mecanismo de cambio de tarea del procesador. ¿Cómo cambiamos la tarea entonces? Las 6 de selectores Las 4 correspondientes a stack de nivel 1 y nivel 2. “A mano”: Los valores a guardar de la tarea se salvan en el PCB (ej: cr3, esp0, ss0, etc.), o en el stack de anillo 0 de la tarea (ej: registros, EFLAGS). El Previous Task Link (PTL) El selector de LDT. Algunos registros de propósito general: varios ya son salvados por convención al entrar en la interrupción. Aprox la mitad del TSS no se usa. El cambio de tarea se hace reemplazando (con mov) los valores de los registros por los guardados en el PCB de la tarea nueva. Al volver de la interrupción (volver a anillo 3) el procesador tendrá el CR3 de la tarea nueva, con los registros restaurados de la pila nueva. Task-State Segment de 32 bits Sabi (PSO - DC) Task Switch y Scheduling 14 de Abril de 2011 15 / 24 Sabi (PSO - DC) Task Switch y Scheduling 14 de Abril de 2011 16 / 24 Task Switch a mano Task Switch a mano Ventajas vs desventajas Apagar Task Switch Desventajas: El cambio de tarea involucra muchas instruciones (mov), que requieren ser ejecutadas. Se pierde la posiblidad de usar Task Gate para interrupciones y call far. El mecanismo de task switch del procesador no se puede apagar. El procesador está diseñado para usarlo. Ejemplo: qué pasa ante una interrupción con cambio de nivel de privilegio. Ventajas: Se ahorran accesos a memoria (que harı́a el jmp far) para los registros que no cambian o ya fueron salvados (selectores, algunos de propósito general, etc.) Se ahorran accesos de los registros que no se usan (pila 1 y 2). No hay necesidad de administrar un TSS (y su descriptor en la GDT) para cada tarea. Se ahorran registros como EIP. Sabi (PSO - DC) Task Switch y Scheduling 14 de Abril de 2011 Sabi (PSO - DC) 17 / 24 Task Switch a mano 14 de Abril de 2011 18 / 24 Task Switch a mano El TSS siempre está Dinámica del cambio 1 2 La pila del handler se obtiene desde el TSS actual de la tarea actual (TR). 3 Necesitamos un TSS, su descriptor y el TR. 4 Con un único TSS alcanza para todas las tareas, pero hay que guardar al momento del task switch los valores que el procesador espera encontrar allı́: la pila de anillo 0 (cada tarea tiene su pila de anillo 0). 5 6 7 8 9 10 Sabi (PSO - DC) Task Switch y Scheduling Task Switch y Scheduling 14 de Abril de 2011 19 / 24 Llega la interrupción que deriva en la necesidad de un cambio de contexto. Por convención C, el pre-handler (en Assembler) salva eax, ecx y edx si es necesario (depende si es syscall o interrupción). La única función que hace el cambio de tarea (ej: switchto) guarda los demás registros de propósito general (en la pila, o en el PCB). Algunos registros sólo se leen del PCB (ej: CR3, CS, SS, ...) Se guarda la pila de nivel 0 en el PCB. No se puede usar más la pila de la tarea anterior. Se cambia el CR3 por el de la tarea nueva. Se carga la pila de nivel 0 desde el PCB nuevo. Hay que guardar el nuevo pid en algún registro, antes de perder la pila anterior. Se desapila y/o restaura desde el PCB todos los registros. Se actualiza el TSS con los valores que el procesador espera encontrar. Se vuelve de la función switchto, ya en otro contexto. Sabi (PSO - DC) Task Switch y Scheduling 14 de Abril de 2011 20 / 24 Carga de tareas Carga de tareas Inicialización Memoria Para tener tareas hay que crear las tareas. Dependiendo del mecanismo de cambio de tarea hay que realizar la inicialización correspondiente. Una nueva tarea tiene su propia memoria. Hay que reservar: páginas para el directorio de tablas de página y las tablas de página. Para el task switch à la Intel, hay que inicializar el TSS de la tarea y su descriptor con los valores de los registros. páginas para el código de la tarea. Para el otro caso, hay que inicializar los valores en el PCB (los que correspondan) y en la pila de nivel 0, como si la tarea estuviera detenida dentro de switchto dentro de alguna interrupción. páginas para la pila de nivel 3. Sabi (PSO - DC) Task Switch y Scheduling 14 de Abril de 2011 21 / 24 páginas para la pila de nivel 0. Además, hay que copiar datos en muchas de esas páginas. Sabi (PSO - DC) Carga de tareas Task Switch y Scheduling 14 de Abril de 2011 22 / 24 Carga de tareas Memoria - problema Inicialización de registros Al comienzo de la tarea algunos registros que ve el usuario como eax pueden tener cualquier valor, pero otros no: Problema: La tarea se inicializa desde el anillo 0 de otra tarea. No todas las páginas fı́sicas son accesibles desde esta otra tarea (sólo los primeros 4MB). Solución: Ciertas estructuras comunes a todas las tareas (los PCB, memoria para pipes, buffers de handlers de hardware, etc) están visibles con identity mapping en todas las tareas. Las demás páginas no. Para inicializar otra tarea, mapeamos temporalmente al directorio de la tarea actual cada página que necesitemos para copiar o inicializar datos allı́ y luego la quitamos y mapeamos en su lugar definitivo del directorio de la otra tarea. Sabi (PSO - DC) Task Switch y Scheduling 14 de Abril de 2011 23 / 24 Pila de nivel 3 (esp y ebp) deben apuntar a la dirección donde reservamos la pila. EFLAGS, debe tener las interrupciones habilitadas en anillo 3. Sabi (PSO - DC) Task Switch y Scheduling 14 de Abril de 2011 24 / 24