TEMA 2 ENTRADA / SALIDA Contenido Interfaz HW de E/S

Anuncio

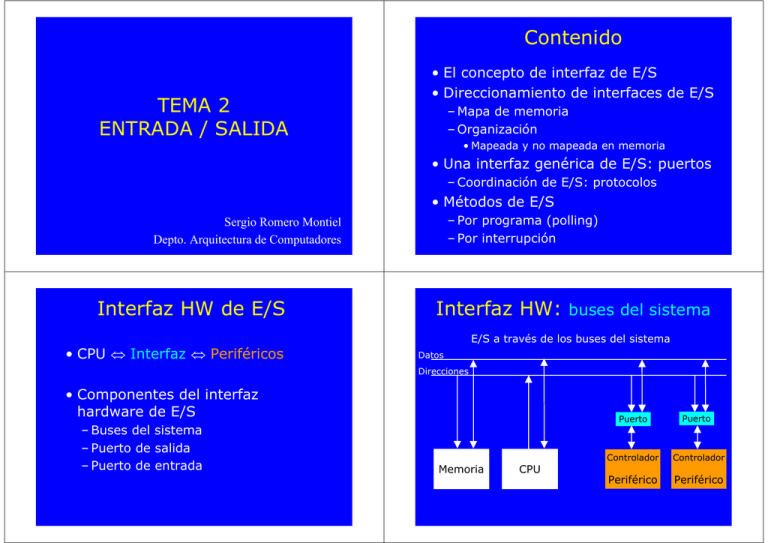

Contenido TEMA 2 ENTRADA / SALIDA • El concepto de interfaz de E/S • Direccionamiento de interfaces de E/S – Mapa de memoria – Organización • Mapeada y no mapeada en memoria • Una interfaz genérica de E/S: puertos – Coordinación de E/S: protocolos • Métodos de E/S – Por programa (polling) – Por interrupción Sergio Romero Montiel Depto. Arquitectura de Computadores Interfaz HW de E/S Interfaz HW: buses del sistema E/S a través de los buses del sistema • CPU ⇔ Interfaz ⇔ Periféricos Datos Direcciones • Componentes del interfaz hardware de E/S – Buses del sistema – Puerto de salida – Puerto de entrada Memoria CPU Puerto Puerto Controlador Controlador Periférico Periférico Interfaz HW: puerto de salida INTERIOR Señales internas de datos Interfaz HW: puerto de entrada EXTERIOR INTERIOR EXTERIOR D0 Q0 D0 I0 D1 Q1 D1 I1 D2 Q2 D2 I2 D3 Q3 D3 I3 D4 Q4 D4 I4 D5 Q5 D5 I5 D6 Q6 D6 I6 D7 Q7 D7 I7 Señales accesibles desde el exterior Señales internas de datos EN EN Señales producidas en el exterior Los interruptores se implementan con puertas triestado Direccionamiento de Interfaces Direccionamiento de Interfaces DIAGRAMA DE BLOQUES MAPA DE DIRECCIONES: ejemplo I E/S mapeada en memoria Datos Direcciones R/W 2n 0 1 2 . . . 2n-1 Memoria CPU Puerto 2n+1 Puerto Controlador Controlador Periférico Periférico Buses del sistema: dirección, datos y control E/S mapeada en memoria 0 1 2 . . . . . . . . . . . . 2(n-1)-1 2(n-1) . . . . . . . 2(n-1)+2(n-2)-1 (n-1) (n-2) 2 +2 . . . . . 2n-1 | n bits | 000............00 000............01 000............10 ½ del espacio de direccionamiento para la memoria Memoria 011............11 100............00 100............01 E/S 101............11 110............00 110............01 no usado 111111111111 1/4 del espacio de direccionamiento para E/S 1/4 del espacio de direccionamiento no utilizado Direccionamiento de Interfaces E/S mapeada en memoria Direccionamiento de Interfaces E/S no mapeada en memoria MAPA DE DIRECCIONES: ejemplo II | n bits | 000............00 000............01 000............10 Memoria 001............11 010............00 011............11 100............00 101............11 110...00.....00 110...00.....01 110...00.....10 E/S |m bits| 110..001.....11 110..010.....00 110..010.....01 no usado 1111110.....00 1111111.....11 Datos 3·2(n-2) posiciones del espacio de direcciones para la memoria Direcciones IO_R/W R/W 0 2m posiciones del espacio de direcciones para E/S Resto de posiciones no utilizadas Direccionamiento de Interfaces E/S no mapeada en memoria 0 1 2 . . . 2n-1 Memoria Controlador Controlador Periférico Periférico puerto de salida INTERIOR A0-A15 ALE 111............11 Espacio de direccionamiento de E/S Puerto EXTERIOR D0-D7 Espacio de direccionamiento de la memoria Memoria 1 Direccionamiento de Interfaces Address Decoder EQUAL | m bits | 000.........00 000.........01 000.........10 E/S 111.........11 0 1 2 . . . . 2m-1 CLK 0 1 2 . . . . . . . . . . . . 2n-1 Puerto Buses del sistema: dirección, datos y control MAPA DE DIRECCIONES DE MEMORIA Y DE E/S | n bits | 000............00 000............01 000............10 CPU 74374 0 1 2 . . 2 (n-2)-1 2 (n-2) . . . . 2 (n-1)-1 2 (n-1) . . 2(n-1)+2(n-2)-1 2(n-1)+2(n-2) . . . . . . . 2(n-1)+2(n-2)+2(m) -1 2(n-1)+2(n-2)+2(m) . . . . . 2n-1 M/IO WR Señales visibles desde el exterior WR RD A2-A15 ALE wr rd RDS RCD Address Decoder RDE EQUAL A0 A1 RSD A0 A1 CS Ejemplo de interfaz de impresora Data wr rd EXTERIOR Printer Data Register A0 A1 7 0 7 0 Printer Status Register A0 A1 BSY ACK PE SL ERR IRQ Printer Control Register A0 A1 D IQ SI IN AF A0 A1 CS M/IO ST read or last written write IMPRESORA D0-D7 Dependiente del dispositivo Controlador de periférico de 4 puertos Direccionamiento de Interfaces Comunicación con la impresora Direccionamiento de Interfaces Direccion base: 278h, 378h Interfaz E/S Software Los protocolos de E/S pueden ser SW ó HW. Los más simples pueden implementarse en HW. Los complejos y más habituales son SW. Protocolo PC-Impresora (ej.) Las señales de datos y strobe las genera el procesador Las señales busy y ack las envía la impresora ¿Eres la impresora? Si, soy yo D7-D0 ¿Estas lista? Preparada para recibir datos Primer dato CPU Recibido IMPRESORA STROBE BUSY ACK dato dato Métodos de E/S E/S mediante ‘polling’ Bloqueante No Bloqueante Polling (sondeo) • Bloqueante: el procesador espera a que el periférico esté listo (perdida de tiempo en el procesador) • No bloqueante: el procesador continua con otra tarea y atiende al periférico al terminar (perdida de tiempo en el periférico) PROGRAMA PROGRAMA NO NO Interrupción • Permite al procesador trabajar en otra tarea mientras el periférico está ocupado • Es necesario que el procesador disponga de un mecanísno que le permita recibir y atender interrupciones E/S mediante Interrupciones El periférico “interrumpe” cuando ocurre un evento que debe ser tratado PROGRAMA Rutina de tratamiento de la interrupción (RTI) PROGRAMA Al finalizar la RTI, la CPU sigue la ejecución del programa por donde estaba antes de la interrupción Está listo el periférico? SI Rutina de tratamiento del periférico Está listo el periférico? SI Rutina de tratamiento del periférico Origen de las Interrupciones • Interrupciones HW internas (excepciones) – División por cero, desbordamiento, etc • Interrupciones HW Externas – Pines INTR, INTA – PIC (IRQ’s) • Interrupciones software o simuladas (int) – Servicios BIOS (int 10h), DOS (int 21h) Determinación de la Interrupción Interrupciones Externas Multiples • Vectorizadas – Requiere de un controlador que proporciona el número de la interrupción (vector) – El vector determina quién produce la interrupción y dónde está la rutina de tratamiento CPU • Autovectorizadas Periférico Periférico Periférico Periférico – El vector es conocido, ya que la interrupción se produce por un pin dedicado CPU . . . . . . . . . . . . Periférico Periférico • No vectorizadas – Siempre se ejecuta la misma rutina que determina mediante polling al perif. causante Reconocimiento de la Interrupción Varias lineas de petición de interrupción (autovectorizada) Reconocimiento de la Interrupción INICIO I=1 ES EL PERIFÉRICO I-ÉSIMO Periférico 2 CPU . . . SI NO . . . I=I+1 RUTINA DE TRATAMIENTO PARA EL PERIFÉRICO I-ÉSIMO Periférico N NO I>n Bus de datos vector Periférico 1 SI FIN Reconocimiento de intr.’s por sondeo (no vectorizadas) CPU Controlador de Interrupciones Bus de datos Una línea de petición de interrupción Periférico 1 Periférico 2 . . . . . . Periférico N INICIO EL CONTROLADOR DE INTERRUPCIONES INDICA QUE SE TRATA DEL PERIFÉRICO I-ÉSIMO (VECTOR=I) RUTINA DE TRATAMIENTO PARA EL PERIFÉRICO I-ÉSIMO FIN Controlador de Interrupciones Inteligente ó Programable Interrupciones vectorizadas Gestión de Prioridades Procesamiento de la Interrupción – Siempre toman el control de la CPU cuando se producen (errores fatales) 1. El dispositivo envía una señal de interrupción 2. Se termina de ejecutar la instrucción en curso 3. La CPU envía una señal de reconocimiento de la interrupción 4. La CPU guarda la información necesaria para continuar el programa en curso (PC y FLAGs) 5. Se carga el PC con la dirección de la rutina de tratamiento de la interrupción (RTI) 6. La RTI guarda el resto del estado del sistema 7. La RTI procesa la interrupción 8. La RTI recupera el estado del sistema 9. La RTI devuelve el control al programa E/S en el 8086 El 8086 por dentro y por fuera – Con prioridades: SW y HW – Sin prioridades – Concepto de máscara de interrupción • Enmascaramiento por niveles • Enmascaramiento individual (registro de máscara) – Controlador de Interrupciones Programable • PIC (intel 8259), prioridades HW • No enmascarables (NMI) • El 8086 maneja E/S no mapeada en memoria: – Posee líneas control para seleccionar la memoria o los periféricos de E/S – Posee instrucciones (IN, OUT) para leer y escribir de/en los puertos de los periféricos – Posee líneas de interrupción • La E/S de vídeo (memoria de video) se realiza mediante mapeo en memoria Diagrama de bloques de 8086 DATA, INDEX & SEGMENT POINTER REGS REGISTERS & (8 WORDS) IP (5 WORDS) 16 BIT ALU FLAGS BUS INTERFACE UNIT 6-BYTE INSTRUCTION QUEUE CONTROL & TIMING ADDRESS DATA Configuración de PINES GND AD14 AD13 AD12 AD11 AD10 AD9 AD8 AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0 NMI INTR CLK GND 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 8086 • Enmascarables 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21 Vcc AD15 A16/S3 A17/S4 A18/S5 A19/S6 BHE/S7 MN/MX RD HOLD HLDA WR M/IO DT/R DEN ALE INTA TEST READY RESET Interrupciones en el 8086 • Posee dos líneas para interrupciones HW externas – INTR (INTerrupt Request): • Enmascarable (IF, interruption flag) • Vectorizada (tamaño del vector: 1 byte,256 int.’s) – NMI (Non Maskable Interrupt): • No enmascarable • Autovectorizada (Vector = 02h) • Las interrupciones internas (excepciones) son los vectores de 00h a 07h • Las interrupciones SW se invocan con la instrucción INT vector, ej.: INT 21h Interconexión 8086-8259 El PIC 8259 Controlador de Interrupciones Programable (o PIC 8259) es el microchip de intel que se utiliza con el 8086 – 8 líneas de petición de interrupción (IRQ0-7) – Proporciona el vector de interrupción al 8086 (vector base programable) – Pueden conectase el cascada (en dos niveles, hasta 64 interrupciones) – Gestiona las prioridades (programable) – Permite enmascarar las interrupciones individualmente Modo de operación del 8259 16 Bus de direcciones Bus de datos 16 8 A0-19 D0-15 M/IO ¿20h-21h? cs 8086 rd wr INTR INT INTA INTA a0 data 8259 El 8259, como periférico que es, se conecta a la CPU por los buses de dirección, datos y control asignandosele una dir. base de E/S En este ejemplo la dirección base es 20h Posee 3 registros: IRR, ISR (solo lectura, dir.base), IMR (lectura y escritura, dir base+1) Se puede escribir una palabra de control sobre la dirección base Bus de datos 8 D0-15 Periférico 1 IRQ0 IRQ1 8086 INTR INTA INTR INTA 8259 20 IRQ7 Periférico 2 . . . . . . Periférico 8 Un periférico genera una señal de interrupción Si no está enmascarada y no hay otra de mayor prioridad ejecutandose, el 8259 envía la señal INTR al 8086 Si IF está a 1, el 8086 acepta la interrupción y envía INTA al 8259 El 8259 vuelca sobre el bus de datos el vector correspondiente Acceso a la RTI Bus de direcciones 20 Bus de datos Tabla de Vectores de Interrupción Con el número de vector NV la ALU calcula la posición en la tabla de vectores de interrupción (NVx4) 16 A0-19 D0-15 En dicha posición de memoria se encuentra un puntero a la rutina de tratamiento (RTI) MEMORIA Se guarda en la pila los flags, CS e IP y el puntero lejano leido se carga en CS e IP 8086 8259 en cascada Ocupa el primer 1kbyte de memoria (00000h-003FFh) Contiene 256 punteros lejanos (4 bytes, CS:IP) a RTI La tabla de vectores se puede modificar simplemente escribiendo en la posición adecuada un nuevo valor de puntero a RTI Es recomendable restaurar los valores originales de la tabla de vectores antes de finalizar un programa que haya modificado dichos valores Bibliografía 16 Bus de datos 8 D0-15 Dir. Base Maestro: 020h INTA INTR INTA IRQ7 IRQ0 . . . 8259 8086 INTR Periférico 2 IRQ0 IRQ1 IRQ2 8259 Dir. Base Esclavo: 0A0h Periférico 1 8 IRQ7 15 periféricos, el periférico de IRQ2 es el PIC esclavo • William Stallings – Organización y Arquitectura de Computadores, 5ª Edición – Prentice Hall Periférico 9 . . . Periférico 16 Periférico 8 • Patterson, Hennessy – Estructura y Diseño de Computadores – Editorial Reverté