examen final d`ic

Anuncio

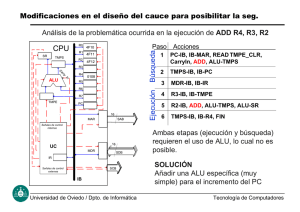

EXAMEN FINAL D’IC CURS 2004-2005 Q1 20 DE GENER DE 2005 • Duració de l’examen 2 hores i 30 minuts. • Els problemes 1 i 4 s’han de resoldre en els FULLS D’EXAMEN. Els problemes 2 i 3, en FULLS SEPARATS. • No es pot fer servir calculadora, ni mòbil ni apunts. • La solució de l’examen sortirà publicada al “Racó” demà a la tarda. • Les notes es publicaran el 31 de gener. • La revisió es realitzarà el dia 1 de febrer a les 15:00 a l’aula D6004, i les notes definitives es publicaran el 2 de febrer. Pregunta 1. (1.5 punts) (Objetivo 4.8) k C4 l R2 C3 j g R1 OUT a IN b c C1 d h f C2 i e El siguiente circuito secuencial está inmerso en un sistema más complejo. Se sabe que la entrada IN viene directamente de un registro, que podemos denominar RIN, y que la salida OUT va directamente a otro registro, que podemos denominar ROUT. Vamos a calcular el tiempo de ciclo mínimo del sistema suponiendo que el camino crítico del sistema pasa por este circuito. En el circuito los bloques C1, C2, C3 y C4 son combinacionales y R1 y R2 son registros. Clk Preguntas a) Para obtener el camino crítico primero tienes que obtener todos los posibles caminos de este circuito. Indica en la siguiente tabla cada camino escribiendo los bloques combinacionales y registros involucrados en el camino, separados por flechas. Numera los posibles caminos. Camino 1 2 … Ci Æ Cj … Apellidos y Nombre: ……………………………………………………………. b) El tiempo de propagación de los bloques combinacionales que hay en este circuito es el siguiente (TCi n-m indica el tiempo de propagación del bloque Ci desde la entrada n a la salida m, que se mide en unidades de tiempo, u.t.): Bloque C1 TC1 u.t. a-d 40 b-d 50 c-d 10 Bloque C3 TC3 u.t. g-j 20 h-j 70 Bloque C2 TC2 u.t. i-e 30 i-f 60 Bloque C4 TC4 u.t. k-l 80 El tiempo de propagación de cualquier registro del sistema (RIN, R1, R2, ROUT) es de 100 u.t. Escribe en la siguiente tabla el tiempo de cada uno de los posibles caminos que has encontrado en la pregunta anterior, indicando los sumandos y la suma total. … TCi x-y + TCj p-q … Camino 1 Tcamino 2 c) ¿Cuál es el camino crítico del sistema? d) ¿Cuál es el tiempo de ciclo mínimo del sistema? Pregunta 2. (2.5 punts) Ens demanen que dissenyem un circuit lògic seqüencial que calculi la part entera del logaritme neperià d’un valor codificat amb 8 bits i mantingui el resultat a la sortida durant 3 cicles de clock. X INICI 1 CLK 8 INT(ln X) 1 FI 3 LNX Donada la complexitat del circuit el disseny s’ha dividit en subcircuits més simples de la següent manera: INICI X 1 8 iniCalc 1 SLS1 1 fiCalc SLS2 ldRes 3 CLK load 1 1 Res REGISTRE 3 FI LNX Tenint en compte que: - INICI és un senyal que es posa a 1 indicant que X estarà disponible en el següent cicle. Si INICI es posa a 1 durant el càlcul s’ignora. SLS1 posa el senyal iniCalc a 1 durant només un cicle indicant a SLS2 que el valor X que hi ha en aquest moment és el valor sobre el qual es vol fer el càlcul. SLS2 triga més d’un cicle en calcular el resultat SLS2 posa el senyal fiCalc a 1 durant un únic cicle indicant que el resultat de l’operació està disponible a Res durant aquell mateix cicle Com que SLS2 no manté el resultat durant més d’un cicle cal afegir REGISTRE per mantenir el resultat durant 3 cicles de rellotge tal com demana l’enunciat El senyal FI només s’ha de posar a 1 durant els tres cicles en els que el resultat està disponible a la sortida El senyal INICI es pot posar a 1 durant l’últim cicle de l’operació anterior (l’últim dels tres cicles on mostrem el resultat) indicant que comença una nova operació Trobeu el graf de Moore de SLS1 utilitzant la següent llegenda: (objectiu 4.6) INICI fiCalc NOM ESTAT iniCalc LdRes FI NOTA: no us preocupeu pels noms dels estats, podeu anomenar-los E0, E1, E2, etc. Pregunta 3. (4 punts) (Objectiu 9.5) Volem afegir dues noves instruccions al llenguatge màquina SISA-I: DOBZ Rd, Offset; Decrement One and Branch on Zero DOBNZ Rd, Offset; Decrement One and Branch on Not Zero La primera instrucció decrementa una unitat el valor que conté el registre Rd, guarda el resultat en aquest mateix registre i si el nou valor és zero, fa un salt a PC+Offset. Rd=Rd-1; if (Rd=0) then PC=PC+ExtSgn(Offset) else PC=PC+1 La segona instrucció funciona de la mateixa manera, però salta quan el resultat del decrement és diferent de zero. Rd=Rd-1; if (Rd<>0) then PC=PC+ExtSgn(Offset) else PC=PC+1 Offset és un nombre enter codificat en Ca2 amb 8 bits. Es demana: a) Codificació de les dues noves instruccions. b) Modificacions que s’han de fer a l’ALU i a la Unitat de Procés del SISP-I-1. (Dibuixeu les parts del circuit que varien o que afegiu. Les parts que no són afectades per les noves instruccions, no cal que les dibuixeu). c) Modificacions que s’han de fer a la Lògica de Control del SISP-I-1. (Dibuixeu les parts del circuit que varien o que afegiu. Les parts que no són afectades per les noves instruccions, no cal que les dibuixeu). d) El següent codi fa una còpia d’un vector. Escriu de nou una versió modificada del codi que faci servir la instrucció DOBNZ, de manera que es mantingui la seva funcionalitat i es redueixi el número d'instruccions a 10: .data a: .word 30,1,-3,128,0,671,-23,30,-100,78 b: .space 10 .text MOVI R0,10 MOVI R1,lo(a) MOVHI R1,hi(a) MOVI R2,lo(b) MOVHI R2,hi(b) bucle: LD R3,0(R1) ST 0(R2),R3 ADDI R0,R0,-1 DDI R1,R1,1 ADDI R2,R2,1 NZ R0,bucle .end e) Quants cicles triga en executar-se el codi original al processador SISP-I-1, i quants trigarà la versió modificada? f) Suposant que implementéssim les noves instruccions al processador SISP-I-2, i que s’executessin en dos cicles, quants cicles trigaria en executar-se el codi original al processador SISP-I-2, i quants la versió modificada? Y e X ALU X Y MVI X Y F CMP A DD X Y AL F 3 F b0 b1 b2 OP 3 7 6 5 4 3 2 1 0 MUX z z 0 1 2 W SISP-I-1 z +1 OP e Tk nBr W rIO WrM In/Ld InL d/Alu W rD @D @A F Rb/I @B IMME D @IO !C lk I NSTRU CTI ON M EMORY REG 1 0 MUX C lk PC + PC ADDR -INS Tk nBr ADD OP e Tk nBr W rIO W rMem In/ Ld InL d/Alu W rD @D @A F Rb/I @B IMMED @IO 8- SE R D-INS INS Ins t ructio n In/ Ld 1 0 M UX InL d/Alu 1 0 M UX !Clk WrIO W rD Clk D WrD RD-D ATA @D @D WrM !Clk R D-IO INPU T/ OU TP UT DataRdM z DataRdIO SISP-I- 1 CONTROL LOGIC Clk R EGFIL E @A @A @B @B A W r-Io B A D ATA M EMOR Y W r-D at a B W R-IO R D-D ATA IMMED R b/ I AD DR -IO @IO X z 1 0 M UX Y ADDR-DATA F e OP z ALU ALUou t F e OP b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0 b15 b14 b13 b12 INS IMMED OP b0 b1 b2 b0 b1 b2 b0 b1 b2 1 0 3MUX b0 b1 b2 @ IO 8 1 0 3MUX b0 b1 b2 e 7 6 5 2 4 1 3 0 2 1 0 Dec z 5-6-8-S E SISP-I-1 CONTROL LOGIC OP 3 @B 3 F 3 @A 3 @D OP 3 e Rb /I In /Ld In Ld/Alu W rD W rIO W rMe m TknBr Apellidos y Nombre: ……………………………………………………………. Pregunta 4. (2 punts) Responded a las preguntas respecto al siguiente fragmento de código: .data D: A: .space 3 .word 1056, -345 INI: MOVI MOVI MOVHI LD ADD ST .text R0, 2 R1, lo(A) R1, hi(A) R2, 1(R1) R3, R0, R2 0(R1), R3 .end Suponed que tanto la sección de definición de datos (.data) como subsección de las instrucciones (.text) se comienzan a ensamblar a partir de la dirección 0 de memoria (de datos y de instrucciones respectivamente). Para vuestra ayuda os damos la tabla resumen del formato y codificación de las instrucciones SISA-I. Func 000 001 010 011 100 101 110 111 AND OR XOR NOT ADD SUB SHA SHL Preguntas a) Indicad el contenido de todas las posiciones de la memoria de datos y de instrucciones, cuyo contenido es distinto de 0, después de ensamblar el código anterior y cargarlo en las memorias de datos e instrucciones. Suponed que todas las posiciones de las dos memorias contienen el valor 0 antes de cargar el programa. Responded en la siguiente tabla (Objetivo 8.1): Memoria de Datos Dirección con 4 Contenido con 4 dígitos en dígitos en Hexadecimal Hexadecimal Memoria de Instrucciones Dirección con 4 Contenido con 4 dígitos en dígitos en Hexadecimal Hexadecimal b) Suponed que el estado del computador antes de comenzar a ejecutarse el programa cargado en las memorias es el siguiente: Memoria de datos: tal como quedó después de cargarse el programa. Memoria de instrucciones: tal como quedó después de cargarse el programa. Registros generales: el contenido de todos los registros Ri es 0. Registros Especiales: PC = 0 Puertos de Entrada/Salida: no usados, no es necesario especificarlos Indica en la siguiente tabla cómo queda el estado del computador después de ejecutar cada una de las instrucciones del programa. Sólo hay que indicar el nuevo valor (en hexadecimal) de la parte del estado del computador que modifica cada instrucción. (En un programa, el estado del computador antes de iniciar la ejecución de una instrucción es el estado que dejó la instrucción que se ejecutó anteriormente) (Objetivo 8.2). Instrucción MOVI R0, 2 MOVI R1, lo(A) MOVHI R1, hi(A) LD R2, 1(R1) ADD R3, R0, R2 ST 0(R1), R3 Estado modificado, en Hexadecimal, después de ejecutar cada instrucción del programa