Formatos de instrucción de la MIPS (3 de 32 bits)

Anuncio

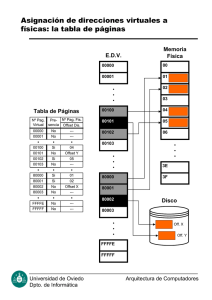

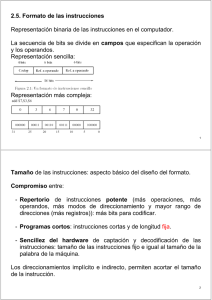

Formatos de instrucción de la MIPS (3 de 32 bits) 1 2 1. Tipo R (Registro) - opcode: código de operación primario, cuyo valor es cero. rs: especificador de registro fuente. rt: especificador de registro objetivo (fuente/destino). rd: especificador de registro destino. sa: cantidad de desplazamiento. function: campo función, especifica la operación. Utilizado para instrucciones aritméticas y lógicas: 3 (1.1) Tres operandos en registros ADD rd, rs, rt (rd ← rs + rt) SUB rd, rs, rt (rd ← rs - rt) 4 Ejemplos Modo de direccionamiento registro: 5 (1.2) Dos operandos en registros SLL rd, rt, sa (rd ← rt << sa) (Desplaza rt, sa posiciones a la izquierda, y pone el resultado en rd) Ejemplo sll $7, $3, 5 = 0 X 3 7 5 0 6 Divide rs por rt, deja el cociente en LO y el resto en HI. Ejemplo DIV $8, $9 0 8 9 X X 0x1A = 7 2. Tipo I (Inmediato) - opcode: especifica la operación. Para instrucciones: (2.1) de transferencia de datos (carga/almacenamiento): - rs: registro base. - rt: registro fuente/destino. - offset: desplazamiento. (2.2) de salto condicional: - rs y rt: para establecer la condición. - offset: desplazamiento. (2.3) instrucciones con operandos inmediatos: - rs: operando fuente. - rt: operando destino. - offset (inmediate): operando fuente. 8 (2.1) Instrucciones de carga/almacenamiento LW rt, offset(base) (rt ← memory[base+offset]) SW rt, offset(base) (memory[base+offset] ← rt) 9 Ejemplos 10 Existen instrucciones distintas para los diferentes tamaños de dato (i) Load Byte (ii) Load Half Word (iii) Load Word En todos los casos, el direccionamiento para el segundo operando es base (registro rt) + desplazamiento (offset) 11 (2.2) Instrucciones de salto condicional (bifurcación) BEQ rs, rt, offset (if (rs = rt) then branch) Operación: tgt_offset ← sign_extend(offset || 02) condition ← (GPR[rs] = GPR[rt]) if (condition) then PC ← PC + tgt_offset endif An 18-bit signed offset (the 16-bit offset field shifted left 2 bits) is added to the address of the instruction following the branch (not the branch itself), to form a PC-relative effective target address. 12 Ejemplos beq $19, $20, 6205 bne $19, $20, 6205 Estas instrucciones saltarían a la instrucción instrucciones más adelante en memoria. que está 6206 13 El modo de direccionamiento es relativo al contador de programa. En este modo, se especifica el desplazamiento (en número de instrucciones), con respecto al PC, donde está la instrucción destino del salto: dirección destino = PC + desplazamiento * 4. Las instrucciones de bifurcación pueden saltar 215-1 instrucciones hacia delante y 215 hacia atrás. En el ejemplo, si la instrucción “beq $19, $20, 6205” está en la dirección 5300, la dirección de la instrucción destino del salto sería: PC + (6205 * 4) = 5304 + 24820 = 30124 14 (2.3) Instrucciones con un operando inmediato Para operaciones con constantes ADDI rt, rs, immediate (rt ← rs + immediate) Ejemplo Modo de direccionamiento inmediato. 15 3. Tipo J (Salto) Operación: PC ← PC32..28 || instr_index || 02 Modo de direccionamiento pseudodirecto: la dirección de salto son los 26 bits menos significativos de la instrucción, desplazados 2 posiciones a la izquierda y concatenados con los 4 bits más significativos del PC. 16