Memoria virtual Memoria virtual

Anuncio

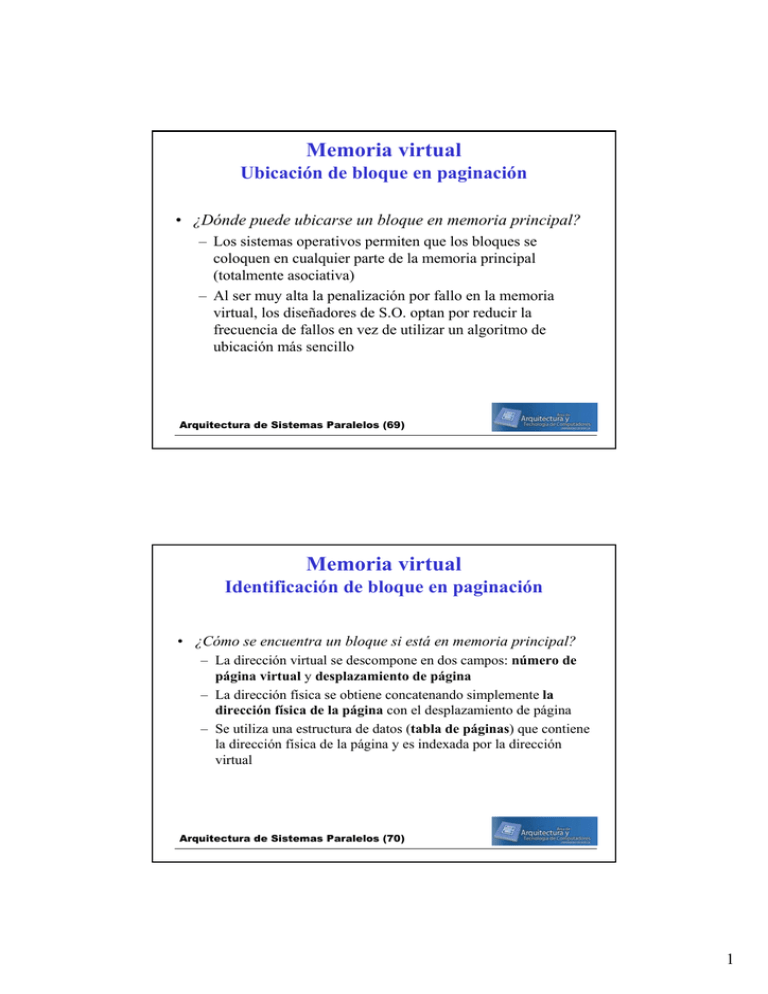

Memoria virtual Ubicación de bloque en paginación • ¿Dónde puede ubicarse un bloque en memoria principal? – Los sistemas operativos permiten que los bloques se coloquen en cualquier parte de la memoria principal (totalmente asociativa) – Al ser muy alta la penalización por fallo en la memoria virtual, los diseñadores de S.O. optan por reducir la frecuencia de fallos en vez de utilizar un algoritmo de ubicación más sencillo Arquitectura de Sistemas Paralelos (69) Memoria virtual Identificación de bloque en paginación • ¿Cómo se encuentra un bloque si está en memoria principal? – La dirección virtual se descompone en dos campos: número de página virtual y desplazamiento de página – La dirección física se obtiene concatenando simplemente la dirección física de la página con el desplazamiento de página – Se utiliza una estructura de datos (tabla de páginas) que contiene la dirección física de la página y es indexada por la dirección virtual Arquitectura de Sistemas Paralelos (70) 1 Identificación de bloque en paginación Correspondencia entre dirección virtual y física Arquitectura de Sistemas Paralelos (71) Memoria virtual Sustitución de bloque en paginación • ¿Qué bloque debería sustituirse en un fallo de memoria virtual? – Con objeto de minimizar los fallos de página, se intenta sustituir la página que menos recientemente ha sido usada (LRU) – Implementación de una política LRU: Muchas máquinas proporcionan un bit de uso o bit de referencia para cada página, que se pone a uno siempre que dicha página es accedida. El S.O. borra periódicamente los bits de uso y más tarde los registra para poder determinar qué páginas fueron accedidas durante un periodo de tiempo determinado. De esta manera, el S.O. puede seleccionar una página que se encuentre entre la menos recientemente referenciadas Arquitectura de Sistemas Paralelos (72) 2 Memoria virtual Política de escritura en paginación • ¿Qué ocurre en una escritura? – La estrategia de escritura es siempre la post-escritura (write back) debido a la gran diferencia que existe entre los tiempos de acceso en uno y otro nivel – Los sistemas de memoria virtual incluyen un bit de modificado o sucio (dirty) para que sólo los bloques que han sido alterados desde que se cargaron sean escritos en la memoria secundaria Arquitectura de Sistemas Paralelos (73) Memoria virtual Tabla de páginas (I) • Permite traducir direcciones virtuales a direcciones físicas • Está indexada por el número de página virtual y contiene la dirección física de la página. Se requiere un bit de válido para indicar que la entrada contiene un página física válida (se encuentra en memoria principal y no se produce fallo de página) • El tamaño de la tabla de páginas es inversamente proporcional al tamaño de página • Las tablas de páginas son habitualmente tan grandes que se almacenan en memoria principal y, con frecuencia, paginadas ellas mismas: se requiere un acceso a memoria para obtener la dirección física y otro para obtener el dato • Bits de control: válido, uso, sucio, permiso lectura y permiso escritura • Optimización: Jerarquía de tablas de página, técnicas hashing (tablas de páginas invertidas) y Buffer de Traducción Anticipada (TLB) Arquitectura de Sistemas Paralelos (74) 3 Memoria virtual Tabla de páginas (II) Ejemplo: Dirección virtual de 28 bits, páginas de 4Kb y 4 bytes/entrada (256Mb/4Kb)*4 = 256Kb Arquitectura de Sistemas Paralelos (75) Memoria virtual Buffer de traducción anticipada o TLB (I) • De nuevo el principio de localidad: Si las referencias tienen localidad entonces la traducción de direcciones también debe tener localidad • El buffer de traducción anticipada (translation-lookaside buffer) o TLB es una cache, habitualmente totalmente asociativa o asociativa por conjuntos, cuyas entradas contienen: en la parte de la etiqueta, el número de página virtual (o parte) y en la parte del dato, el número de página física y los bits de control • Un tamaño de página mayor hace que más memoria pueda estar mapeada con una entrada, por lo que se reduce el numero de fallos en la TLB • Hay TLBs unificadas y separadas (datos e instrucciones) Tamaño de bloque 4-8 bytes (una entrada de tabla de página) Tiempo de acierto 1 ciclo de reloj Penalización de fallos 10-30 ciclos de reloj Frecuencia de fallos 0.1%-0.2% Tamaño TLB 32-8192 Valores típicos de parámetros Arquitectura de Sistemas Paralelos (76) 4 Memoria virtual Buffer de traducción anticipada o TLB (II) Arquitectura de Sistemas Paralelos (77) Buffer de traducción anticipada o TLB (III) Ejemplo: TLB del VAX-11/780 Tamaño de página de 512bytes Entrada de TP de 4bytes TLB de 512bytes asociativa por conjuntos de 2 vías Pasos: 1: Envío del índice de la dirección virtual 2: Comprobación de válido y tipo de acceso a memoria 3: Comparación de etiquetas 4: Envío de la dirección física a través del multiplexor 5: Combinación del número y desplazamiento de página Arquitectura de Sistemas Paralelos (78) 5 Buffer de traducción anticipada o TLB (IV) TLB y cache • Cuando se combinan caches y memoria virtual, la dirección virtual debe ser traducida a una dirección física mediante la TLB antes de que pueda acceder a la cache (elevado tiempo de acierto) • Una forma de reducir el tiempo de acierto es: – acceder a la cache únicamente con el desplazamiento de página (no necesita ser traducido) y mientras se están leyendo las etiquetas de dirección de la cache, el número de página virtual es enviado a la TLB para ser traducido – como la TLB es habitualmente más pequeña y rápida que la memoria de etiquetas de la cache, la lectura de la TLB puede hacerse de forma simultánea a la lectura de la memoria de etiquetas sin ralentizar los tiempos de acierto de la cache – después la comparación de direcciones se realiza entre la dirección física de la TLB y la etiqueta de la cache • Inconveniente: una cache de correspondencia directa no puede ser mayor que una página • Otra alternativa es utilizar caches virtuales (transparencia 59) Arquitectura de Sistemas Paralelos (79) 6