Retos en el diseño de los procesadores

Anuncio

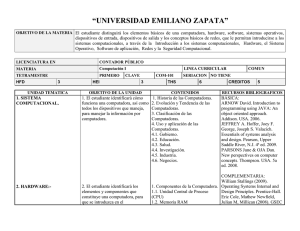

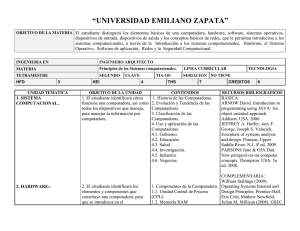

Parallel Computing Seminar Retos en el diseño de los procesadores Juan Carlos Moure Parallel Computing Seminar – Canarias Oct 05 DiseñoProc 1 Computer Architecture and Operating Systems El Coste del Alto Rendimiento Rango de Procesadores coste ( € ) consumo ( wats ) El rendimiento de un procesador no es lineal con el coste de fabricación y con el coste de utilización (consumo energético, refrigeración, …) operaciones / segundo Parallel Computing Seminar – Canarias Oct 05 DiseñoProc 2 Computer Architecture and Operating Systems Alto Rendimiento con múltiples chips Smart Dust : 10.000s /10,000.000s procesadores tamaño, coste y consumo muy pequeño conexión inalámbrica, heterogénea, … batería incorporada (usar y tirar) Rango de Procesadores coste ( € ) moderada o masivamente paralelizables consumo ( wats ) Premisa: Aplicaciones operaciones / segundo Clusters: (Blue Gene) 100s / 100.000s procesadores buena relación: rendimiento / coste rendimiento / consumo conexión homogénea, banda muy ancha. Computer Parallel Computing Seminar – Canarias Oct 05 DiseñoProc 3 Architecture and Operating Systems Alto Rendimiento con múltiples chips Reto: Caracterizar propiedades relevantes de un procesador para formar un sistema paralelo: (Diferencias respecto a un procesador convencional) 1. ¿Integrar comunicaciones? 2. ¿Menos soporte al sistema operativo? 3. ¿Reconfigurabilidad? … Parallel Computing Seminar – Canarias Oct 05 DiseñoProc 4 Computer Architecture and Operating Systems Alto Rendimiento con un único chip Rango de Procesadores coste ( € ) una única aplicación, no paralelizada de forma explícita consumo ( wats ) Premisa: acelerar operaciones / segundo Reto: Aumentar prestaciones de forma más eficiente (consumo / coste) Parallel Computing Seminar – Canarias Oct 05 DiseñoProc 5 Computer Architecture and Operating Systems Alto Rendimiento con un único chip paralelismo + + frecuencia de reloj Supersegmentación InstructionLevel Parallelism Multithreading + consumo / rendimiento + coste /rendimiento Reto: Obtener paralelismo a diferentes niveles: instrucción / lazos Parallel Computing Seminar – Canarias Oct 05 DiseñoProc 6 / threads Computer Architecture and Operating Systems Alto Rendimiento con un único chip el H/W busca el paralelismo dinámicamente Ejecución Superescalar y Especulación + consumo / rendimiento + coste /rendimiento Parallel Computing Seminar – Canarias Oct 05 el S/W busca el paralelismo estáticamente (compilador y programador) EPIC (VLIW) Multithreading Reto: H/W y S/W colaboran de forma eficiente en buscar paralelismo DiseñoProc 7 Computer Architecture and Operating Systems Alto Rendimiento con un único chip el diseñador adapta el H/W a la aplicación el H/W se adapta dinámicamente a la aplicación Configuración a Medida Problema: alto coste de diseño Reconfiguración Problema: coste reconfiguración (estático/dinámico) Tiempo de aprendizaje Reto: S/W colabora con H/W en la adaptación (ejemplo: code morphing) Parallel Computing Seminar – Canarias Oct 05 DiseñoProc 8 Computer Architecture and Operating Systems Predicción de Flujo de Control Identificar las instrucciones que se han de proporcionar a las siguientes etapas del procesador segmentado Predictor de Flujo Cache Instrucciones 1. Prever la ocurrencia de instrucciones de salto y predecir su resultado 2. Proporcionar las direcciones de las instrucciones Parallel Computing Seminar – Canarias Oct 05 DiseñoProc 9 Computer Architecture and Operating Systems Predicción de Flujo de Control Reto: Gran Ancho de Banda con uso eficiente de recursos Propuestas: 1. Usar traza como elemento básico de predicción: aprender es más complejo, pero cada predicción es más eficiente: más rendimiento con “coste” similar 2. Predecir qué datos se usarán en la predicción acceder sólo a datos útiles: más rápido, menos consumo traza nº 1 traza nº 2 Punto de Entrada Parallel Computing Seminar – Canarias Oct 05 traza nº 3 DiseñoProc 10 Computer Architecture and Operating Systems Idea: Predecir datos útiles addri Acceso sólo a información probablemente útil Selección final de información útil addr i+1 TCT idxi Asumimos predicción correcta Datos críticos Si la predicción fue incorrecta, hay que acceder a TODA la información idxi+1 Frecuente + no crítico TPred TPred A) sin predicción check Acceso en paralelo a TODA la información (no sé cuál será útil) Uso Poco Frecuente B) con predicción tiempo total consumo total Penalización por fallo de predicción Parallel Computing Seminar – Canarias Oct 05 DiseñoProc 11 Computer Architecture and Operating Systems