Estructura de Computadores 2 [08/09] Entrada

Anuncio

![Estructura de Computadores 2 [08/09] Entrada](http://s2.studylib.es/store/data/005965071_1-6615eed32543f3a6a0449e36ee6d33b8-768x994.png)

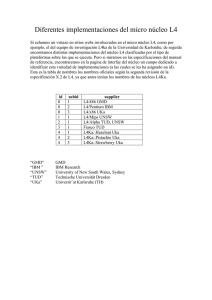

Estructura de Computadores 2 [08/09]

Entrada/Salida en procesadores MIPS

GAC: Grupo de Arquitectura de Computadores

Dpt. Electrónica e Sistemas. Universidade da Coruña.

Bibliografı́a

Computer Organization and Design: The hardware/software interface (3rd ed.), David A.

Patterson and John L. Hennessy. Morgan Kaufmann Publishers, Inc.

(También disponible en castellano: Estructura y diseño de computadores: interficie circuiterı́a/programación)

1.

Introducción

Filosofı́a RISC (Reduced Instruction Set Computer)

• Instrucciones de pocas etapas (buscando además longitud fija de instrucciones)

• instrucciones de carga/almacenamiento (load/store)

• reducido número de métodos de direccionamiento

• juego de instrucciones pequeño

Ejemplos RISC: MIPS, Sun SPARC, HP PA-RISC, IBM PowerPC, Alpha, ARM. . .

Objetivos de diseño: velocidad, coste (diseño, fabricación y testeo), tamaño, consumo

eléctrico, fiabilidad, versatilidad (sistemas empotrados)

Principios básicos:

• simplicidad favorece regularidad

• más pequeño ⇒ más rápido

• hacer el caso más frecuente lo más rápido posible

2.

MIPS: Arquitectura básica y ensamblador

E/S asignada en memoria (MMIO)

Dos modos de funcionamiento: kernel y usuario

La mitad superior del espacio de direcciones sólo accesible en modo kernel : direcciones a

partir de 0x8000 0000.

Esta región incluye:

• Código para el manejo de excepciones

• Datos solo accesibles al SO

• Direcciones de E/S asignadas en memoria: a partir de 0xf f f f 0000

Organización de memoria

Organización de un stack frame

Registros del MIPS y convención sobre su uso

Operandos de instrucciones MIPS

Category

Arithmetic

add

MIPS assembly language

Example

Meaning

add $s1, $s2, $s3

$s1 = $s2 + $s3

Three operands; data in registers

subtract

sub $s1, $s2, $s3

Three operands; data in registers

Instruction

addi $s1, $s2, 100

lw $s1, 100($s2)

sw $s1, 100($s2)

store w ord

lb $s1, 100($s2)

load byte

sb $s1, 100($s2)

store byte

load upper immediate lui $s1, 100

add immediate

load w ord

Data

transfer

$s1 = $s2 + 100

$s1 = Memory[$s2 + 100]

Memory[$s2 + 100] = $s1

$s1 = Memory[$s2 + 100]

Memory[$s2 + 100] = $s1

$s1 = 100 * 2 16

Used to add constants

Word from memory to register

Word from register to memory

Byte f rom memory to register

Byte f rom register to memory

Loads constant in upper 16 bits

branch on equal

beq

$s1, $s2, 25

if ($s1 == $s2) go to

PC + 4 + 100

Equal test; PC-relative branch

branch on not equal

bne

$s1, $s2, 25

if ($s1 != $s2) go to

PC + 4 + 100

Not equal test; PC-relative

slt

$s1, $s2, $s3

if ($s2 < $s3) $s1 = 1;

else $s1 = 0

Compare less than; for beq, bne

Conditional

set on less than

branch

Unconditional jump

$s1 = $s2 - $s3

Comments

set less than

immediate

slti

jump

j

jr

jal

jump register

jump and link

$s1, $s2, 100 if ($s2 < 100) $s1 = 1;

Compare less than constant

else $s1 = 0

2500

$ra

2500

Formato de instrucciones del MIPS

go to 10000

Jump to target address

go to $ra

For sw itch, procedure return

$ra = PC + 4; go to 10000 For procedure call

Modos de direccionamiento

Qué se guarda y qué no en una subrutina

leaf_example:

addi $sp, $sp, -4

sw $s0, 0($sp)

int leaf_example (int g, int h, int i, int j) {

int f;

f = (g + h) - (i + j);

return f;

add $t0, $a0, $a1

add $t1, $a2, $a3

sub $s0, $t0, $t1

add $v0, $s0, $zero

}

lw $s0, 0($sp)

addi $sp, $sp, 4

jr $ra

#adjust stack

#save reg $s0

#g+h in $t0

#i+j in $t1

3.

E/S en MIPS

E/S asignada en memoria

3.1.

E/S con interrupciones

Eventos o situaciones excepcionales en flujo de ejecución del MIPS:

1. Petición de dispositivo de E/S

Origen: Externo. Terminologı́a MIPS: Interrupción

2. Llamada al sistema desde espacio usuario

Origen: Interno. Terminologı́a. MIPS: Excepción

3. Desbordamiento aritmético (overflow )

Origen: Interno. Terminologı́a MIPS: Excepción

4. Uso de una instrucción no definida

Origen: Interno. Terminologı́a MIPS: Excepción

5. Problema hardware

Origen: Interno o Externo. Terminologı́a MIPS: Excepción o Interrupción

Para el manejo de excepciones e interrupciones MIPS utiliza el coprocesador 0.

Identificación del motivo de excepción mediante un registro de estado (Registro de causa

o Cause register ) del coprocesador 0 (no usa interrupciones vectorizadas).

Otro registro de estado (Registro de estado o Status register ) permite habilitar/deshabilitar

interrupciones.

Otro registro guarda la dirección de la instrucción interrumpida, es decir, del contador de

programa: EPC register (Exception Program Counter ).

Los registros del coprocesador 0 son accesibles por medio de las instrucciones mfc0 (move

from coprocessor 0 ) y mtc0 (move to coprocessor 0 ):

mfc0

mtc0

$k0, $13

$0, $12

# Reg. $k0 de CPU cargado con contenido de reg causa

# Reg. zero de CPU almacenado en reg estado

# (se borra a cero)

La instrucción rfe (return from exception) habilita de nuevo las interrupciones (bit Interrupt Enable en registro de estado) antes de devolver el control tras la ejecución de una

rutina de servicio.

Un salto incondicional a la dirección de la instrucción siguiente a la que habı́a sido interrumpida devuelve el control tras haber atendido la excepción.

Algunos registros del coprocesador 0 del MIPS

Principales bits del registro de estado del C0 del MIPS

Principales bits del registro de causa del C0 del MIPS

Códigos de causas de excepción

La arquitectura MIPS fija una dirección de memoria como dirección de comienzo del

manejador de excepciones: 0x8000 0080.

Manejo de una excepción en MIPS