DMA y Discos - Departamento de Computación

Anuncio

Entrada-Salida

Entrada-Salida

DMA y Discos

Organización del Computador I

David Alejandro González Márquez

Departamento de Computación

Facultad de Ciencias Exactas y Naturales

Universidad de Buenos Aires

02.03.2011

Entrada-Salida

Entrada-Salida

¿Qué es DMA (Direct memory access )?

Es un dispositivo o caracterı́stica de un dispositivo,

por la que se le permite acceder a la memoria principal

independientemente del procesador central

En general cuenta con registros que indican qué direcciones

deben ser escritas o leı́das desde la memoria principal al

dispositivo o viceversa

Ver: DMA controller 8257

http://www.8085projects.info/

PROGRAMMABLE-DMA-CONTROLLER-INTEL8257.html

Entrada-Salida

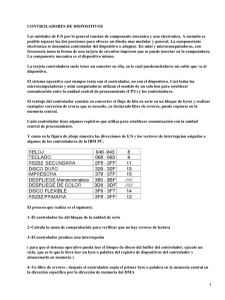

Discos

Pista/

Cilindro

Los discos se componen por

platos divididos en pistas y

sectores.

Dos consideraciones

importantes,

Sector

La interfaz del disco,

IDE, SCSI, SATA, SAS, . . .

Cabezas

El sistema de archivos,

FAT, ext2 . . . ext4, NTFS,

HFS, ISO 9660, . . .

8 cabezas,

4 platos

Hard Drive Size Limitations and Barriers

Ver: http://www.dewassoc.com/kbase/hard drives/hard drive size barriers.htm

Entrada-Salida

Entrada-Salida

Ejercicios

Ejercicio 1

Se posee el siguiente sistema:

Memoria

Disk 1

Disk 2

Controladora

de discos

Disk 3

El controlador puede acceder a los discos; leer o escribir sus

sectores. Para esto posee un buffer interno donde se almacena

temporariamente esta información. La CPU puede solicitar al

controlador que lea o escriba a la memoria un sector de un disco

mediante un protocolo de DMA.

Entrada-Salida

Ejercicios

Ejercicio 1

Algunas primitivas del controlador de disco son:

LeerDeDisco( Sector S, Disco D, Buffer B )

Lee el sector S del disco número D y lo almacena en el buffer

interno número B.

LeerDeMemoria( Dirección D, Buffer B )

Lee desde la dirección de memoria D un sector completo y lo

almacena en el buffer interno número B.

a. Identificar todos los registros que requiera el controlador

indicando su uso.

b. Identificar qué primitivas faltan definir para la controladora.

c. Escribir el seudocódigo de la controladora de discos.

d. Programar el controlador para copiar el sector número 387 del

disco 2, a la dirección de memoria 0x3041.

Entrada-Salida

Ejercicios

Ejercicio 1: Solución

a. Identificar todos los registros que requiera el controlador

indicando su uso.

DISCO: Selecciona el disco con el cual se desea interactuar.

SECTOR: Indica que sector del disco que se desea leer o

escribir.

DIRECCION: Indica la dirección de memoria para leer o

escribir.

ESTADO: Proporciona el estado del dispositivo

0x86 : Ocupado Leyendo

0x82 : Ocupado Escribiendo

0x00 : Libre

Entrada-Salida

Ejercicios

Ejercicio 1: Solución

b. Identificar qué primitivas faltan definir para la controladora.

Faltan definir todas las primitivas de escritura en disco y en

memoria

EscribirEnDisco( Sector S, Disco D, Buffer B )

Escribir el buffer interno número B en el sector S del disco

número D.

EscribirEnMemoria( Dirección D, Buffer B )

Escribir el buffer interno número B desde la dirección de

memoria D.

Entrada-Salida

Ejercicios

Ejercicio 1: Solución

c. Escribir el seudocódigo de la controladora de discos.

while(true)

if( ESTADO == 0x86 )

LeerDeDisco(SECTOR,DISCO,BUFFER_DMA_LECTURA)

EscribirEnMemoria(DIRECCCION,BUFFER_DMA_LECTURA)

ESTADO <- 0x00

if( ESTADO == 0x82 )

LeerDeMemoria(DIRECCCION,BUFFER_DMA_ESCRITURA)

EscribirEnDisco(SECTOR,DISCO,BUFFER_DMA_ESCRITURA)

ESTADO <- 0x00

Donde BUFFER DMA LECTURA y BUFFER DMA ESCRITURA son

buffers de la controladora reservados para el DMA.

Entrada-Salida

Ejercicios

Ejercicio 1: Solución

d. Programar el controlador para copiar el sector número 387 del

disco 2, a la dirección de memoria 0x3041.

esperar:

cmp [ESTADO], 0

jz esperar

mov [DISCO], 2

mov [SECTOR], 387

mov [DIRECCION], 0x3041

mov [ESTADO], 0x86

Entrada-Salida

Ejercicios

Entrada-Salida

Ejercicios

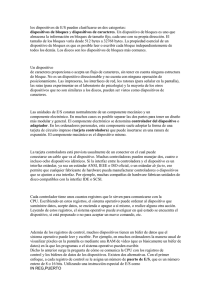

Ejercicio 2

Interrupción

Capturadora

de Video

CPU

Memoria

Puente

Controlador

de DMA

M/IO

RW

RD

Request

Ready

Bus de Direcciones

Bus de Datos

A continuación se describe el protocolo entre el controlador de

DMA y un dispositivo de E/S para realizar transferencias de datos

usando el I/O Bus.

Entrada-Salida

Ejercicios

Ejercicio 2

1. El controlador DMA pone en el bus de direcciones el identificador del

dispositivo con el que desea iniciar la comunicación y levanta la señal

de Request, de RD o WR, según corresponda y baja la lı́nea de M/IO.

2. El controlador del dispositivo detecta la señal de Request y compara

su propio identificador con el contenido del bus de direcciones.

3. Si coincide el identificador y el dispositivo se encuentra listo, el

controlador del dispositivo levanta la señal de Ready.

4. El controlador DMA detecta la señal de Ready. En el caso de tratarse

de una escritura, el controlador DMA pone el dato a escribir junto con

su posición de memoria en los buses correspondientes. Por otro lado,

en el caso de una lectura, el controlador de DMA pone la dirección del

dato deseado.

5. El controlador DMA baja la señal de Request.

6. · · ·

Entrada-Salida

Ejercicios

Ejercicio 2

5. · · ·

6. De tratarse de una escritura, el controlador del dispositivo ordena

grabar el dato, o en el caso de una lectura pone el dato en el bus.

Luego, baja la señal de Ready.

7. Si se trata de una lectura el DMAC lee el dato del bus de datos.

8. En ambos casos, lectura y escritura, el DMAC retira las lı́neas y baja

la señal de RD o WR según corresponda.

9. Si es una lectura, cuando el DMAC baja la señal de RD la controladora

del dispositivo quita el dato del bus de datos.

El protocolo para interactuar con la memoria es equivalente. Cambia el

valor de la lı́nea M/IO y no se coloca en el bus el identificador del

dispositivo.

Entrada-Salida

Ejercicios

Ejercicio 2

Primitivas de control del bus:

requestBus() : Solicita el bus para realizar cualquier transferencia.

releaseBus() : Libera el bus una vez que se termino de utilizar.

Además cada lı́nea de control posee una primitiva get seguida del

nombre y otra de nombre set. Que permiten leer o escribir cada

una de las lı́neas respectivamente.

setRequest(x)

getRequest()

setReady(x)

getReady()

setRead(x)

getRead()

setWrite(x)

getWrite()

setMemoryIO(x)

getMemoryIO()

Para las lı́neas de datos y direcciones se poseen primitivas que

permiten leer y escribir las lı́neas en su conjunto.

setData(x)

getData()

setAddress(x)

getAddress()

Entrada-Salida

Ejercicios

Ejercicio 2

La Placa Capturadora de Video tienen su espacio de direcciones mapeado

a memoria en las direcciones FE00 a FF00. Por simplicidad suponemos

que es una pantalla de video. El identificador de este dispositivo es

0x005F. A su vez, el controlador de DMA posee los siguientes registros

también mapeados a memoria en las direcciones indicadas:

DEVICE (0xFFA0): identificador del dispositivo.

DEVICE ADDRESS (0xFFA1): dirección de memoria (en el espacio de

direccionamiento del dispositivo) que se desea leer/escribir.

MEM ADDRESS (0xFFA2): dirección de memoria (en el espacio de

direccionamiento de la memoria principal) que se desea leer/escribir.

SIZE (0xFFA3): cantidad de datos a transferir.

STATUS (0xFFA4):

si bit 0 contiene 1 indica que ya se han cargado todos los datos

necesarios, y se puede iniciar la transmisión.

el bit 1 contiene un 1 en caso de escritura, y un 0 en caso contrario.

Entrada-Salida

Ejercicios

Ejercicio 2

El comportamiento del controlador de DMA es el siguiente, cuando

el bit 0 de STATUS contiene un 1 significa que se puede comenzar

la transferencia.

Si el bit 1 de STATUS es un 1 entonces será de IO a Memoria, si es

0 sera de Memoria a IO.

Serán transferidos la cantidad de palabras que indique SIZE, de la

dirección indicada por MEM ADDRESS a DEVICE ADDRESS o

viceversa.

Entrada-Salida

Ejercicios

Ejercicio 2

1

Escribir el seudo-código que realiza el controlador de DMA

2

Suponga que existe un proceso que muestra en la pantalla los

cuadros de video capturados por la placa. Este proceso posee

una rutina que escribe en la memoria principal el cuadro

capturado. La placa capturadora genera una interrupción,

cada vez que se captura un cuadro. Realizar el seudo-código

de la rutina que atiende la interrupción de la placa. (el rango

de memoria AB00 a AC00 esta reservado para guardar la

pantalla capturada en memoria principal)

3

Realizar el punto anterior utilizando el controlador de DMA.

Entrada-Salida

Ejercicios

Ejercicio 2: Solución - 1

while(true)

if( STATUS AND [0...01] =/= 0 )

if( STATUS AND [0...010] =/= 0 )

// IO a Memoria

while( SIZE > 0 )

tempDato <- LeerDatoDeDispositivo()

EscribirDatoEnMemoria(tempDato)

MEM_ADDRESS <- MEM_ADDRESS + 1

DEVICE_ADDRESS <- DEVICE_ADDRESS + 1

SIZE <- SIZE - 1

STATUS <- STATUS AND [1...10]

else

// Memoria a IO

while( SIZE > 0 ) {

tempDato <- LeerDatoDeMemoria()

EscribirDatoEnDispositivo(tempDato)

MEM_ADDRESS <- MEM_ADDRESS + 1

DEVICE_ADDRESS <- DEVICE_ADDRESS + 1

SIZE <- SIZE - 1

STATUS <- STATUS AND [1...10]

Entrada-Salida

Ejercicios

Ejercicio 2: Solución - 1

Lectura de Dispositivo

Lectura de Memoria

requestBus()

setMemoryIO(0)

setRead(1)

setWrite(0)

setAddress(DEVICE)

setRequest(1)

wait( getReady() =/= 0 )

setAddress(DEVICE ADDRESS)

setRequest(0)

wait( getReady() =/= 1 )

tempDato <- getData()

setRead(0)

releaseBus()

requestBus()

setMemoryIO(1)

setRead(1)

setWrite(0)

setRequest(1)

wait( getReady() =/= 0 )

setAddress(MEM ADDRESS)

setRequest(0)

wait( getReady() =/= 1 )

tempDato <- getData()

setRead(0)

releaseBus()

Entrada-Salida

Ejercicios

Ejercicio 2: Solución - 1

Escritura en Dispositivo

Escritura en Memoria

requestBus()

setMemoryIO(0)

setRead(0)

setWrite(1)

setAddress(DEVICE)

setRequest(1)

wait( getReady() =/= 0 )

setAddress(DEVICE ADDRESS)

setData(tempDato)

setRequest(0)

wait( getReady() =/= 1 )

setWrite(0)

releaseBus()

requestBus()

setMemoryIO(1)

setRead(0)

setWrite(1)

setRequest(1)

wait( getReady() =/= 0 )

setAddress(MEM ADDRESS)

setData(tempDato)

setRequest(0)

wait( getReady() =/= 1 )

setWrite(0)

releaseBus()

Entrada-Salida

Ejercicios

Ejercicio 2: Solución - 2

rutina:

ciclo:

fin:

.....

.....

MOV R1, 0xAB00

MOV R2, 0xFE00

MOV R0, 0x0100

MOV [R1], [R2]

SUB R0, 1

ADD R1, 1

ADD R2, 1

CMP R0, 0

JE fin

JMP ciclo

.....

.....

RETI

Entrada-Salida

Ejercicios

Ejercicio 2: Solución - 3

rutina:

.....

.....

MOV [DEVICE], 0x005F

MOV [DEVICE_ADDRESS], 0x0000

MOV [MEM_ADDRESS], 0xAB00

MOV [SIZE], 0x0100

OR [STATUS], 0x8000

.....

.....

RETI

Entrada-Salida

Ejercicios

Entrada-Salida

Ejercicios

Ejercicio 3

A continuación se presentan algunos parámetros caracterı́sticos de

un disco rı́gido.

Cantidad de Bytes por Sector : |Sectorbytes | Bytes

Cantidad de Platos o Cantidad de Cabezas : |Cabezas|

Cantidad de Pistas por Plato o Cantidad de Cilindros : |Cilindros|

Cantidad de Sectores por Pista : |Sectorespista |

Tiempo entre Pistas adyacentes : |Tadyasentes | Seg

Tiempo promedio entre Pistas : |Tpromedio | Seg

Latencia : |Tlatencia | Seg

Capacidad del Buffer : |Buffer | Mb

Velocidad de Rotación : |Discorotacion | RPM

Velocidad de Transferencia de la Interfaz : |Interfazvelocidad | Mb/Seg

Entrada-Salida

Ejercicios

Ejercicio 3

Calcular los siguientes valores caracterı́sticos a partir de los

parámetros presentados.

1

Cantidad de Sectores totales.

2

Capacidad máxima en Mbytes.

3

Tiempo de lectura de un sector.

4

Tiempo de transferencia de un sector.

5

Tiempo de transferencia de n sectores consecutivos sobre una

misma pista.

Entrada-Salida

Ejercicios

Ejercicio 3: Solución

1

|Sectorestotales | = |Cabezas| ∗ |Cilindros| ∗ |Sectorespista |

2

|Capacidadtotal | = |Sectorestotales | ∗ |Sectorbytes |

3

|TLectura.Sector | = 60/(|Discorotacion | ∗ |Sectorespista |)

4

|TTransferencia.Sector | =

|TLectura.Sector | + |Sectorbytes |/(220 ∗ |Interfazvelocidad |)

5

|TTransferencia.Sectores.Unica.Pista (n)| =

n ∗ |TTransferencia.Sector | + (n − 1)|Tlatencia |

Entrada-Salida

Ejercicios

¿Preguntas?

Entrada-Salida

Ejercicios

¿Preguntas?