Registro de desplazamiento con entrada paralelo y salida paralelo.

Anuncio

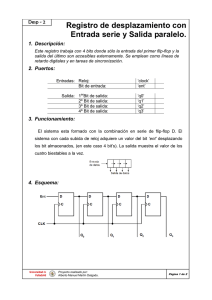

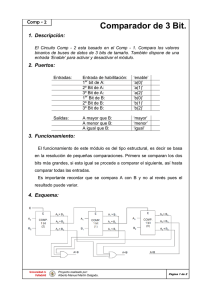

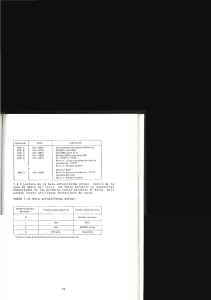

Desp - 4 Registro de desplazamiento con entrada paralelo y salida paralelo. 1. Descripción: Este componente dispone de los mismos bits de entrada y salida, que en este caso son 4, cuando se produce una subida del flanco de reloj los bits de entrada se envían a la salida. 2. Puertos: Entradas: Reloj: 1er Bit de entrada: 2º Bit de entrada: 3º Bit de entrada: 4º Bit de entrada: Salida: 1er Bit de salida: 2º Bit de salida: 3º Bit de salida: 4º Bit de salida: ‘clock’ ‘ent(0)’ ‘ent(0)’ ‘ent(0)’ ‘ent(0)’ ‘q(0)’ ‘q(1)’ ‘q(2)’ ‘q(3)’ 3. Funcionamiento: Este componente es el más parecido a una memoria de 4 bits. La salida almacena los 4 bits del último franco de subida. Cuando este se vuelve a producir, los bits de entrada bajan y se envían por la correspondiente salida. Para poder utilizar este componente como una memoria RAM se deberá de considerar que el reloj es el bit R/W. 4. Esquema: Universidad de Valladolid Proyecto realizado por: Alberto Manuel Martín Delgado. Página 1 de 2 5. Ejemplo: Para este ejemplo se introducido dos valores: ‘0110’ correspondiente al 610 y ‘1001’ que corresponde al 910. La señal de salida se mantiene hasta el siguiente flanco de subida. 6. Cuestiones: • ¿Qué entrada habría que introducir en ‘ent(3)’ para que ‘q(3)’ muestre un reloj de periodo el doble que ‘clock’? • ¿Si se anula la entrada de reloj la salida cambia? • ¿Cuantos registros hace falta para aumentar un bit el bus de entrada y el de salida? Universidad de Valladolid Proyecto realizado por: Alberto Manuel Martín Delgado. Página 2 de 2