soluciones - Facultad de Ingeniería

Anuncio

Facultad de Ingeniería – UDELAR

Int. a los microprocesadores – JULIO 2011

SOLUCIONES

pag. 1/4

SOLUCIÓN PROBLEMA 1

a) Hardware

-- Memorias:

R O M

A[14..0]

Add[]

R A M

D[7..0]

Data[]

A[14..0]

O R 2

/ M R E Q

C S

O E

inst16

A 1 5

D[7..0]

C S

O E

W E

/ R D

N O T

inst15

/ W R

inst32

/ R D

Data[]

O R 2

/ M R E Q

A 1 5

Add[]

-- Puertos, decodificación e Interrupciones.

A[7]

NOT

A 0

A 1

inst17

A[6]

deco_1de4

inst14

NOT

OR4

Y

Y

Y

Y

A 1

A 0

inst19

0

1

2

3

IDSP_req_umbral

IDSP_dat_umbral_1

IDSP_dat_umbral_2

IDSP_adc

A[7]

A[6]

NOT

A 0

A 1

OR4

deco_1de4

Y

Y

Y

Y

A 1

A 0

inst28

0

1

2

3

ODSP_ack_umbral

ODSP_bandera

ODSP_amplitud

G

/IORQ

/ W R

DECO

inst18

inst13

inst27

G

/IORQ

/RD

NOT

inst21

inst1

DECO

inst26

IDSP_dat_umbral_1

N O T

inst8

dat_umbral_1

D[6..0]

TRI

IDSP_adc

inst7

N O T

inst24

A/D

senal

IDSP_dat_umbral_2

N O T

Vin

D[6..0]

conv[6..0],conv[7..0]

TRI

D[7..0]

inst20

conv[7]

inst10

G N D

dat_umbral_2

D[6..0]

TRI

inst9

D F F

T I C

D

PRN

N O T

Q

inst5

/INT

V C C

inst

O R 2

A N D 2

/ I O R Q

/reset

PRN

T R I

Q

CLRN

inst3

ODSP_ack_umbral AND2

inst31

D F F

D

req_umbral

CLRN

inst12

/ M 1

N O T

IDSP_req_umbral

V C C

/reset

inst30

inst29

D F F

D 0

D

PRN

ODSP_bandera

CLRN

inst6

/reset

bandera

D[7..0]

Q

D F F

D

ODSP_amplitud

PRN

CLRN

inst11

amplitud

Q

inst4

D 0

Facultad de Ingeniería – UDELAR

Int. a los microprocesadores – JULIO 2011

SOLUCIONES

b) Inicialización y reserva mem.

adc

EQU 0xC3

datumb_2 EQU 0xC2

datumb_1 EQU 0xC1

req_umb EQU 0xC0

ack_umb EQU 0xC0

bandera EQU 0xC1

amplitud EQU 0xC2

umb1_ini EQU 20

umb2_ini EQU 5

.Org 0x8000

umbral_1 DB

umbral_2 DB

Dat_ant DB

Estado

DB

Máximo

DB

pag. 2/4

;

bandera = 0x00

;

Estado = reposo (0x00)

;

amplitud = Máximo

;

}else{

;

if (Dato_leído > Máximo){

;

Máximo = Dato_leído

;

}

;

}

; }

; Dat_ ant = Dato_leído

; restauro registros y retorno

; Nota: Tener en cuenta que tanto los datos

; leídos del ADC como los umbrales siempre

; son positivos y menores que 128.

.Org 0x38

PUSH AF

.Org 0x0000

PUSH BC

LD SP, 0x0000

PUSH HL

LD A, umb1_ini

LD A, (Dat_ant)

LD (umbral_1), A

LD B, A

LD A, umb2_ini

IN A, (adc)

LD (umbral_2), A

LD C, A; Guardo en C dato leído de ADC

LD A, 0x00

LD A, (Estado)

LD (Dat_ant), A

AND 0xFF

LD (Estado), A

JP NZ, Pico

LD (Máximo), A

LD HL, umbral_1

OUT (amplitud), A

LD A, C

IM 1

SUB B

; dato_leido - dat_ant

EI

CP (HL)

; menos umbral1

JP Loop

JP M, Fin

; Si positivo → comienzo de pico

c) Loop programa principal

; si no reposo

; for (true) {

LD A, 0xFF

; Leo req_umbral

OUT (bandera), A

; if (req_umbral == 1){

LD (Estado),A

;

actualizo umbral_1

LD A, C

;

actualizo umbral_2

LD (Máximo), A

;

doy pulso ack_umbral

JP Fin

;

}

Pico: LD A, C

; }

LD HL, umbral_2

.Org 0x100

CP (HL)

; dejo lugar para la rutina de

JP P, Máx

; atención a la interrupción

; Si es positivo no se cumple

Loop: IN A, (req_umb)

; cond. de salida de pico

BIT 0, A

LD A, B

; dat_ant

JP Z, Loop

CP (HL)

IN A, (datumb_1)

JP P, Máx

AND 0x7F

; Se cumple cond. de salida de pico

LD (umbral_1), A

LD A, 0x00

IN A, (datumb_2)

OUT (bandera), A

AND 0x7f_

LD (Estado), A

LD (umbral_2), A

LD A, (Máximo)

OUT (ack_umb), A

OUT (amplitud), A

JP Loop

JP Fin

Máx:

LD A, (Máximo); comparo maximo

d) Rutina atención interrupciones

CP C

; con C (dato_leido)

; preservo registros

JP P, Fin

; Dato_leido = puerto_adc

LD A, C

; maximo = Dato_leido

; if (Estado == reposo){

LD (Máximo), A

;

if (Dato_leido – Dat_ant – umbral1 > 0){ Fin:

LD A, C

;

bandera = 0xFF

LD (Dat_ant), A

;

Estado = pico (0xFF)

POP HL

;

Máximo = Dato_leído

POP BC

;

}

POP AF

; } else{

EI

;

if ( (Dato_leido < umbral2) and

RET

;

(Dat_ant < umbral2)){

Facultad de Ingeniería – UDELAR

Int. a los microprocesadores – JULIO 2011

SOLUCIONES

pag. 3/4

SOLUCIÓN PROBLEMA 2

a) Hardware.

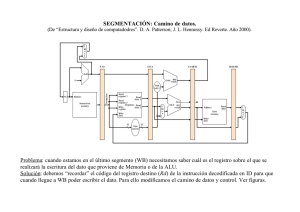

El protocolo descrito para los pares de señales from_T, to_T y from_R, to_R coincide con el

comportamiento de las señales RDY y STB\ del PIO. Conecto dispositivo T a puerto A porque

debe tener mayor prioridad.

Memorizo el byte alto de Dato_T con flanco de subida de from_T en un registro y agrego puertos

de 8 bits para byte alto de Dato_T y Dato_R

D[7..0]

N O T

A[6]

A[5]

A[4]

B/A\

C/D\

CE\

Clk

Dato_R[7..0]

to_R

from_R

PB[7..0]

B R D Y

BSTB\

C K

inst1

Dato_T[7..0]

to_T

from_T

PA[7..0]

A R D Y

ASTB\

M1\

IORQ\

RD\

A[0]

A[1]

O R 4

inst2

IEI

D0..D7

M 1

I O R Q

R D

A[7]

V C C

pio

IEO

INT\

int

inst

Dato_T[15..8]

from_T

D F F

D

PRN

inst5

Q

D[7..0]

D[7..0]

T R I

CLRN

inst4

A[4]

A[7]

A[6]

A[5]

A[4]

inst6

O R 6

N O T

inst12

N O T

inst8

I O R Q

W R

O R 6

N O T

inst7

D

PRN

CLRN

inst9

I O R Q

R D

A[7]

D F F

A[6]

A[5]

N O T

inst13

inst10

Q

Dato_R[15..8]

Facultad de Ingeniería – UDELAR

Int. a los microprocesadores – JULIO 2011

SOLUCIONES

b) Inicialización y reserva memoria

PIOconf_A

PIOconf_B

DatoT_low

DatoT_high

DatoR_low

DatoR_high

EQU

EQU

EQU

EQU

EQU

EQU

0x82

0x83

0x80

0x90

0x81

0x90

.Org 0x1000; Tabla en ROM

tabla_int:

DW rutint_T

DW rutint_R

.Org 0x8000; En RAM

R_Busy DB 0x00

.Org 0x0000

LD SP, 0x0000

;Config. PIO, canal A, dispositivo T

LD A, 01001111; Modo 1, entrada

OUT (PIOconf_A), A

LD A, 00000000; Vector int.

OUT (PIOconf_A), A

LD A, 10000011; Habilit. int.

OUT (PIOconf_A), A

;Config. canal B, dispositivo R

LD A, 00001111; Modo 0, salida

OUT (PIOconf_B), A

LD A, 00000010; Vector int.

OUT (PIOconf_B), A

LD A, 10000011; Habilit. Int.

OUT (PIOconf_B), A

IN A, (DatoT_low)

LD A, 0x00

LD (R_Busy), A

LD A, 0x10

LD I, A

IM 2

EI

CALL iniotros

Loop: CALL otros

JP Loop

; para subir RDY

pag. 4/4

c) Rutina interrupción Dispositivo R

;

preservo registros

;

si GetFifo devuelve dato

;

escribo dato en puerto

;

else

;

R_Busy = 00h

;

fin_si

;

restauro registros

;

habilito int, retorno

.Org 0x0200

rutint_R:

PUSH AF

PUSH BC

CALL GetFifo ; entre que verifico cola

; vacía y escribo R_Busy no deben

; entrar interrupciones del otro

; dispositivo

JP Z, enviar

LD A, 0x00

LD (R_Busy), A

EI

JP finR

enviar: EI

LD A, B

OUT (DatoR_high), A

LD C, A

OUT (DatoR_low), A

finR: POP BC

POP AF

RETI

d) Rutina interrupción Dispositivo T

;

preservo registros

;

leer dato de puerto

;

si (R_Busy = 0) entonces

;

escribo dato en puerto

;

R_Busy = FFh

;

else

;

PutFifo(dato)

;

fin_si

;

restauro registros

;

habilito int, retorno

rutint_T:

PUSH AF

PUSH BC

IN A, (DatoT_high)

LD B, A

IN A, (DatoT_low)

LD C, A

LD A, (R_Busy)

BIT 0, A

JP NZ, busy

LD A, 0xFF

LD (R_Busy), A

LD A, B

OUT (DatoR_high), A

LD A, C

OUT (DatoR_low), A

JP finR

busy: CALL PutFifo

finR: POP BC

POP AF

EI

RETI