microprocesadores y componentes del PC

Anuncio

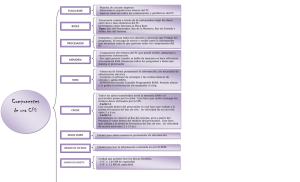

Estructura y Tecnología de Computadores Miguel Angel©1999-2002 Equipos Microinformáticos 1. El Ordenador. Es un dispositivo electrónico capaz de recibir un conjunto de instrucciones, o programa, y, a continuación, ejecutarlo realizando cálculos sobre los datos numéricos, o bien compilando y correlacionando otros tipos de información. Todo lo que hace un ordenador digital se basa en una operación: la capacidad de determinar si un conmutador, o 'puerta', está abierto o cerrado. Es decir, el ordenador puede reconocer sólo dos estados en cualquiera de sus circuitos microscópicos: abierto o cerrado, alta o baja tensión o, en el caso de números, 0 ó 1. Sin embargo, es la velocidad con la cual el ordenador realiza este acto tan sencillo lo que lo convierte en una poderosa herramienta. Las velocidades del ordenador se miden en megahercios, o millones de ciclos por segundo. Un ordenador con una velocidad de reloj de 900MHz, velocidad bastante representativa de un microordenador o microcomputadora, es capaz de ejecutar 900 millones de operaciones discretas por segundo. Las microcomputadoras para empresas (uso profesional) pueden ejecutar entre 2500 y 3000 millones de operaciones por segundo, mientras que las supercomputadoras utilizadas en aplicaciones de investigación y de defensa alcanzan velocidades muy superiores. La velocidad y la potencia de cálculo de los ordenadores digitales se incrementan aún más por la cantidad de datos manipulados durante cada ciclo. Si un ordenador verifica sólo un conmutador cada vez, dicho conmutador puede representar solamente dos comandos o números. Así, ON simbolizaría una operación o un número, mientras que OFF simbolizará otra u otro. Sin embargo, al verificar grupos de conmutadores enlazados como una sola unidad, el ordenador aumenta el número de operaciones que puede reconocer en cada ciclo. Por ejemplo, un ordenador que verifica dos conmutadores cada vez, puede representar cuatro números (del 0 al 3), o bien ejecutar en cada ciclo una de las cuatro operaciones, una para cada uno de los siguientes modelos de conmutador: OFF-OFF (0), OFF-ON (1), ON-OFF (2) u ON-ON (3). En general, los ordenadores de la década de 1970 eran capaces de verificar 8 conmutadores simultáneamente; es decir, podían verificar ocho dígitos binarios, de ahí el término bit de datos en cada ciclo. Un grupo de ocho bits se denomina byte y cada uno contiene 256 configuraciones posibles de ON y OFF (o 1 y 0). Cada configuración equivale a una instrucción, a una parte de una instrucción o a un determinado tipo de dato; estos últimos pueden ser un número, un carácter o un símbolo gráfico. Por ejemplo, la configuración 11010010 puede representar datos binarios, en este caso el número decimal 210, o bien estar indicando al ordenador que compare los datos almacenados en estos conmutadores con los datos almacenados en determinada ubicación del chip de memoria. El desarrollo de procesadores capaces de manejar simultáneamente 16, 32 y 64 bits de datos ha permitido incrementar la velocidad de los ordenadores. La colección completa de configuraciones reconocibles, es decir, la lista total de operaciones que una computadora es capaz de procesar, se denomina conjunto, o repertorio, de instrucciones. Ambos factores, el número de bits simultáneos y el tamaño de los conjuntos de instrucciones, continúa incrementándose a medida que avanza el desarrollo de los ordenadores digitales modernos. 1 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 2. CPU (Unidad Central de Proceso) La CPU puede ser un único chip o una serie de chips que realizan cálculos aritméticos y lógicos y que temporizan y controlan las operaciones de los demás elementos del sistema. Las técnicas de miniaturización y de integración han posibilitado el desarrollo de un chip de CPU denominado microprocesador, que incorpora un sistema de circuitos y memoria adicionales. El resultado son unos ordenadores más pequeños y la reducción del sistema de circuitos de soporte. Los microprocesadores se utilizan en la mayoría de los ordenadores personales de la actualidad. La mayoría de los chips de CPU y de los microprocesadores están compuestos de cuatro secciones funcionales: una unidad aritmética / lógica; unos registros; una sección de control y un bus interno. La unidad aritmética / lógica proporciona al chip su capacidad de cálculo y permite la realización de operaciones aritméticas y lógicas. Los registros son áreas de almacenamiento temporal que contienen datos, realizan un seguimiento de las instrucciones y conservan la ubicación y los resultados de dichas operaciones. La sección de control tiene tres tareas principales: temporiza y regula las operaciones de la totalidad del sistema informático; su descodificador de instrucciones lee las configuraciones de datos en un registro designado y las convierte en una actividad, como podría ser sumar o comparar y su unidad interruptora indica en qué orden utilizarán la CPU las operaciones individuales y regula la cantidad de tiempo de CPU que podrá consumir cada operación. El último segmento de un chip de CPU o microprocesador es su bus interno, una red de líneas de comunicación que conecta los elementos internos del procesador y que también lleva hacia los conectores externos que enlazan al procesador con los demás elementos del sistema informático. Los tres tipos de bus de la CPU son: un bus de control que consiste en una línea que detecta las señales de entrada y de otra línea que genera señales de control desde el interior de la CPU; el bus de dirección, una línea unidireccional que sale desde el procesador y que gestiona la ubicación de los datos en las direcciones de la memoria y el bus de datos, una línea de transmisión bidireccional que lee los datos de la memoria y escribe nuevos datos en ésta. HISTORIA DE LA MICROELECTRÓNICA Escalas de Integración: SSI ( Small Scale Integration ) - pequeña escala de integracióncircuitos de funciones lógicas elementales. número aproximado de componentes por circuito, 100. número aproximado de puertas lógicas, 10. MSI ( Mediun Scale Integration) - media escala de integracióncircuitos más complejos que los anteriores, de aplicación general realizan funciones lógicas más complejas. Son codificadores, multiplexores, contadores, etc... número aproximado de componentes por chip entre 100 y 1000. número aproximado de puertas lógicas, 100. 2 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 LSI (Large Scale Integration) - gran escala de integraciónrealizan funciones lógicas muy complejas. son circuitos propios de la lógica programable como: memorias, microprocesadores, etc... el número aproximado de componentes por chip está entre 1000 y 10.000. número aproximado de puertas lógicas, 1000. VLSI (Very Large Scale Integration) - muy gran escala de integraciónson circuitos con más de 10 millones de transistores por chip. CIRCUITOS LSI: El microprocesador. 2.1. Estructura básica de un sistema con microprocesador. BUS DE DIRECCIONES MEMORIA C.P.U. ROM RAM E/S BUS DE DATOS BUS DE CONTROL Figura 1. Básicamente un sistema digital basado en microprocesador es una estructura hardware controlada mediante un sistema software o programa. 2.2. Estructura interna de un sistema basado en microprocesador: El procesador toma los datos de la memoria principal, y los acumula en el registro de instrucciones con el orden de llegada en una memoria intermedia del tipo LIFO, estos son decodificados en el DECODIFICADOR DE INSTRUCCIONES donde cada instrucción es cambiada por su código máquina correspondiente. El programa almacenado en memoria sigue una secuencia preestablecida, que sólo se verá alterada si se produce una petición de interrupción desde un dispositivo de E/S. Cuando se produce una interrupción se ejecuta una bifurcación en la secuencia del programa. Esto provoca la ejecución de una subrutina dentro de la secuencia general del programa. El stack o pila es el conjunto de registros que forman la memoria intermedia, en esta pila se almacenan los datos que va enviando el Contador de Programa, que es quien lleva el control de la siguiente posición de memoria a la que hay que acceder. Cuando la ALU obtiene el resultado de la operación, lo posiciona en memoria a través del bus de datos. (ver figura 2.) 3 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 CISC FRENTE A RISC La tecnología CISC (Complex Instruction Set Code) es un elemento derivado de los anteriores desarrollos de Intel (486), y básicamente es la adoptada por los procesadores P54C, el PENTIUM. La necesidad de que sea compatible con las aplicaciones creadas para las anteriores CPU’s de Intel, hace que de nuevo se haya ampliado el conjunto de instrucciones para acomodar nuevas prestaciones. Ahora bien, se ha cambiado notablemente la forma de realizar el proceso interno para cada operación. Hasta el advenimiento del Pentium, uno de los factores diferenciadores entre procesadores CISC y RISC era el número de ciclos de reloj necesarios para completar una instrucción. Mientras una instrucción RISC se ejecutaba típicamente en un ciclo de reloj, una instrucción CISC se subdividía en varias fases, que requerían en su conjunto múltiples ciclos de reloj para completarse. BUS DE DATOS DIRECCIÓN 1 2 3 CARGAR ACUM. 45 CONTADOR DE PROGRAMA SUMAR 4 21 5 GUARDAR 6 8 7 STOP DECODIFICADOR DE INSTRUCCIONES BUS DE DIRECCIONES C.P.U. 8 9 REGISTRO DE INSTRUCCIONES RELOJ Y SEÑALES DE CONTROL 66 (RESULTADO) CONTROL MEMORIA REGISTRO ACUMULADOR ALU ALU Estructura interna y memoria. Figura 2. 4 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 El procesador Pentium mantiene buena parte de la arquitectura CISC, pero al mismo tiempo incorpora en su núcleo circuitería e instrucciones propias de un RISC. Hay instrucciones que requieren varios ciclos de reloj, pero a cambio otras se operan internamente en menos de un ciclo por instrucción. El sistema de doble pipeline o pipeline bifásica y algunas optimizaciones más permiten que el funcionamiento general se aproxime al ideal RISC y se ejecute una cadencia cercana a una instrucción por ciclo. Microinstrucciones CISC MEMORIA Allá por la tercera generación del ordenador cuando las máquinas comienzan a soportar Unidad de Control lenguajes de alto nivel, surgieron juegos de (Decodificación) instrucciones complejos, en los que cada instrucción equivalía a varias decenas de operaciones simples, llamadas “operaciones elementales” en lenguaje máquina. Así se evitaban muchos accesos a la Memoria memoria principal, al mismo tiempo que se de control sacaba el máximo rendimiento de la máquina, denominando a este tipo de UNIDAD DE DECODIFICACIÓN computadores CISC (juego de código de instrucción complejo). Al aumentar la complejidad de las ALU instrucciones máquina surgió la necesidad de una fase intermedia encargada de CPU almacenar los microcódigos E/S correspondientes a cada macroinstrucción. Esta unidad intermedia se denominó Memoria de Control. En los procesadores CISC se establece un intercambio, por parte de la memoria de control, entre la lógica cableada de las operaciones simples y la programada de las complejas. Así se resolvía el problema derivado de las distintas velocidades entre las dos secciones principales del procesador. Además se paliaba la divergencia semántica con las instrucciones de los lenguajes de alto nivel. El número de instrucciones CISC sólo está limitado por la capacidad de la memoria de control. Los computadores RISC sólo disponen de las instrucciones máquina más importantes y usadas, que, suelen ser menos de 50. En este tipo de computadores se ha incrementado el número de registros de propósito general para evitar accesos a memoria y ayudar a los compiladores a analizar los datos y controlar los flujos de forma óptima al conocerse las variables más usadas que se han asignado a los registros. Las instrucciones RISC tienen normalizados tanto su formato como su longitud, lo que favorece el funcionamiento fragmentado o pipe-line, al estar todos sus campos en sitios determinados. Sin embargo, dada la limitación del juego de instrucciones RISC únicamente a las funciones elementales, requieren empleo de coprocesadores especializados. 5 Unidad de Control (Decodificación) Miguel Angel©1999-2002 CÓDIGOS MÁQUINA MEMORIA CACHÉ DE CÓDIGO Y DE DATOS Microinstrucciones RISC MEMORIA UNIDAD DE CONTROL Estructura y Tecnología de Computadores ALU CPU E/S PROCESADOR RISC Figura 4. 2.3. ESTRUCTURA SEGMENTADA La segmentación es la técnica usada en los microprocesadores para incorporar un cierto grado de paralelismo, con el fin de aumentar su velocidad de procesamiento. También recibe el nombre de técnica tubular o "pipeline", y emplea la filosofía aplicada en las cadenas de montaje y ensamblado de las carrocerías de los coches, consistente en dividir el proceso total en varias fases o etapas y destinar a cada una de ellas un conjunto de hombres y/o máquinas para efectuarla. Intel introdujo por primera vez en el 8086 el funcionamiento segmentado, que dividía un proceso en varias partes y dotaba a la CPU de unidades para el tratamiento de cada parte, permitiendo trabajar simultáneamente a dichas unidades y dando lugar a una aceleración en el tiempo total de realización. Internamente el 8086 estaba formado por dos unidades o procesadores independientes: La unidad de ejecución: encargada de ejecutar instrucciones procedentes de la cola de instrucciones. La unidad de intercambio con el bus: realiza todas las transferencias con el bus del sistema. Se encarga de direccionar la memoria y las E/S soportando la transferencia de datos. La técnica de la segmentación puede aplicarse en la arquitectura de computadores al procesamiento de las instrucciones, que se dividen en 4 subfunciones o registros: 1) Búsqueda de la instrucción (BI) 2) Decodificación (D) 3) Búsqueda de operandos (BO) 6 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 4) Ejecución (E) BÚSQUEDA INSTRUCCIÓN ( lectura ) DECODIFICACIÓN BUSQUEDA OPERANDOS D BO E D I1 BO E BO I1 E BO I2 E I1 BI I1 I5 I4 I3 I2 RELOJ RELOJ t2 RELOJ D I2 t3 t2 BI I4 I5 RELOJ t3 SALIDA t1 D I3 t4 SALIDA t1 BI I3 I5 I4 SALIDA t1 BI I2 I5 I4 I3 EJECUCIÓN t2 SALIDA t1 La ejecución en cadena de las fases de una instrucción permite obtener a la salida del proceso el resultado o finalización de cada instrucción con cada impulso de reloj. Figura 5. Como se refleja en la Figura anterior, cuando se ejecuta una serie de instrucciones al ritmo de los impulsos que genera el reloj, con el primero de dichos impulsos se realiza la fase de búsqueda de la primera instrucción I1. Con el segundo impulso, I1 pasa a la Unidad de Decodificación (D), dejando libre a BI, que pasa a ser ocupada por la siguiente instrucción, I2. En el tercer impulso, I1 pasa a la Unidad de Búsqueda de Operandos, mientras que I2 llega a D e I3 se introduce a la unidad BI. Así se desarrolla en cadena la ejecución de una secuencia de instrucciones. Como podemos observar son necesarios cinco ciclos de reloj hasta obtener el primer resultado. 2.4. Coprocesador matemático. Procesador de operaciones en coma flotante, también llamado coprocesador matemático, coprocesador numérico y unidad de coma flotante; se trata de un coprocesador (procesador adicional al microprocesador principal del sistema) que realiza cálculos con números en coma flotante, en oposición a los números enteros. La inclusión de un procesador de coma flotante puede aumentar de forma considerable la velocidad de ejecución de funciones matemáticas y gráficas (los trabajos gráficos conllevan generalmente muchos cálculos), siempre que los programas estén diseñados para 7 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 reconocerlo y utilizarlo. A partir del Intel 80486 y Motorola 68040, los nuevos procesadores de estas familias incorporan lógica para realizar operaciones de coma flotante que hacen innecesario el uso de coprocesador matemático externo, es decir, llevan coprocesador integrado en la CPU. El coprocesador puede aumentar de forma considerable el rendimiento del sistema, siempre que el software de aplicación haga uso de él, ya que pone a disposición de la aplicación instrucciones aritméticas, trigonométricas, exponenciales y logarítmicas con las que no cuenta el procesador principal. El coprocesador también incorpora operaciones fundamentales para el cálculo de senos, cosenos, tangentes, arcotangentes y logaritmos. Si se utilizan estas instrucciones adicionales, las operaciones son realizadas por el coprocesador, permitiendo al procesador dedicarse a otras tareas. int el R Es la compañía más importante del mercado en la fabricación de microprocesadores y componentes electrónicos. Intel se fundó en 1968 cuando Bob Noyce (coinventor del circuito integrado) junto a Gordon Moore decidieron abandonar la empresa que fundaron con cuatro colegas más, “Fairchild”, por problemas burocráticos y de inestabilidad. La nueva tecnología de memoria basada en semiconductores prometía lo suficiente como para embarcarse en este proyecto, Intel acababa de nacer y su actividad inicial fue la de diseñar memorias con tecnología LSI. Poco después se les unió Andy Grove, que a la postre se convertiría en el líder de Intel. En el primer medio año de vida la joven empresa ingresó 2.682 dólares, en el otro medio año ya dobló esa cantidad. Así se ha venido sucediendo hasta ahora, con esos record de ganancias y sin que nadie le discuta el liderazgo a esta empresa que, hoy por hoy, está representada en todo el mundo. Uno de los grandes aciertos de Intel fue fabricar el primer chip considerado como una CPU. Se trataba del 4004, un diminuto procesador de 4 bits diseñado en 1969 que contaba sólo con 16 patillas y que se empleó como corazón de la primera calculadora. 8 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 HISTORIA DE LOS MICROPROCESADORES DE INTEL. Diseñado en 1969 y Comercializado en 1971 el 4004 de INTEL con un Bus de datos de 4 bits. 1972, el 8008 de INTEL Bus de datos de 8 bits. 1974, el 8080 de INTEL Bus de 8 bits. 1976, el 8085 de INTEL Bus de 8 bits. 1978, el 8086 1979, el 8088 Primer procesador con bus de 16 bits. Bus de direcciones de 20 líneas: podía direccionar hasta 1Mb de Memoria. Dos versiones: 4.77 y 8Mhz. de velocidad de reloj. Bus interno de 16 bits / Bus externo de 8 bits. (Más lento que su predecesor, el 8086) Bus de direcciones de 20 líneas. Frecuencia de reloj 4.77Mhz. EL PRIMER PC, fabricado por IBM, utilizaba el 8088 de INTEL y apareció por primera vez en el mercado en 1982. 1984, Primer AT (Advanced Technology), el 80286 a 12Mhz y 16MHz. Bus de datos de 16 bits (ISA a 8MHz). Bus de direcciones de 24 líneas. Coprocesador matemático opcional (80287). 1985, el 80386 a 16, 20, 25 y 33MHz. (Coprocesador opcional 80387) Bus de datos y de direcciones de 32 bits. Aparecieron dos versiones: SX y DX (Single y Double Word external). 1989, el 80486 también en versiones DX y SX. Bus de 32 bits con formatos ISA y EISA. (El bus ISA trabaja con 16 bits a 8MHz. El bus EISA trabaja con 32 bits a 33MHz). Lleva coprocesador matemático interno. Es un procesador CISC: código de instrucción completo. En un principio trabajaba a una frecuencia de reloj de 25MHz, más tarde aparecieron versiones a 33MHz y 40MHz. Poco tiempo después aparecieron los... 1992, 1993, el 80486DX2 y el 80486DX4. Lo que hacen es duplicar y triplicar internamente la frecuencia de reloj del sistema. Integran en su interior 1,6 millones de transistores, sobre estructura de 0,6 micras y con una alimentación de 3,3volts. (Bus de 32 bits con formatos VLB: 33MHz; y PCI: 64 ó 32 bits a 33MHz) Ejecutan una instrucción por ciclo de reloj. Trabajan a 50, 66, 75 y 100MHz. 9 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 MARZO 1993, (5ª generación de procesadores INTEL) el PENTIUM o 586 ( nombre clave P54CX) es un Procesador CISC/RISC: código de instrucción reducido. Inicialmente trabajaba con unas frecuencias de 60 y 66MHz. Construido con 3,1 millones de transistores. Ejecuta dos instrucciones por ciclo de reloj. Es cinco veces más potente que el 486 a 33. ChipSet 430FX, VH, HX y TX. Fabricado con proceso BI-CMOS de geometría de 0,8 micras y con arquitectura superescalar. Bus interno de 256 bits. Bus externo de 64 bits, PCI. 1994/1995 Aparecen nuevas versiones del PENTIUM. PENTIUM a 75, 90, 100, 120 y 133MHz. DICIEMBRE 1995, Se presenta en el mercado el PENTIUM-PRO a 150MHz. Posteriormente aparecen tres versiones más: a 166, 180 y 200MHz. Es un procesador especialmente concebido para aplicaciones de 32bits. (Profesional). Construido con geometría de 0,6 micras. Microarquitectura superescalar. Es un RISC puro. Integra 5,5 millones de transistores. Puede ejecutar hasta 3 instrucciones por ciclo de reloj. ENERO 1996, Aparece el PENTIUM a 150 y 166MHz. Fabricados en 0,35 micras y alimentados a 3,3 volts. JULIO 1996, Llega el PENTIUM a 200MHz. Este chip se basa en la tecnología avanzada de proceso de 0,35 micras. Está construido con un encapsulado PPGA (Plastic Pin Grid Array) más eficaz térmicamente. SEPTIEMBRE 1996 PENTIUM 166 Y 200MHz MMX (P55CX). PENTIUM 233MHz MMX PENTIUM 266MHz MMX 1997 PENTIUM II 233MHz (MMX)- Slot 1. (nombre clave KLAMATH). ChipSet 440LX y 440FX. PENTIUM II 266MHz PENTIUM II 300MHz PENTIUM II 333MHz 1998 MAYO 1998 PENTIUM II 400MHz-Slot 2. (Bus de sistema a 100MHz). ChipSet440BX. - (Xeon™) 1999 PENTIUM III 450 – SLOT1 (KATMAI – MMX2). Bus a 100MHz. AGP 4x. 10 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 ESQUEMATIZACIÓN DE LOS Pentium DE INTEL Y DE SU MÁS FIEL COMPETIDOR. Pentium-clásico (P54CX) 1993 Procesador 60 66 75 90 100 120 133 Socket 7 CISC/RISC (FPU) ChipSet 430FX, VH, HX y TX. (Es cinco veces mas potente que un 486 a 33MHz) L1 Un Pentium se puede definir como dos procesadores 486 en paralelo ( mas exactamente, un 486SX y un 486DX en paralelo) 16KB 256 bits 3,1 millones de transistores BI-CMOS 0,8 micras L2 64 bits BUS DE SISTEMA 66MHz 256/512KB MEMORIA CACHÉ EDO-RAM MEMORIA PRINCIPAL Pentium-Pro (200MHz) 1995 L2 Procesador 150 166 180 200 (FPU) RISC 1MB de Caché personalizada. Bus de alta velocidad 200MHz 3I/CLK Socket 8 L1 32KB 0,6 micras microarquitectura superescalar 5,5 millones de transistores Especialmente concebido para aplicaciones de 32 bits (Windows NT) Pentium-MMX (P55CX) 256/512KB BUS DE SISTEMA 66MHz CACHÉ L2 Encapsulado PPGA (Plastic Pin Grid Array) a partir del 200MHz. 1996 Procesador CISC/RISC Socket 7 MMX 57 instr. 166 200 233 266 ChipSet 430 TX (VX mínimo) (FPU) L1 32KB 0,35 micras Alimentación Dual: Núcleo (core) 2,8V Patillaje (I/O) 3,3V nota: (FPU) Unidad de Procesamiento en coma Flotante, o más conocido como Coprocesador Matemático. 11 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 Pentium II - MMX (KLAMATH) 1997 Procesador 233 266 300 333 L2 L1 Ej.: 300MHz Slot 1 32KB CLK/2 150MHz ChipSet 440LX-FX 512KB SRAM Con ChipSet LX se pueden construir placas que soportan dos procesadores en paralelo. MMX SEC (Single Edge Compact) Arquitectura DIB (Dual Independent Bus) 0,35 micras BUS DE SISTEMA 66MHz Pentium II - MMX (Deschutes)/100 1998 Procesador L2 L1 350 400 450 32KB Slot 1 CLK/2 ChipSet 440BX 512KB SRAM MMX 0,25 micras SEC (Single Edge Compact) Arquitectura DIB (Dual Independent Bus) 440 ChipSet BX BUS DE SISTEMA 100MHz Unidad E/S MEMORIA (SDRAM) 100 MHz. PC/100 Celeron 266/300 Procesador Slot1 L1 ChipSet 440EX 32KB no tienen caché L2 MMX 0,25 micras 7,5 millones de transistores SEC Alimentación Dual BUS DE SISTEMA 66MHz 12 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 Celeron 300A/466 (Mendocino) 9,1 millones de transistores. Procesador 300 333 366 400 433 466 1998 L2 L1 Slot1-S.370 ChipSet 440EX 32KB MMX =CLK Optimizado para alpicaciones de 32 bits. La caché L2 trabaja a la misma velocidad que el procesador. 128KB SRAM 2,0V 3,3V 0,25 micras S.E.P.P. Alimentación Dual BUS DE SISTEMA 66MHz Pentium III (KATMAI) NÚMERO DE IDENTIFICACIÓN 450 500 550 600 .... 850 866 933 1000 1999 Juego de instrucciones IA-32 Procesador 3D 70 New Instruction S.S.E. L2 L1 Slot 1- S.370 Streaming SIMD Extensions 32KB 512KB CLK/2 SRAM MMX 0,25 micras 0,18 micras 2,0 V 3,3 V 9,5 millones de transistores S.E.C.C.2 Package / FC-PGA Package ChipSet 810 Incorpora 70 nuevas instrucciones S.S.E.(equivalentes a las 3D Now). Nota: son equivalentes pero incompatibles. Dynamic Execution Technology. Dual Processor Support. Internal Streaming SIMD Extensions Arquitectura DIB. BUS DE SISTEMA 100/133 Mhz PENTIUM -4 IA-64 Socket 370. FC-PGA2 0.13 micras Nota: el nuevo procesador de intel merece una atención especial, por lo que será tratado en otro momento. 13 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 AMD K5 PR75 PR90 PR100 PR120 PR133 PR166 L1 (Pentium clásico) Socket 7 Generalmente estos procesadores indican como medida de velocidad el denominado P-rating, que es una medida de velocidad comparada con los procesadores de Intel y según los resultados del test Winstone 98. 24KB L2 en placa madre (512KB) BUS de Sistema a 66MHz. M M AMD X 6 166 200 233 (Pentium II) Socket 7 ChipSet 430VX (Nx686) NexGen L1: 64KB L2: en placa Alimentación Dual: 2.8/3.3V BUS de Sistema a 66MHz. 8.8 millones de transistores X M 300 350 M AMD 6 3D NOW (Katmai) Zócalos: Socket 7 a 66MHz Super 7 a 100MHz juego de 24 instrucciones ChipSet AMD640. L1: 64KB Alimentación Dual: 2.2/3.3V Soporta Bus de sistema a 100MHz AGP, USB y Ultra DMA. 21,3 millones de transistores a 025 micras. (PentiumIII) M AMD 6 X M 400 450 L3: L1: 64KB L2 se comunica con la CPU a la frecuencia de reloj Zócalo Super 7 a 100MHz. Alimentación Dual: 2.4/3.3V L2: 256KB La caché de la placa base pasa a trabajar como memoria de tercer nivel. Su principal característica es su nuevo diseño de caché de 3 niveles. Esto se consigue incorporando una caché L2 de 256KB en el núcleo de la CPU. 14 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 Micros: Retrospectiva y actualidad. E l microprocesador es el cerebro del ordenador, el encargado de procesar todas las instrucciones de programas y dispositivos. Aunque se trata de una parte fundamental en todos los ordenadores, la velocidad de un ordenador no sólo viene determinada por el procesador, la velocidad de todos sus componentes es fundamental y ello determina un mayor o menor rendimiento del sistema. El cuello de botella puede estar en cualquiera de los elementos que forman un ordenador como puede ser el adaptador gráfico, la memoria RAM o el subsistema de discos duros. La velocidad de un ordenador depende de cuatro aspectos fundamentales (procesador, memoria, tarjeta gráfica y disco duro) y ninguno de ellos es más importante que los otros. Arquitectura de un ordenador A grandes rasgos, un microprocesador de la última generación está formado, por una CPU (Unidad Central de Proceso) y una caché de nivel 1 (level 1 o L1), además de una ALU (Unidad Aritmético-lógica) . Lo más destacable es el concepto de caché y la distinción entre caché de nivel 1 y caché de nivel 2. El término caché se utiliza para designar una zona de almacenamiento rápido. El procesador accede a la caché a mucha más velocidad de lo que lo hace a la memoria principal. Gracias a la memoria caché se consigue aumentar la velocidad de proceso, pues en vez de acceder a los datos de la memoria principal, el procesador primero "mira" si esos datos están en el caché que es mucho más rápido. Diagrama de un ordenador actual Figura 1. 15 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 Caché L1. La memoria caché de nivel 1 está incluida en el propio encapsulado del procesador. Al integrar el caché en el chip del procesador se consigue que la CPU tenga un acceso muy rápido al caché, ya que la conexión entre ambos es casi directa. Normalmente, se utilizan 16KB o 32KB de caché L1 (aunque existen procesadores con 64KB de caché L1), utilizando la mitad del caché para datos y la otra mitad para código. Caché L2. La memoria caché de nivel 2 también se utiliza para acelerar la comunicación entre el procesador y la memoria RAM. Se trata de una cantidad más grande de memoria, entre 256KB y 512KB, donde se guardan los datos más usados para acceder a ellos con mayor velocidad. Resulta más rápido leer la memoria caché que la RAM, porque la memoria caché es memoria estática (SRAM), con tiempos de acceso del orden de 10 nanosegundos, mientras que la memoria RAM es memoria dinámica (DRAM), cuya velocidad no puede bajar de 50 nanosegundos. Además de emplear tipos de memoria diferentes, para aumentar la velocidad de acceso al caché L2, algunos procesadores se construyen sobre un mismo circuito que incluyen el caché L2, como es el caso de los Pentium-Pro y Pentium II, estableciendo de esta forma un bus de alta velocidad entre el procesador y el caché. ChipSet. Como su nombre indica, el chipset es un conjunto de chips que se integran en la placa madre y que contienen todos los controladores y rutinas que ponen en comunicación el procesador con las diferentes partes funcionales del ordenador. El chipset incluye la unidad de gestión de memoria (MMU), el controlador de interrupciones (PIC), etc. Puesto que el chipset decide la comunicación del procesador con el resto del ordenador, según sus características se podrá utilizar el mismo procesador para crear ordenadores con capacidades diferentes, por ejemplo, hay chipset que permiten trabajar con un Pentium, mientras que otros permiten trabajar con 2 Pentium en paralelo. Es fundamental destacar la transcendencia del chipset en un ordenador, puesto que decide cosas tan importantes como la cantidad máxima de memoria RAM, el tipo de memoria RAM (EDO DRAM ó SDRAM) que soporta la placa madre, el número de procesadores que se pueden emplear en paralelo, la velocidad del bus de sistema o la posibilidad de utilizar puertos USB, tarjetas de vídeo AGP o discos duros Ultra DMA. Bus de Sistema y bus de Datos. La comunicación entre el procesador, la memoria RAM y el chipset se realiza a través del bus de sistema. Luego, cuando se empiezan a enviar datos a los periféricos conectados en los slots de expansión del ordenador, se utiliza el bus de datos. Estos buses miden su velocidad en megahertzios (millones de ciclos por segundo), que indica la velocidad con la que se envían los datos por el bus. Además, también hay que tener en cuenta al ancho de banda del bus (por ejemplo, 16, 32 ó 64 bits), es decir, la cantidad de datos que se pueden enviar en cada ciclo. Sabiendo la velocidad del bus y el ancho de banda, se puede obtener la velocidad de transferencia máxima del bus en bytes por segundo. Por ejemplo, un bus de 8 MHz con un ancho de banda de 16 bits (2 bytes) puede trabajar con una velocidad de transferencia máxima de 8 millones/seg. x 2 bytes = 16 MB/seg. 16 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 La familia intel Pentium El Pentium clásico. El primer Pentium (denominado técnicamente P54CX) apareció en 1994, como exponente de la quinta generación de los procesadores Intel. Un Pentium se puede definir como dos procesadores 486 en paralelo (más exactamente, un 486SX y un 486DX en paralelo), por lo que puede ejecutar más instrucciones que un 486, normalmente 2 instrucciones por ciclo de reloj. Existen Pentium de diferentes velocidades de reloj, con modelos que van desde los 60 hasta los 200MHz. Todos poseen 16 KB de caché L1 y soportan entre una cantidad variable de caché L2, cantidad que depende del ChipSet usado en la placa base, que es externa al micro conectada al procesador a través del bus de sistema. Lógicamente, la velocidad con la que accede el procesador a la caché L2 es la velocidad del propio bus de sistema, que según el modelo corresponde a 60 ó 66MHz. El Pentium se introduce en la placa base sobre zócalo ZIF, versión Socket 7, que como veremos es el zócalo en el que se apoyan otros fabricantes como AMD y Cyrix para sus procesadores. El Pentium Pro. Este procesador aparece en 1995 y está especialmente concebido para servidores, estando ligado al sistema operativo Windows NT. Esto es debido a varias razones. Por una parte, el Pentium Pro está preparado para trabajar en equipos con hasta cuatro Pentium Pro en paralelo, lo cual resulta fundamental para las situaciones críticas de los servidores. Además el Pentium Pro es muy lento escribiendo a sus registros de segmento, escritura que se produce con mucha frecuencia al ejecutar software de 16 bits (como Windows’95) y pocas veces al ejecutar software de 32 bits (como Windows NT). El resultado es que trabajando con Windows 95 un Pentium Pro es más lento que un Pentium clásico de la misma velocidad de reloj, pero mucho más rápido con Windows NT. La principal característica del Pentium Pro es que dentro del propio chip se incluye tanto el procesador como la memoria caché de nivel 2, los dos unidos mediante un bus de alta velocidad (se trata de un paquete cerámico con dos cavidades cuadradas que se pueden observar a simple vista). De esta forma, se consigue que el procesador sea capaz de acceder a la caché L2 a la misma velocidad del reloj del procesador. Un Pentium clásico a 200MHz accede a la caché L2 a la velocidad del bus de sistema, 66MHz, mientras que un Pentium Pro a 200MHz accede a su caché L2 a 200MHz. Además de la velocidad cuenta la cantidad, pues existen versiones del Pentium Pro con 1MB de caché L2, frente a los 512KB habituales en el caché L2 del Pentium clásico. Además el Pentium Pro puede ejecutar 3 instrucciones en cada ciclo de reloj (por las 2 instrucciones del Pentium) e incluye características de ejecución dinámica (capacidad de ejecutar instrucciones en cualquier orden, ejecutando la más adecuada según la lógica del programa). La versión más potente de Pentium Pro es de 200MHz con 1MB de caché L2. Este Pentium de 32 bits, con núcleo RISC puro, se inserta sobre zócalo ZIF versión Socket 8. Pentium MMX. En 1996 nace el P55C o Pentium MMX. Se trata de un procesador Pentium al cual se le han asignado un juego extra de 57 instrucciones que aceleran el procesamiento de vídeo, audio y gráficos, aumentando el rendimiento de las aplicaciones multimedia. Además de las instrucciones MMX, este Pentium se integra con 32KB de caché L1 (16KB para código y otros 16KB para datos), frente a los 16KB del P54C. En lo demás no cambia, manteniéndose la velocidad del bus a 66MHz e insertándose sobre Socket 7. Este procesador utiliza para su funcionamiento dos niveles de voltaje distintos, el patillaje del procesador se alimenta a 3,3 voltios, mientras que el núcleo del chip requiere 2,8 voltios. Por lo que necesita placas base con alimentación dual. Además de estar provistas de un ChipSet 430VX mínimo. Que son los primeros grabados para soportar la tecnología MMX. Aunque posteriormente Intel lanzó el conjunto de chips 430TX. Este chipset está compuesto por dos núcleos PCIset que incrementan el rendimiento de los procesadores MMX. 17 Estructura y Tecnología de Computadores Pentium® II Processor 450MHz Miguel Angel©1999-2002 Pentium II. El Pentium II aparece en el mercado a mediados de 1997 y fue conocido durante mucho tiempo con el nombre estratégico de Klamath, se trata de un procesador que se monta sobre un cartucho que incluye una caché L2 de 512KB. Es necesario diferenciarlo del Pentium Pro, en el cual existe una caché L2 personalizada y que se encuentra integrada en una de las dos cavidades del procesador. Intel, en el Pentium II, lo que hace es coger el chip convencional del procesador MMX y varios chip de memoria SRAM que servirán como caché L2, establecer un bus entre ellos, integrarlos en una pequeña placa de circuito impreso denominada cartucho SEC (Single Edge Compact) y recubrirla de una que es lo que envoltura de plástico y metal conocemos finalmente como Pentium II. El Pentium II incorpora dos buses dentro del chip y por eso se dice que tiene arquitectura DIB (Dual Independent Bus), uno es el habitual bus que conecta el procesador al bus de sistema y el otro es un bus oculto dentro del Pentium II que conecta el procesador con la caché L2. Este enfoque de dos buses permite al Pentium II aumentar la velocidad de acceso al caché L2, que ya no depende del bus de sistema (como el Pentium), aunque tampoco llega a igualar la velocidad de reloj del procesador (como en un sistema con Pentium Pro), quedándose en la mitad de la velocidad de reloj del procesador. Esto significa que un Pentium II a 300MHz accede a la caché L2 a 150MHz y no a los 66MHz habituales del bus de sistema. Está claro que el cartucho SEC donde se aloja el Pentium II y su caché L2 rompe con el tamaño habitual del Pentium clásico y el Pentium MMX, por lo que no se puede instalar sobre un zócalo Socket 7 de la placa madre. El Pentium II tiene la forma de una tarjeta de ampliación y se introduce en una ranura especial denominada Slot 1. Se requiere una placa madre especial que soporte Slot 1 y que incluya un ChipSet 440LX ó 440FX. Al igual que un Pentium MMX, el Pentium II integra 32KB de caché L1 e incluye el juego de instrucciones MMX. Como ya se ha comentado, los ordenadores con Pentium II tienen el chipset 440 LX, que permite construir placas con bus AGP para tarjetas de vídeo, con el nuevo bus de puertos USB y con discos duros Ultra DMA. Además, este chipset está preparado para soportar dos Pentium II en paralelo sobre la misma placa madre. Actualmente existen versiones a 233MHz, 266MHz, 300MHz y 333MHz. 18 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 LA TECNOLOGÍA DE LOS ZOCALOS DEL Pentium®. La aparición del Slot 1 en los procesadores Pentium II ha sido un gran motivo de controversia, pues ha recibido críticas que acusan a Intel de buscar con ello la desaparición del Socket 7, donde se han apoyado los fabricantes AMD y Cyrix para construir sus procesadores. La principal razón de esta acusación reside en que Intel no ha hecho públicas las especificaciones del Slot 1, más bien al contrario, afirma que existen patentes a nivel del sistema en el desarrollo del bus del Slot 1 (denominado bus P6). ¿Responde el slot 1 a una estrategia de marketing o a una necesidad del mercado? La respuesta es que el Slot 1 ofrece interesantes innovaciones tecnológicas, pero también es cierto que Intel ha decidido buscar las soluciones en una oferta propietaria antes que intentar mantener la compatibilidad con el Socket 7. Probablemente, lo más lógico habría sido que Intel hiciera públicas las especificaciones del Slot 1 pero la compañía no va a tomar una decisión en contra suya. La principal ventaja del Slot 1 es que utiliza procesadores conectados al caché L2 mediante un bus especial - La tecnología DIB-, lo cual aumenta la velocidad de acceso al caché L2. Como ya se ha comentado, el Pentium II permite acceder al caché L2 a la mitad de la velocidad de reloj. Es decir, un procesador a 233 MHz en un Slot 1 accede al caché a 166 MHz, mientras que un procesador a 233MHz en un socket 7 accede al caché a la velocidad del bus de sistema (66 MHz). Además de una mayor velocidad del caché L2, la ventaja de los procesadores para Slot 1 es que el bus de sistema se limita únicamente a gestionar accesos a memoria y las peticiones de los periféricos de entrada/salida, sin tener que ocuparse de la gestión del caché L2 (que es realizada por el bus especial que va entre el procesador y el caché L2). procesadores similares al Pentium Pro que incluyan dentro del mismo chip el caché L2, probablemente usando la misma velocidad de reloj. El inconveniente de este tipo de procesadores es que resulta muy difícil subir la velocidad del reloj Existen proyectos serios para crear placas madre Super 7 que incorporan un Socket 7 con un bus de sistema a 100MHz e incluyen nuevas tecnologías como AGP, USB o Ultra DMA. Pero el socket 7 se pone casi al límite con un bus a 100MHz, haciendo complicado el diseño de chipset necesario para esta tecnología (si hubiese sido tan fácil, probablemente lo habría llevado a cabo hace años Intel con el Pentium MMX). Y de todas formas, el acceso al caché L2 de un procesador Socket 7 en un bus a l00MHz, siempre será más lento que el más lento de los Pentium II (el modelo a 233 MHz accede al caché a 116 MHz). El resultado es que AMD y Cyrix tendrán que cambiar en el futuro a un nuevo zócalo, ya sea logrando la compatibilidad con el Slot 1 o diseñando uno nuevo. Con esta situación y la reciente aparición del Slot 1, no se comprende por qué intel propone otro nuevo zócalo (Slot 2) para los futuros Pentium II dirigidos a servidores y estaciones de trabajo. Y tampoco se comprende su interés en cubrir el mercado de PCs de nivel bajo-medio con ordenadores Slot 1 (basados en la gama de procesadores Celeron), cuando podían haberse utilizado perfectamente Pentium MMX a mayor velocidad o, simplemente haber dejado que bajaran los precios de los Pentium II a 233 y 266 MHz. Para luchar contra esta limitación del Socket 7 AMD y Cyrix pueden intentar aumentar el caché L1 de sus sistemas, pues ambas compañías ofrecen procesadores con 64KB frente a los 32KB del Pentium MMX y el Pentium II. Pero al final tendrán que crear 19 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 TECNOLOGIAS para 1998-1999. Pentium Deschutes. De entrada decir que no existe ningún procesador de Intel con este nombre, sino más bien Deschutes se ha utilizado por la compañía para designar procesadores creados con tecnología de fabricación de 0,25 micras destinada al Pentium II (en vez de la tecnología habitual de 0,35 micras). De hecho esta tecnología está ya superada, pues existe en el mercado el Pentium II a 333MHz con tecnología de 0,25 micras. Pentium II con bus de 100MHz. El Pentium II a 350 y 400MHz están preparados para trabajar con un bus de sistema de 100MHz. Desde los tiempos del 486 apenas había habido cambios en el bus de sistema, que se seguía manteniendo a 60 ó 66MHz. Esta lenta velocidad del bus de sistema estaba empezando a generar un cuello de botella importante, sobre todo en el acceso a la memoria RAM. Al aumentar a 100MHz el bus de sistema, se resuelve el problema, aunque requiere placas madre capaz de soportar memoria SDRAM (que está preparada, a diferencia de la EDO RAM, para trabajar con un bus de sistema de esta velocidad). Lógicamente, un cambio en la velocidad del bus de sistema exige un nuevo chipset que soporte este cambio fundamental para los componentes que rodean al procesador. Este nuevo chipset es el 440BX. Por lo que, no se podrá introducir un Pentium II /100 en las placas con chipset 440LX. Por lo demás, las características de un Pentium II con bus de 100MHz son iguales que los primeros Pentium II aparecido en el mercado, aunque, por supuesto, utilizan tecnología de fabricación de 0,25 micras (son Deschutes). Pentium II para Slot 2. Se trata del procesador que sustituye al viejo Pentium Pro como solución para sistemas servidores y estaciones de trabajo especializadas. Se trata de Pentium II /100 a 400 y 450MHz que trabajan con bus de sistema a 100MHz; permite trabajar con hasta cuatro procesadores en paralelo; incluye caché L2 de 2MB; y pueden acceder a la caché L2 a la velocidad de reloj. Además, aumentan el límite de la memoria RAM a 4GB (el Pentium II para Slot 1 sólo llega 512MB) y necesita un nuevo chipset, el 450NX. Se trata de procesadores fabricados con la tecnología de 0,25 micras. Por supuesto, el slot 2 es incompatible con el slot 1. Celeron 266. Este procesador aparece en el mercado con el propósito de posicionarse como el sustituto del Pentium MMX en la gama baja-media de ordenadores personales. A la hora de explicar sus características salta a la mente el antiguo procesador 486SX. Recordemos que un 486 normal o DX incluía un coprocesador matemático, mientras que el 486SX era un 486 con el coprocesador desactivado. El nuevo Celeron se puede considerar como un Pentium II sin caché L2 y, para abaratar los costes de fabricación, no se ha envuelto en el cartucho SEC del Pentium II. El procesador Celeron va acompañado de un nuevo chipset (440EX) que permite crear ordenadores con sólo 1 CPU, 3 ranuras ISA y 2 módulos DIMM, aunque AGP y Ultra DMA. Mendocino (Celeron 300 y 333). Este procesador que se estima aparezca a finales de 1998, lo hará en dos versiones 300MHz y 333MHz y pretende posicionarse en la gama media de usuarios domésticos y profesionales, por encima del Celeron 266 y por debajo de los Pentium II/100. Se trata de un procesador similar al Celeron, pero en el que ahora de nuevo se vuelve a añadir el caché, incorporándose 128KB de caché L2. Esta cantidad de caché puede parecer pequeña cuando de compara con los 512KB de un Pentium II, pero Mendocino puede acceder al caché L2 a la velocidad de reloj del procesador (y no a la mitad como el Pentium II). 20 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 Katmai. Para el año próximo (1999) se espera la aparición de un nuevo procesador de Intel, el Katmai, que incorpora 70 nuevas instrucciones que se añaden a las MMX para aumentar el rendimiento multimedia y de los gráficos 3D. Este conjunto de instrucciones lo ha denominado Intel como Katmai o MMX2. También soportará la futura generación de memorias, ya sea SDRAM II (puede leer dos celdas de memoria en cada ciclo de reloj) o Direct Rambus DRAM (utiliza buses especiales para conseguir una velocidad 10 veces superior a la memoria DRAM convencional) . Permitirá la implantación del modo AGP 4x (que ofrece una vía de comunicación entre el procesador y la tarjeta gráfica que puede alcanzar una velocidad de transferencia máxima de 1GB/seg.). Merced. En el año 2000 aparecerá el procesador que hoy por hoy nos han dado ha conocer con el nombre de Merced, que responde a un desarrollo conjunto de Intel y Hewlett-Packard. Se trata del primer procesador de Intel de 64 bits, que utiliza un conjunto de instrucciones denominado IA64 y comenzará con una velocidad de reloj de 600 MHz. El procesador Merced soportará las instrucciones 3D del Katmai y estará fabricado con tecnología de 0,18 micras. Está recibiendo un amplio respaldo de la industria y Microsoft ya ha anunciado una versión prebeta de Windows NT 64 bits para finales de este año. LOS COMPETIDORES DE INTEL Los procesadores AMD La compañía Advanced Micro Devices es el principal competidor de Intel en el terreno de los procesadores. Tanto AMD como Cyrix sufren las consecuencias de la situación casi de monopolio por parte de Intel. En realidad, estos fabricantes producen procesadores completamente compatibles con los Intel y permiten ejecutar sin problemas todos los programas existentes. AMD K5. El procesador K5 ofrece unas prestaciones y características similares a la del Pentium clásico, e igual que él ha de considerarse ya prácticamente obsoleto. Como el Pentium, el K5 tiene el tamaño y formato para un zócalo Socket 7. Generalmente estos procesadores indican como medida de velocidad el denominado P-rating, que es una medida de velocidad comparada con los procesadores de Intel y según los resultados del test Winstone 98. Por ejemplo, un procesador PR75 indica que su rendimiento es similar a un Pentium a 75MHz. Del K5 existen modelos PR75, PR90, PR100, PR120, PR133 y PR166. Puesto que el K5 utiliza una placa base con Socket 7, el caché L2 es el caché de la placa madre, que pueden llegar a ser 512KB a los que accede según la velocidad del bus de sistema (66MHz). Hay que señalar que el K5 ofrece 24KB de caché L1 integrada en el chip, frente a los 16KB del Pentium clásico. AMD K6. La mejor definición que se podría dar del K6 es la de un "Pentium II para Socket 7". Es decir, el K6 ofrece un rendimiento similar a los Pentium II, con la ventaja de poder emplearse en las placas madre que utilizan Socket 7, lo cual protege la inversión que se hubiera realizado en esta tecnología. La mayoría de las placas madre con Socket 7 actuales están preparadas para trabajar con Pentium, Pentium MMX, AMD K6 y Cyrix 6x86MX, incluso detectando al arrancar el tipo de procesador incorporado. El K6 no fue diseñado inicialmente por AMD, que se encontró con problemas en el desarrollo del K5 y compró la compañía NexGen por su procesador Nx686, que es la base del K6. 21 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 Este procesador, al igual que ocurriera con el Pentium MMX, utiliza para su funcionamiento dos niveles de voltaje distintos, el patillaje del procesador se alimenta a 3,3 voltios, mientras que el núcleo del chip requiere 2,8 voltios. Por lo que necesitará placas base con alimentación dual y estar provistas de un ChipSet 430VX mínimo. El K6 incluye el conjunto de instrucciones MMX y tiene 64KB de caché L1 frente a los 32KB de un Pentium II. Existen modelos a 166, 200 y 233MHz (en el K6 no se utiliza el P-rating y esa velocidad de reloj les posiciona al mismo rendimiento que los Pentium II de igual velocidad de reloj). A igualdad de velocidad de reloj, un K6 es más rápido que un Pentium MMX, pero un poco más lento que un Pentium II. Este rendimiento inferior respecto al Pentium II se debe a que el K6 es más lento gestionando las instrucciones MMX y en punto flotante (entre otras cosas, porque el PentiumII puede ejecutar 3 instrucciones por ciclo de reloj, frente a las 2 del K6), y porque todos los procesadores Intel tienen unidades en coma flotante (FPU) con pipeline (es decir, que pueden iniciar una segunda instrucción mientras esperan los datos de la instrucción actual), mientras que los procesadores AMD y Cyrix no soportan esta característica. De todas formas la gran ventaja del K6 es que es mucho más económico que el Pentium II. AMD K6 3D. Se ha presentado una nueva versión del K6, se trata del K6 3D, en versiones a 300 y 350MHz y que añade 24 nuevas instrucciones en el procesador para acelerar la gestión 3D en gráficos, audio, vídeo y otras aplicaciones multimedia. Es importante señalar que ese conjunto de instrucciones multimedia son propiedad de AMD y por tanto diferentes e incompatibles con las instrucciones MMX2 del procesador Katmai, por lo cual los programadores tendrán que elegir entre utilizar un juego de instrucciones u otro. El K6 3D necesita un bus de sistema de 100MHz, lo cual exige placas base con un nuevo chipset, por ejemplo, el AMD 640 o un futuro chipset que creara el fabricante. En este sentido, es fundamental para el desarrollo de los procesadores futuros de AMD y Cyrix la aparición de las denominadas placas base Super 7, que son placas con zócalos Socket 7 pero con todas las novedades que incorporan las nuevas placas base con Slot 1, es decir, bus de 100MHz y soporte de AGP, USB y Ultra DMA. Otros procesadores son los de la marca Cyrix, como el M1, equivalente al Pentium clásico ó el M2, que es la alternativa de Cyrix a los Pentium II. La apuesta más revolucionaria de esta marca es el procesador Cyrix MediaGX, que incorpora dentro del mismo procesador un chip de sonido, uno de gráficos, el controlador de memoria y el chipset PCI. Además incorpora el conjunto de instrucciones MMX. Con esto se consigue que los gráficos se procesen a la velocidad de reloj del procesador. Además, no es necesaria caché L2 ni VRAM (memoria de vídeo) porque el controlador de memoria dentro del chip permite acceso directo a la memoria RAM, que sirve como memoria de vídeo. 22 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 MICROPROCESADORES x86 Figura 10. 1.600.000 DESARROLLO DE LA FAMILIA “x86" Número de transistores 486DX2 MIPS 120 32 80486 32 80386 4 32 275.000 80286 1 16 120.000 80186 16 80188 8086 27.000 0.2 16/8 16 8088 8085 8080 4.000 16/8 8 8 74 76 78 82 85 89 92 Año El 80286 sirve de puente entre el 8086 y los microprocesadores avanzados que vendrían después. Los recursos técnicos introducidos en el 8086 y que sirvieron para construir el 80286 son cruciales para concebir e implementar los microprocesadores de 32 y 64 bits. Las características más sobresalientes del 80286 son: 1. MEMORIA VIRTUAL 2. DOS MODOS DE TRABAJO: - Modo real - Modo protegido virtuales 3. PROCESADOR NUMÉRICO DE 80 BITS (80287) con direcciones FAMILIA HARDWARE DEL 286. 80286 CPU 82284 Generador de reloj 82288 Controlador del bus 82289 Arbitro del bus 80287 Coprocesador matemático 82258 Controlador de DMA 8207 Controlador RAM dinámica 8206 Unidad de detección/corrección error 286/10 Tarjeta microcontroladora 23 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 ARQUITECTURA DEL 8086. Intel introdujo por primera vez en el 8086 el funcionamiento segmentado ( segmentación de la memoria ), que consiste en dividir un proceso en partes y construir unidades para el tratamiento de cada parte, permitiendo trabajar simultáneamente a dichas unidades y dando lugar a una aceleración en el tiempo total de realización. Se trata de un paralelismo implícito, similar al que se usa en el acabado de un automóvil en una cadena de fabricación en serie. Internamente el 8086 está formado por dos unidades o procesadores independientes: 1. La unidad de ejecución: encargada de ejecutar instrucciones procedentes de la cola de instrucciones. 2. La unidad de interfaz con el bus: realiza todas las transferencias con el bus del sistema. Se encarga de direccionar la memoria y las E/S para soportar las transferencias de información. Estructura interna simplificada del 8086. UNIDAD DE EJECUCIÓN UNIDAD DE INTERFAZ DEL BUS REGIST ROS DE SEGMENTOS BANCO REGISTROS GENERALES PUNTERO DE INSTRUCCIONES GENERACIÓN DE DIRECCIO NES OPERANDOS S E Ñ A LI Z A D OR E S BUS DEL SIST EMA COL A DE IN S T R U C C IO N E S ALU Figura 11. Arquitectura segmentada del 8086. Las dos Unidades que le conforman son independientes y trabajan en paralelo. LOS REGISTROS Se dividen en 4 grupos: 1. De Datos ( AX, BX, CX, DX) 2. De Punteros e índice ( SP, BP, SI y DI ) 3. Registros de segmento y puntero de instrucciones (CS, DS, SS, ES e IP ) 4. De Estado (Señalizadores). 24 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 Registros de datos AX: Acumulador → está dedicado a las operaciones BX: Base → se usa como puntero base en el direccionamiento de memoria CX: Controlador → contador de interacciones DX: Datos → se usa en operaciones y en direccionamiento para E/S Registros puntero e índice SP: Puntero de pila BP: Base en el direccionamiento de la pila SI: Índice fuente en la segmentación DI: Índice destino en la segmentación Registro de segmento y puntero de instrucciones El 8086 utiliza el método de la segmentación para manejar la memoria. Dicho método consiste en asignar varios trozos de tamaño variable de la memoria ( segmentos ) a cada programa; cada trozo o segmento guarda un tipo de información concreta. Así existe un segmento de código que guarda los códigos OP de las instrucciones, otro segmento de datos, que guarda los datos, otro segmento de pila, que implementa la zona de memoria que actúa como pila en saltos a subrutinas, interrupciones, etc. Cada programa o procedimiento dispone de varios segmentos, cada uno de los cuales puede alcanzar un máximo de 64kb de memoria. Figura 12. 00000 H MEMORIA CS SEGMENTO DE CÓDIGO DS Bases de los 4 segmentos SEGMENTO DE DATOS 1 MB SS SEGMENTO DE PILA ES FFFFF H SEGMENTO EXTRA MEMORIA SEGMENTADA DEL 8086 La base de un segmento se obtiene a partir del contenido de uno de los 4 registros de la CPU, llamados registros de segmento. Las memorias que actualmente se utilizan en los sistemas digitales son circuitos integrados LSI. 25 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 La memoria de Lectura/Escritura Introducción Se trata de un tipo de memoria, que a diferencia de la ROM, su información puede ser leída o escrita tantas veces como se desee, y además, su contenido se altera en caso de faltar la alimentación de la misma. Se dice que son “volátiles”. Se las conoce generalmente con el nombre de memorias RAM, Random Access Memory (memoria de acceso aleatorio). Esto es, se puede acceder a cualquier posición, en cualquier momento, sin seguir ningún orden en particular. Memoria RAM estática. En síntesis, la estructura interna de filas y columnas es similar a las ROM. La diferencia se encuentra en la construcción de las celdas que, si bien aquellas consistían en la conexión o desconexión de un diodo, en estas la estructura se basa en una báscula electrónica o flip-flop del tipo D, capaz de almacenar un bit 1 ó 0 temporalmente. Por definición una memoria RAM es una memoria de lectura/escritura, ya que una báscula puede ser leída o escrita tantas veces como sea necesario. También es volátil ya que si a un flip-flop, al cual se le ha cargado una información, se le interrumpe la tensión de alimentación, al restaurarla, puede quedar aleatoriamente a1 ó 0. Si tenemos en consideración que un chip contiene miles de esos flip-flop, es lógico pensar que es imposible que todos ellos se restauren con lo que tenían originalmente. C7 C6 C5 C4 C3 C2 C1 C0 D Q CLK 0 LÍNEAS DE DIRECCIÓN 1 2 3 R /W PUERTA DE ENTRADA / SALIDA LÍNEAS DE CS DATOS Figura13. En la figura se muestra la arquitectura interna de una memoria RAM estática. 26 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 Direccionamiento A través del bus de direcciones, la CPU envía la posición de memoria a la que se desea acceder. Esta es decodificada internamente para seleccionar a una de las múltiples filas. Esto implica la activación de los flip-flop que la componen, de forma que sólo ellos sean capaces de reaccionar. Seguidamente, el procesador envía la orden de lectura/escritura (R/W) a la puerta de entrada/salida de manera que la información entra desde el exterior hacia la posición seleccionada (Write, nivel “0”) o desde ésta al exterior (Read, nivel “1”). En ambos casos, la información estará disponible siempre que la señal CS (Chip Select) esté activa (normalmente a “0”). El número de posiciones de que dispone un determinado modelo se obtiene, al igual que en las ROM, elevando 2 al número de líneas de direcciones que tenga el chip. En cuanto al número de columnas o bits por fila, hay que señalar que, si bien en las ROM era de 8, en las RAM estáticas puede ser de 1, 4 u 8. Memoria RAM dinámica. Se trata de otra forma de almacenamiento de información binaria que puede ser modificada en cualquier momento y, desde luego, estamos ante una memoria volátil al igual que la anterior. En este caso, en lugar de emplearse un flip-flop como célula básica de almacenamiento, se emplea un condensador, conectado al terminal de surtidor de un FET, que se carga (nivel “1”) o se descarga (nivel “0”) según convenga. En la siguiente figura (fig.14) se muestra la configuración interna de este tipo de memoria RAM. Es necesario señalar, independientemente del número de filas que contenga, que por lo general sólo se manipula un bit de información por cada una de estas filas. Cn C2 C1 C0 RAS Di LINEA DE DATOS LINEAS DE DIRECCION WE RAS DECODIFICADOR DE COLUMNAS CAS Di - Do CAS DATO Figura 14. 27 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 Internamente, existen dos decodificadores, uno para las filas y otro para las columnas. Ambos comparten las mismas líneas de direcciones del chip. En un primer lugar, por ellas debe darse, junto con la señal RAS activa a “0” (selección de filas), el número de la fila a la que se desea acceder. Tras un corto intervalo de tiempo (entre 20 y 100 ns), se proporciona, por las mismas líneas de direcciones y junto con la señal CAS activa a “0” (selección de columna), el número de columna a la que se desea acceder. Ambas coordenadas, filas-columnas, seleccionan una y sólo una de las múltiples células. Al mismo tiempo, la señal WE = 0, indica si se trata de leer o escribir sobre ella. Este tipo de dispositivos suelen disponer de dos patillas, una de entrada de bit (Di) para el caso de escritura y otra de salida (Do) para el caso de lectura. En los montajes prácticos, ambas patillas suelen estar unidas. No existe señal CS como en dispositivos anteriores, para dar por válido un acceso, es necesaria la secuencia completa de RAS – CAS junto con WE. Dado que para acceder a un único bit de información, ya sea en lectura o en escritura, es necesario realizar un doble acceso, primero para seleccionar la fila y luego la columna, el hardware utilizado entre el bus de direcciones de la CPU y las propias líneas de dirección del micro, está basado en un multiplexor que envía primero la dirección de filas y luego la de columnas más un circuito retardador encargado de generar la conmutación RAS / CAS. Capacidad de una memoria Las memorias se caracterizan fundamentalmente por el número de posiciones que la constituyen. Es necesario, en primer lugar, distinguir entre capacidad total y número total de posiciones disponibles. Se llama capacidad total al número de bits que una memoria puede almacenar. Por consiguiente, siempre será mayor la capacidad total que el número de posiciones, salvo en el caso de que el número de bits por posición sea uno. En estas circunstancias, ambos conceptos son coincidentes. En general, si llamamos n al número de bits de cada posición y m al número de posiciones, la cantidad total de bits, a la que denominaremos N, será: N=n·m La operación de selección de una determinada posición de memoria se denomina direccionamiento. El bus de direcciones o, dicho de otra manera, la cantidad de líneas necesarias para direccionar las m posiciones de una memoria será n, de tal forma que siempre debe cumplirse la siguiente igualdad: n1 2 =m Las memorias son conocidas por el número de posiciones que las forman y por la longitud del dato o palabra que es capaz de almacenar en cada posición de memoria. Así la expresión 32 x 4 referida a una memoria indica que es un dispositivo de 32 posiciones (m = 32) cuya longitud de palabra es de 4 bits (n = 4). La cantidad de posiciones de las memorias de gran capacidad se mide en Ks. 1K equivale a 1024 posiciones, y para direccionar todas ellas se necesitan diez líneas o variables binarias, ya que: 10 2 = 1024 28 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 La letra K como prefijo de la capacidad de una memoria tiene el mismo significado que la K utilizada como medida de otras magnitudes físicas; se ha 10 escogido el valor 1024 = 2 porque es la potencia de 2 que más se aproxima a 1000. Cuando la longitud de la palabra es de 8 bits, es decir, un byte, la capacidad se mide en kilobytes. La capacidad expresada en Ks de una memoria que utiliza n1 variables binarias para direccionar todas sus posiciones será: n1 -10 2 De manera que una memoria con n1 = 14 entradas de selección tendrá una capacidad de 16K posiciones. Por último, volviendo al concepto de capacidad total, calcularemos el número de bits de una memoria de 16 kilobytes, es decir, 16 x 8, expresado de manera más general: N = 16 x 1.024 x 8 = 131.072 bits. Configuración externa de una Memoria A continuación se muestra simbólicamente una memoria RAM con sus correspondientes entradas/salidas de direcciones, datos y control. La diferencia entre esta y una ROM reside en la ausencia, en el caso de esta última, de la entrada de control R/W que permite leer o escribir en función del nivel lógico aplicado. Memoria Direcciones n1 RAM E/S de datos n R/W CS Control Figura 15. Este dispositivo tiene comunes las entradas y las salidas de datos. El valor de la letra n depende de la longitud de las palabras o datos que pueden escribirse o leerse en cada posición. Existen memorias con entradas y salidas independientes. Las líneas de selección para el direccionamiento de cada uno de los registros están representadas por n . Su valor depende del número de posiciones que constituyen la memoria. 29 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 Las entradas de control de este dispositivo son CS (Chip Select) y la ya mencionada R/W (Read/Write). A0 -A9 10 RAM 1Kx8 CS R/W 8 RAM 1Kx 8 CS R/W RAM 1Kx8 8 CS R/W 8 D0 - D7 8 R/W A 10 A0 - A12: Líneas de dirección D0 - D7: Líneas de datos 0 A 11 A 12 1 E: entrada de habilitación E 7 Unidad de memoria RAM formada por ocho pastillas de 1K x 8 cada una. Figura 16. En la fig.16 se muestra el esquema de conexión de una unidad de memoria de lectura/escritura, constituida por ocho chips o pastillas de 1K x 8. El número total de posiciones o palabras será de 8K, es decir, de 8.192 bytes. La selección, como ya hemos señalado, se realiza mediante las líneas de dirección del sistema. El número total de líneas constituyen el bus de direcciones y su amplitud depende fundamentalmente del tipo de microprocesador que se utilice. Un sistema cuyo bus de direcciones sea de 16 líneas tendrá capacidad para seleccionar 64K, o sea, 65.536 palabras. En el esquema indicado se utiliza un decodificador de tres entradas y ocho salidas. Además dispone de una entrada E (enable) de habilitación. El número total de líneas de dirección es de trece ( A0 – A12). Las diez primeras se utilizan para seleccionar cada una de las 1.024 palabras de cada pastilla y las tres restantes para seleccionar cada uno de los ocho circuitos. Como se puede comprobar, las salidas de todos los chips están unidas al mismo bus de datos. Esto es posible gracias a las propiedades de los buffer triestado que forman parte de la arquitectura interna de los circuitos de memoria. CIRCUITO 2114 A DE INTEL El circuito 2114 A fabricado por la compañía INTEL es una memoria de acceso aleatorio de lectura/escritura organizada en 1.024 palabras de 4bits cada una. Está construida en HMOS, que es una variante, con altas prestaciones, de la tecnología MOS. Los terminales de entrada y salida son comunes. 30 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 En la figura 17 se muestra el diagrama de conexión y el símbolo lógico. A6 A5 A4 A3 A0 A1 A2 CS GND 1 2 3 4 5 6 7 8 9 2114 A 18 17 16 15 14 13 12 11 10 Vcc A7 A8 A9 I/O 1 I/O 2 I/O 3 I/O 4 WE A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 WE I/O 1 I/O 2 I/O 3 I/O 4 CS Figura 17. Las entradas de control se denominan: WE (Write Enable) y CS (Chip Select). El circuito queda habilitado para escribir en él, cuando se aplica un nivel lógico cero en la patilla WE. Con el mismo nivel, aplicado a la entrada CS, el circuito queda seleccionado de entre todos los que componen el sistema de memoria. Refresco de Memoria Al margen de lo estudiado hasta ahora en cuanto a la configuración y modo de direccionamiento de este tipo de memorias, recordemos que se tratan de células elementales basadas en un condensador, que se carga o no dependiendo de la información que vaya a almacenar. En la práctica, ningún condensador es perfecto y todos, con el tiempo tienden a perder su contenido. Si se dejara que esto ocurriese en las memorias dinámicas, estas perderían continuamente su información. Se hace precisa una circuitería auxiliar que cada cierto tiempo produzca lo que se llama un ciclo de refresco, consistente en recargar todos los condensadores. Dicho ciclo debe producirse cada 4mS aproximadamente. Consiste simplemente, en pasar por todas las filas del dispositivo en modo de lectura. Esto es suficiente para refrescar, a su vez, todas las columnas. Evidentemente, la CPU no debe hacer uso de la memoria durante un ciclo de refresco ni emplear por tanto los buses. Estos serán controlados por esa circuitería auxiliar basado fundamentalmente en un contador. Cuando se recibe una orden de refresco, que puede venir dada periódicamente por un temporizador, la CPU se desconecta de los buses y los toma, a cambio, un contador. Éste, partiendo de 0, comienza una cuenta, descendente, que se va aplicando a las líneas de direcciones del banco de memoria a refrescar. Al mismo tiempo, se aplica la 31 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 señal RAS. En principio, y según el fabricante, esto es suficiente ya que se refrescan también las columnas de cada fila. En la práctica, cuando la CPU realiza un ciclo de lectura/escritura se produce un refresco espontáneo de la fila - columna direccionada. Siguiendo con el ejemplo, cuando el contador vuelva a pasar por 0, se supone finalizado el ciclo de refresco, por lo que el contador se desconecta de los buses cogiéndolos nuevamente la CPU. La secuencia se debe ir repitiendo constantemente cada cierto tiempo. Ciclo de Memoria Ciclo de lectura: comienza cuando se aplica una dirección de filas acompañada de una transición de señal RAS, pasando de “1” a “0”. A continuación, se aplica una dirección de columna acompañada de la señal CAS que también pasa de”1” a “0”. Tras un tiempo de acceso que depende del tipo de chip, aparece el bit de la célula seleccionada por la patilla Do. Este es estable mientras CAS se mantenga activada. La entrada WE debe permanecer en todo momento inactiva “1”. Cuando CAS pasa a “1” (inactiva), se da por terminado el ciclo y la salida queda en alta impedancia. Ciclo de escritura: es similar al de lectura con la diferencia de que la señal WE debe permanecer activa “0” mientras lo esté CAS. Ciclo de refresco: consiste en ir seleccionando y recorriendo todas las filas cada cierto tiempo (unos 4ms), junto con la señal RAS activa (“0”). Cuando se selecciona una, origina el refresco de todas las columnas que la componen. Es decir, no hace falta recorrer todas las células del chip. En cualquier caso, cualquier acceso normal de lectura/escritura sobre cualquier celda, origina automáticamente su refresco. System memory Extended Memory 1024K 15FFFFh Reserved Area for Display Memory, and ROM BIOS 640K Configuración de la memoria Memoria convencional: memoria base. 7FFFFh 8MB 0K Base Memory used by DOS and Application Programs 9FFFFh 00000h Se conoce como memoria convencional la memoria RAM situada entre las direcciones 00000h y 9FFFF h., es decir, los 640k primeros del mapa de memoria. El sistema operativo MS-DOS, en sus diferentes versiones, sólo es capaz de “ver” y gestionar hasta 1MB, límite que impone el microprocesador 8088. Dentro de esta área, se alojan, en primer lugar los vectores de interrupción empleados por el BIOS y el sistema operativo. Estos vectores contienen las direcciones de inicio de diferentes rutinas y tratamientos. Físicamente esto se encuentra en el primer K de memoria, sin ellos, es decir, si fallaran los chips del banco 0, el sistema ni tan siquiera arrancaría. Por encima de los vectores, el BIOS y el DOS van guardando datos y variables temporales. Más arriba queda instalado el núcleo del DOS, en el momento que éste se carga al encender la máquina. En el intervalo de 1024 y 1088K, (memoria extendida). Finalmente, se alojan los datos y programas de aplicación del propio usuario. La longitud de éstos dependerá de la cantidad total de memoria RAM que haya instalada. 32 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 Memoria reservada: memoria superior. En términos generales se trata del espacio comprendido entre los 640K y el MB máximo que puede gestionar el micro 8088, es decir, desde la posición A0000h. hasta la FFFFFh. Memoria extendida (XMS) La memoria convencional y reservada está condicionada por las características propias del procesador 8088, que sólo puede gobernar hasta 1 MB de memoria en total. De la misma manera, la memoria extendida tiene su origen en los procesadores que se emplean en la construcción de las máquinas AT: el 80286 y el 80386. El 80286, dispone de un bus de direcciones de 24 líneas que le hacen capaz de gobernar 16MB, (224 = 16.777.216), y el 80386 posee otro de 32 líneas, con lo que su capacidad se sitúa en los 4GB, (232 = 4.294.967.296), 4096MB. Las máquinas con este tipo de procesadores utilizan los primeros 640K como memoria convencional y los 384K siguientes como reservada, según lo visto anteriormente. La memoria extendida es la que está situada por encima del primer mega. Es propia de los procesadores 80286 y 80386 y, por tanto un XT no podrá tener este tipo de memoria. Este tipo de memoria, bajo DOS, suele ser utilizada como “Disco Virtual” o “Disco RAM”. Otros sistemas operativos (OS/2, UNIX, etc.) la pueden emplear en otras aplicaciones. Memoria expandida Fig. 18 4GB MEMORIA 16MB EXTENDIDA BIOS 1MB MEMORIA RESERVADA 640KB MEMORIA Se trata de un pequeño “truco” MEMORIA OCUPADA CONVENCIONAL POR EL SIST. OP. que se propuso en su día por O MEMORIA BASE varias compañías fabricantes 8088 80286 80386 de software, (Lotus, Intel, Microsoft, LIM y otras) para conseguir que los programas en RAM bajo DOS pudieran superar el límite de los 640K. Recibe el nombre de EMS (Expanded Memory Specification). Se trata de una memoria RAM totalmente independiente, que según las especificaciones EMS v4.0 puede llegar hasta los 32MB. La memoria expandida se encuentra localizada dentro de la memoria superior. Desde el DOS, con solo teclear un comando podemos llegar a conocer la configuración exacta que soporta un ordenador cualquiera: si desde el directorio raíz tecleamos Mem (c:\>mem), podemos observar algo parecido a lo que se muestra a continuación: 33 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 (C)Copyright Microsoft Corp. 1981-1995. C:\WINDOWS>cd.. C:\>mem Tipo de memoria Total Usada Libre ------------------------ ---------- ---------- ----------Convencional 640K 108K 532K Superior 0K 0K 0K Reservada 384K 384K 0K Extendida(XMS) 31.744K 216K 31.528K ------------------------ ----------- ---------- ----------Memoria total 32.768K 708K 32.060K Total por debajo 640K 108K Expandida total (EMS) Expandida libre (EMS) 532K 31M (32.997.376 bytes) 16M (16.777.216 bytes) Mayor tamaño de programa ejecutable: 532K (544.880 bytes) Mayor bloque de memoria superior libre: 0K (0 bytes) MS-DOS es un programa residente en el área de memoria alta. C:\> Esta memoria puede emplearse para contener datos y programas. Mediante un software o hardware adecuado, se consigue que la información de esta memoria expandida pueda ser trasladada a áreas de la memoria convencional, 16MB ó 4GB cuando sea necesario, en bloques de 16K. MEMORIA EXTENDIDA El funcionamiento consiste 1024K en detectar bloques de la ÁREA DE ROM (BIOS, BASIC, ETC.) memoria convencional que, 960K MEMORIA 192K DE RAM en un momento dado no se PARA INTERCAMBIO (12 pág. De 16 K) emplean, e intercambiarlos 768K EXPANDIDA por bloques de la ÁREA DE VIDEO - RAM extendida, que si se usan. (2048 páginas de 640K De esta manera se 16K máximo) 384K de RAM consigue engañar al DOS, PARA INTERCAMBIO (24 pág. De 16K) ya que sólo ve la SOLO CON HARDWARE ESPECIAL MEMORIA convencional pero, en ésta BASE 256K dispone de información que 256K de MEMORIA RAM había en la memoria CONVENCIONAL expandida gracias al cambio de banco que se ha producido. Cuando se necesita otra información, se origina un nuevo cambio de bloque, y así sucesivamente. 32MB 0K 34 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 Aparentemente, el programa, y los datos que está manipulando el DOS, puede ser muy superior a la memoria que él reconoce. Este mecanismo también es conocido con el nombre de Memoria Virtual. En la figura 19 se representan los mapas de memoria correspondientes a las especificaciones EMS v4.0 de Octubre de 1987. LA MEMORIA CACHÉ Existen cachés de muy diversas formas y tamaños, pero todas se diseñan con una única finalidad: acelerar los accesos de la CPU a los datos que se utilizan con más frecuencia. La secuencia es la siguiente: mientras la CPU accede a los datos contenidos en la RAM, el controlador de caché copia los datos y, según su algoritmo de control, también las instrucciones consecutivas o relacionadas. Como resultado, se consigue que la próxima vez que la CPU necesite la información, ésta se encuentre en el caché. Además, debido a que el caché externo es más rápido que la RAM, el acceso de la CPU a los datos se realizará a mayor velocidad. Existen numerosos tipos de arquitecturas de caché y otros cuantos diseños de escritura en caché. La arquitectura de caché determina el método que ha de seguirse para organizar y localizar los datos de la RAM en el interior del caché. Los tres diseños más frecuentes son el de mapeado directo, el de asociación de grupos y el de asociación completa. El diseño de la escritura en caché establece cuándo y con qué frecuencia escribe el caché en la memoria principal datos que han sido alterados por la CPU. Los diseños principales son sólo lectura y lectura/escritura (Write-Back). ARQUITECTURAS Con el caché de mapa directo, una posición específica en el interior del caché corresponde a varias posiciones determinadas dentro de la memoria principal. Esto significa que cuando la CPU requiere unos determinados datos, el caché tiene que desplazarse a dicha posición dentro de sí mismo para obtener la información, de forma que se ahorra tiempo. El inconveniente de este tipo de caché es que como varios bloques de datos dentro de la RAM corresponden a la misma posición en el caché, si un programa accede a dichos datos, el caché estará constantemente en funcionamiento llamando a la memoria principal. De este modo no se obtiene un beneficio global. Con el caché totalmente asociativo, se pueden situar bloques de datos de la memoria principal en cualquier bloque libre dentro del caché. La ventaja es que la información a la que se ha accedido más recientemente suele estar presente en el caché, pero el inconveniente consiste en que la búsqueda es lenta, ya que el caché debe iniciar una búsqueda indexada para localizar los datos. En un caché asociativo por grupos se combina elementos de las dos arquitecturas anteriores: se divide en dos, cuatro u ocho grupos, que tienen diversas posiciones, cada una de las cuales alberga un bloque de datos. Cada bloque dentro de la memoria principal puede estar en cualquiera de los grupos, pero sólo puede estar en una posición dentro de un grupo. Por ejemplo, un caché asociativo en grupos de dos vías tiene dos grupos, por lo que tiene dos posiciones posibles en las que un determinado bloque de datos puede residir. De este modo el tiempo de búsqueda se reduce, y es menos probable que los bits de datos utilizados con más frecuencia se sobrescriban. El inconveniente es que estos cachés son más difíciles de desarrollar. 35 Estructura y Tecnología de Computadores Miguel Angel©1999-2002 LECTURA FRENTE A ESCRITURA La CPU se encarga de actualizar con frecuencia la información de un caché. Los cachés pasan estos cambios a la memoria principal mediante uno de dos métodos de escritura principales: lectura o lectura/escritura. En un caché de sólo lectura, cada vez que la CPU devuelve un bit de datos cambiado al caché, el caché actualizará dichos datos en sí mismo y en la memoria principal. En un caché de lectura/escritura, el caché almacena el bloque de datos cambiado en sí mismo pero lo actualizará en la memoria principal sólo en determinadas circunstancias: cuando al bloque de datos completo deba ser sobrescrito porque un bloque más reciente deba reemplazarlo, cuando otra parte del sistema, como el dispositivo de bus master, trate de acceder a dicho bloque de datos desde la memoria principal o, en ocasiones, cuando el algoritmo controlador determine que los datos han estado esperando demasiado tiempo para ser actualizados. Caché de mapa directo Memoria principal 110 Memoria principal Dos o más bloques pueden asignarse a la posición específica del caché, pero dicha posición sólo puede albergar un bloque cada vez. El caché tiene que desplazarse a una única posición para buscar la información ? 110 La CPU busca el bloque de datos 110. CPU Caché totalmente asociativo Memoria principal Cada bloque de datos puede almacenarse en una o dos posiciones del caché. 110 Caché externo (L2) Caché externo (L2) 110 Caché asociativa en grupos de dos vías Cualquier bloque puede almacenarse en cualquier posición dentro del caché. 110 Caché externo (L2) 110 El caché debe buscar una posición en cada grupo para localizar la información. ? 110 La CPU busca el bloque de datos 110. 110 ? 110 El caché debe buscar en todos sus bloques para localizar un bloque de datos determinado. La CPU busca el bloque de datos 110. CPU CPU Figura 10. 36