Diseño de Circuitos Integrados Analógicos

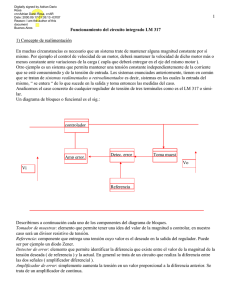

Anuncio

Diseño de Circuitos Integrados Analógicos

(Full Custom)

Estrategia de diseño TOP-DOWN

División del sistema en bloques más simples hasta llegar a los bloques circuitales básicos

• (divide y vencerás)

Niveles de diseño diferenciados:

Nivel

Componentes del diseño

Sistema

Cajas negras

Esquemático Dispositivos electrónicos

Layout

Elementos geométricos

Nivel de SISTEMA: Diagrama de bloques

PGA

ADC

Ant

LNA

PLL

DSP

90º

PGA

ADC

Nivel de Esquemáticos

Nivel de Layout

Diseño JERARQUICO

A un esquemático se puede asociar un SIMBOLO (caja negra)

Ese símbolo puede formar parte de otros esquemas

Así, los esquemas de sistemas complejos contienen símbolos de sus bloques funcionales, que

a su vez contienen símbolos de unidades más simples, hasta llegar a esquemas con sólo los

dispositivos básicos (celdas primitivas).

JERARQUIA de Diseño. Ejemplo

Receptor

LNA

Filtro BP

Mixer

PLL

PGA

ADC

Comparador

Amplificador Operacional

Núcleo

Transistor

Control Modo Común

Condensador

Condensador

Interruptor

Interruptor

Polarización

Generación de reloj

Transistor

Simbolo del núcleo del A. O.

parámetros de los

bloques funcionales

no

Diseño de los

circuitos de los

bloques funcionales

Nivel de LAYOUT

Dibujo del layout

Rediseño

Rediseño

Rediseño

Obtención de

Nivel de ESQUEMATICO

Rediseño

Rediseño

Nivel de SISTEMA

de los bloques

funcionales

SIMULACION

(SPICE)

¿Parámetros

razonables?

EXTRACCION

si

SIMULACION

(nivel de sistema)

no

¿Cumple

especificaciones?

Mal

LVS

si

no

¿Cumple

especificaciones?

si

si

Bien

SIMULACION

(SPICE)

¿imposible o

muy costoso?

no

no

¿Cumple

especificaciones?

si

Flujo de Diseño TOP−DOWN

FIN

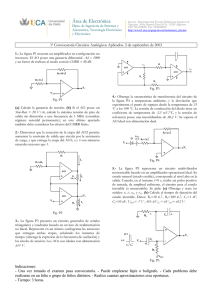

Ejemplo de diseño:

Convertidor Analógico / Digital

(Diseño a nivel de sistema)

Tipo: Convertidor algorítmico

Resolución: Variable (12 bits nominal)

Frecuencia máxima de reloj: 1 MHz

Diagrama de bloques

INIT

Comp.

Vin

+Vref

Vres

Bitout

S&H

Vin

x2

Vres

+

−

Vdac

1 +Vref

0 −Vref

−Vref

−Vref

+Vref

Implementación SC. (sólo cálculo de Vres)

φ1

C2

φ2

φ2

C2

+

φ1

Vin

Vres

C1

φ1

Vdac

+

φ1

C2

+

C1

Vin

C1

φ2

+Vref

Q

+

Vdac

−Vref

Bitout

Vres = 2 Vin − Vdac

Q = (Vdac − Vin)C1

Vres = Vin − Q/C2

C1

Vres = Vin 1 + C

2

C1

− VDAC C

2

Vres

Implementación SC incluyendo S&H

φ1

φ2

C3

φ2

0

φ1

Vin 1

C1

φ2

+Vref

−Vref

1

φ1

φ2

φ1

INIT

φ2

C2

φ1

Vdac

0

Bitout

Vres

INIT

Bitout

MSB

N−1

N−2

N−3

Simulación a nivel de sistema

Efectos a considerar

Mismatch entre C1 y C2

Ganancia finita en el operacional

Voltajes de offset en operacional y comparador

Ruido

• Muestreo: Vn2 = KT /C

• Equivalente en la entrada del A. O.

Simulación a nivel de sistema: Código C

int adc1(float vin,int nbit)

{

int i,o; float vdac,vres,q;

vres=vin;

for (i=o=0; i<nbit;i++) {

o< <=1;

if (vres>OFFSET1) {

vdac=VREF; o++;

} else vdac=-VREF;

q=(vdac-vres+alea(1.4142*noisec1))*C1;

vres=(vres - q/C2 + OFFSETA*(1.+C1/C2)+alea(noiseamp))/

(1.0+1.0/GAIN+1.0/GAIN*C1/C2);

}

return o;

}

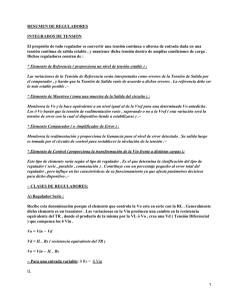

Simulación a nivel de sistema: Offset en el comparador

12

0.03

10

0.02

Input Voltage

DNL (LSB)

8

6

4

2

0

-0.01

-0.02

0

-2

0.01

0

512

1024

1536

2048

2560

3072

3584

4096

-0.03

2000

Code

2016

2032

2048

Code

(VOF F = 10mV )

2064

2080

2096

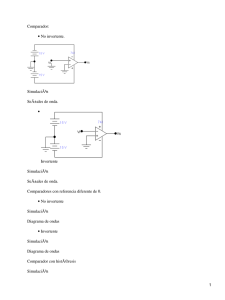

Rediseño: Arquitectura de 1.5 bits

φ2

B1

C3

C2

φ2

0

B1

φ1

B0 ciclo2

B1

φ2

φ1

Vin 1

Vres

+Vref

B0 ciclo 1

B0 ciclo 3

B1

Vres

B0 ciclo 4

C1

φ1

Vin

φ2

φ1

INIT

B1

B1

Vdac

B1

B0

T2

00

−Vref

0

−Vref/4

Th − Bin

1

−Vref 0

2

+Vref

B0 ciclo n−1

−Vref

+Vref/4

T1

B0 ciclo n−2

01

−Vref/4 +Vref/4

10

Dn

+Vref

D2 D1

Resultado de la conversión

D0

Corrección digital del offset:

Vres

+Vref

Vref

Vin

Voff

−Vref

00

−Vref

01

−Vref/4 +Vref/4

10

+Vref

Simulación a nivel de sistema. Código en C

int adc15(float vin,int nbit)

{

int i,o;

float vdac,vres,q;

vres=vin;

for (i=o=0; i<nbit-1;i++) {

o< <=1;

if (vres>VREF/4.+OFFSET1) {

vdac=VREF;

o+=2;

} else if (vres>-VREF/4.+OFFSET2){

vdac=0;

o+=1;

} else vdac=-VREF;

q=(vdac-vres+alea(1.4142*noisec1))*C1;

vres=(vres - q/C2 + OFFSETA*(1.+C1/C2)+alea(noiseamp))/

(1.0+1.0/GAIN+1.0/GAIN*C1/C2);

}

return o;

}

Simulación a nivel de sistema: Offset Operacional

128

Code

96

64

32

0

-1

-0.99

-0.98

Input voltage

(VOF F = 10mV )

-0.97

-0.96

Simulación a nivel de sistema: Ganancia finita A. O.

0.3

INL (LSB)

0.2

0.1

0

-0.1

-0.2

0

512

1024

1536

2048

Code

(GAIN=10000)

2560

3072

3584

4096

Simulación a nivel de sistema: Mismatch entre C1 y C2

0.6

0.4

INL (LSB)

0.2

0

-0.2

-0.4

-0.6

-0.8

-1

512

1024

1536

2048

Code

2560

(C1=1.001 C2)

3072

3584

4096

Simulación a nivel de sistema: Ruido

4096

0

-20

-40

Amplitud (dB)

Dato

3072

2048

-60

-80

-100

1024

-120

0

0

50

100

150

Muestra #

200

250

300

-140

0

50

100

150

200

250

300

350

Frecuencia (kHz)

√

(C1 = C2 = 0,4pF , nin(AO) = 10nV / Hz) ->SNDR=72.5 dB

400

450

500

Simulación a nivel de sistema: Error en voltaje de referencia

6

5

DNL (LSB)

4

3

2

1

0

-1

0

512

1024

1536

2048

Code

2560

(∆Vref = 10mV )

3072

3584

4096

Rediseño: Versión completamente diferencial

INIT

/INIT

Vi+

φ2

C2

DAC 1.5 bits diferencial

φ1

φ1

+Vref/4

−Vref/4

φ2

C3

Vref+

Vo+

S0

C1

Vref+

Vref−

φ1

φ2

φ2

S0

φ1

A. O.

φ1

φ2

Vi−

/INIT

φ2

φ2

Vref/4

T2

B1

Vref/4

T1

S2

Vi−

φ2

C2

Vi+

Vo−

B1

φ1

φ1

INIT

Vref−

C1

B1 B0

φ1

S1

S2

DAC 1.5 bits

ADC 1.5 bits

ADC 1.5 bits diferencial

S2

C3

B0

S1

S0

B0

Obtención de parámetros de los bloques funcionales

Algunos ya conocidos de los resultados de las simulaciones:

Condensadores: 0.4 pF (ruido)

Ganancia A. O. >10000

Otros se obtienen de datos de la tecnología CMOS:

Matching condensadores de doble polisilicio mejor 1/1000 para C=0.4 pF

Obtención de parámetros: Interruptores

Los condensadores se cargan / descargan a través de la resistencia r ON de los interruptores.

En medio ciclo de reloj se han de descargar hasta por lo menos V LSB /2 = Vref /4096 esto da:

T /2

rON ≤ C ln(4096) = 150 KΩ

Cuando se muestrea la entrada se puede tener distorsión debido a la variación de la resistencia

del interruptor, ∆R, con el voltaje. La peor distorsión, ∆V es:

∆V = ω

∆R

C

r

N yq

ON rON

V ref

1 y ∆R = 0,5 , con ω

si V∆V ≤ 4096

N yq = 2π × 45 KHz obtenemos rON ≤ 4300 Ω

rON

ref

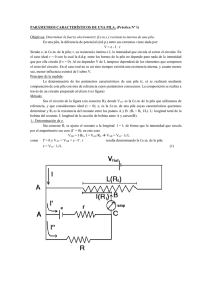

Obtención de parámetros: A. O.

Slew-Rate y Producto ganancia x Ancho de banda.

φ2

Vres

SR

Tslew−rate

Tsettling

V

Tslew−rate = T /4 ->SR = Tref

= 8 V /µs

/4

v(t) = V0 exp(−BW · t) , v(T /4) = V0/4096 ->BW = 5,3 M Hz

GBW = 2 × BW = 10,6 M Hz