Fundamentos de Computadores

Anuncio

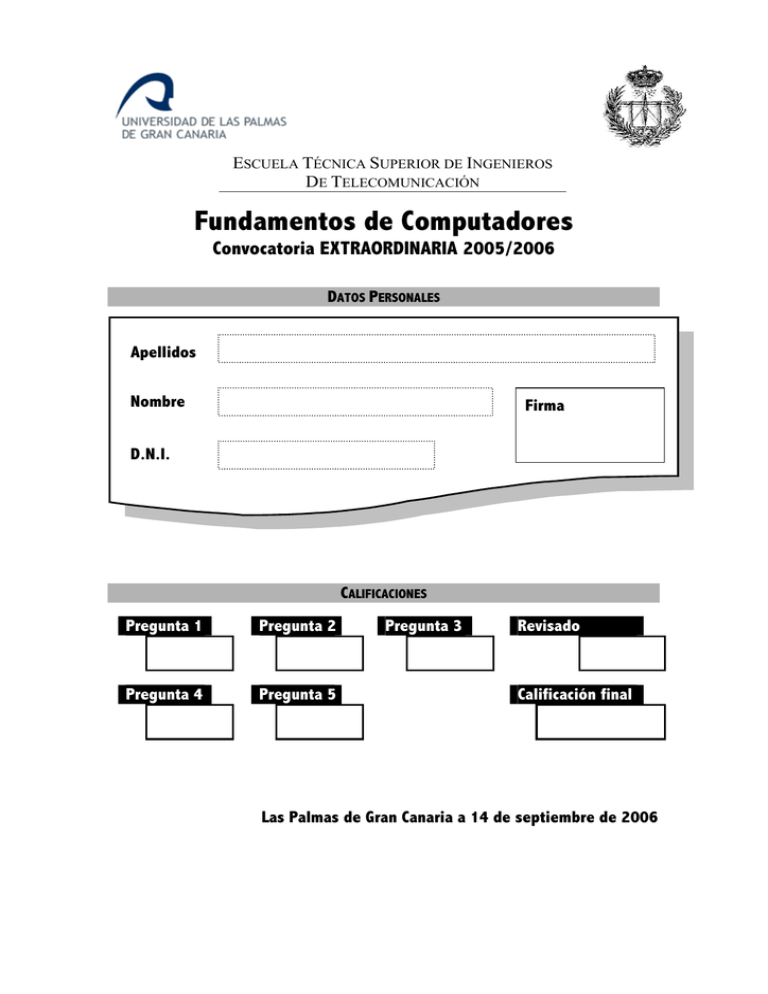

ESCUELA TÉCNICA SUPERIOR DE INGENIEROS DE TELECOMUNICACIÓN Fundamentos de Computadores Convocatoria EXTRAORDINARIA 2005/2006 DATOS PERSONALES Apellidos Nombre Firma D.N.I. CALIFICACIONES Pregunta 1 Pregunta 2 Pregunta 4 Pregunta 5 Pregunta 3 Revisado Calificación final Las Palmas de Gran Canaria a 14 de septiembre de 2006 Convocatoria Extraordinaria Fundamentos de Computadores Septiembre 2006 Pregunta 1 (1.0 Pto.) El esquema que se adjunta corresponde a un microprocesador de 8 bits con bus de direcciones de 16 bits. El banco de registros está compuesto de 5 registros de 16 bits de los que el último registro corresponde al contador de programa y el penúltimo registro es un registro temporal, denominado RTemp, no accesible por el programador. Además el procesador dispone de un registro acumulador (registro A del esquema). Se quiere añadir al procesador el modo de direccionamiento relativo al contador de programa (con desplazamiento de un byte) para las instrucciones de salto (jump) añadiendo una unidad ALU adicional, sin utilizar más registros y sin modificar ninguno de los recursos que actualmente dispone. Se pide: 1. 0.2 Dar una posible codificación de la instrucción jump relativo al contador de programa así como su notación simbólica. 2. 0.8 Modificar la ruta de datos para se pueda ejecutar dicha instrucción. Nota: El incrementador/decrementador de 16 bits es un operador que puede incrementar, decrementar o dejar pasar el dato de entrada. A Reg. Auxiliar Status IR ALSU Lógica de Control R0 R1 R2 RTemp PC 16 8 16 bits incr./decr. Señales de control Address Bus Data Bus Pregunta 2 (1.0 Pto.) En el procesador original de la pregunta anterior, el que se muestra en la figura, dar el diagrama ASM para la ejecución de una instrucción call, tomando como puntero de pila el registro R2 del banco de registros, sabiendo que el puntero de pila apunta a la última posición escrita en la pila y que la escritura en la pila avanza hacia posiciones de memoria decrecientes. Pregunta 3 (1.0 Pto.) Responder razonando brevemente: 1. 0.2 En el código que se adjunta, ¿qué resulta más ventajoso, disponer del avance de datos ALSU A o del avance de datos ALSU B? Add R0, R1, R2 Add R3, R0, DatoInmediato 2. 0.2 Suponiendo un sistema de memoria como el estudiado en clase (desviación de directorio 10 bits, desviación de tabla de páginas 10 bits y desviación de páginas 12 bits) con páginas de 4Kbytes y direccionamiento al byte. Si el procesador genera 16K direcciones consecutivas, a partir de la dirección 0, y con el TLB inicialmente vacío, ¿cuál es la tasa de acierto en el TLB? 3. 0.2 ¿Para qué se utiliza el buffer 3 de la figura adjunta? ¿En qué circunstancia se activa dicho buffer? 4. 0.2 Al repertorio del procesador CISC que se adjunta se le añade la instrucción Jumpind Src1 (PC Mem[RF[Src1]]) y se suprime la instrucción Return. Dar un código equivalente a la instrucción Return R7. 5. 0.2 En una transferencia a ráfagas usando un controlador de DMA, en un procesador de 32 bits, cuántas interrupciones se producen para transferir una página de 4Kbytes en ráfagas de 512 bytes? ¿Cuántos accesos a memoria se producen en cada ráfaga? Pregunta 4 (1.0 Pto.) Se dispone de un procesador de 16 bits con memoria virtual de 2GBytes, memoria física de 256Mbytes, direccionamiento a la palabra y página de 4Kbytes. Se pide: 1 Convocatoria Extraordinaria Fundamentos de Computadores Septiembre 2006 1. Dar el formato de la dirección virtual de tal forma que cada tabla de página ocupe una página y sabiendo que cada entrada de la tabla de páginas contiene un bit de válido. 2. ¿Cuántos procesos de 8Mbytes podrían estar cargados completamente en memoria física de forma concurrente? Suponer que se disponen de un número ilimitado de apuntadores de directorio. 3. Si la página directorio de un proceso está localizada al final de la memoria, dar el rango de direcciones físicas válidas (utilizables) de dicha página. 4. Dar el valor de la etiqueta (tag) contenida en la entrada seleccionada de una caché de correlación directa de 1Kbyte con tamaño de línea 128 bits y una sola vía correspondiente a la primera palabra de la última página, así como el índice seleccionado. 5. El siguiente código, correspondiente al procesador CISC que se adjunta, está almacenado en memoria física a partir de la dirección 0. Indicar el número de aciertos y de caché (suponiendo que se dispone de la caché anterior e inicialmente vacía) y en qué direcciones se producen: Ldir R0,600h Lrel R1,R0,20h Pregunta 5 (1.0 Pto.) Se dispone de un interfaz paralelo estándar (RS0, RS1, RD, WR, CS0 y CS1) con dos puertos de E/S de 8 bits, uno de ellos, puerto A, conectado a una impresora. Se pretende sacar por la impresora un mensaje almacenado a partir de la posición 1000h (en cada posición hay almacenado un carácter). El mensaje finaliza con el carácter 0Dh, que también hay que enviar a la impresora. Se pide: 1. Escribir, usando el ensamblador del procesador RISC que se adjunta, sin avance de datos y con predicción de salto, un programa, a partir de la posición 300h, que saque el mensaje por la impresora. Suponer el interfaz ya programado. Nota: El interfaz tiene conectada las señales CS0 y CS1 a los bits A14 y A15 CS RS0 respectivamente y el bit más significativo del 1 0 registro de estado indica, a nivel alto, impresora 1 0 lista para recibir nuevo carácter. Este bit se 1 1 borra cada vez que se envía un dato. La tabla 1 1 de verdad del interfaz es la que se adjunta. 0 X Seguir el formato adjunto para escribir el programa. Addr Programa Comentarios: Anexo al problema 3.3 2 RS1 0 1 0 1 X Registro Registro de dato del puerto A Registro de dato de puerto B Registro de Control Registro de Estado No seleccionado Convocatoria Extraordinaria Fundamentos de Computadores Septiembre 2006 Anexo Repertorio de Instrucciones para el procesador CISC: Instrucciones con registros 15 14 13 12 11 10 Tipo Op Add, Sub, And, Or, Xor Op Instrucciones de memoria 15 14 13 12 11 10 Tipo Op Linm Ldir Lrel Lin Sdir Srel Sin Denominación Dest,Src1,Src2 Condiciones eq, neq, great, goeq, less, loeq Jump Brel Denominación Dirección Dirección Call Src1, Dirección Return Src1 15 14 13 12 11 10 Tipo Op Instrucciones misceláneas Denominación No-op Clear Lstat Sstat Rtat Dest Src1, Src2 Dest Dest 8 7 6 Dest 9 8 7 6 Dest Dirección Lógica de control 9 8 7 6 Dest Dirección 9 8 7 6 Dest IR PC AR DR In Mem Out 3 5 4 3 Src1 5 4 3 Src1 5 4 3 Src1 Acción Nada RF[Dest] 0 Status RF[Src1] >=< RF[Src2] Status[Dest] 1 Status[Dest] 0 Señales de control ALSU 2 1 0 Src1 2 1 0 Src1 2 1 0 Src1 Acción PC Dirección PC PC + 1 si Status[rel] = 0 PC Dirección si Status[rel] = 1 RF[Src1] RF[Src1] + 1 Mem[Src1] PC + 1; PC Dirección RF[Src1] RF[Src1] – 1; PC Mem[Src1] RF Status 4 3 Src1 Acción RF[Dest] Dirección RF[Dest] Mem[Dirección] RF[Dest] Mem[RF[Src2]+Dirección] RF[Dest] Mem[Mem[Dirección]] Mem[Dirección] RF[Src1] Mem[RF[Src2]+Dirección] RF[Src1] Mem[Mem[Dirección]] RF[Src1] Esquema del procesador CISC: Registro de estado 5 Acción RF[Dest] RF[Src1] Op RF[Src2] Denominación Dest, Dirección Dest, Dirección Dest,Src2,Dirección Dest, Dirección Src1, Dirección Src1,Src2, Dirección Src1Dirección 15 14 13 12 11 10 Tipo Op Instrucciones de control 9 2 1 0 Src1 Convocatoria Extraordinaria Fundamentos de Computadores Septiembre 2006 Repertorio de Instrucciones para el procesador RISC 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 0 Tipo OP Dest Src1 Src2 Constante Instrucciones con registros Add, Sub, Neg, Inc, And, Or, Xor, Not Sright, Sleft, Asright, Asleft OP OP Move Shift Denominación Dest,Src1,Src2 Dest,Src1, Constante Dest, Src1 Dest, Src1, Constante Acción RF[Dest] RF[Src1] Op RF[Src2] RF[Dest] RF[Src1] Op Constante RF[Dest] RF[Src1] RF[Dest] RF[Src1] desplazar Constante 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 Tipo OP Dest Src1 Src2 Offset Instrucciones con memoria LinmU LinmL Lrel Srel Instrucciones de control Denominación Dest Dest Dest, Src2, Offset Src1, Src2, Offset Tipo Condiciones eq, neq, great, goeq, less, loeq Jump Jump Brel Instrucciones de control OP Dest Denominación Offset Src2, Offset Src1, Src2, Offset Tipo Acción RF[Dest][31:16] Offset RF[Dest][15:0] Offset RF[Dest] Mem[RF[Src2] + Offset] Mem[RF[Src2] + Offset] RF[Src1] OP Src1 Offset Acción PC PC + Offset PC RF[Src2] + Offset PC PC + 1 si RF[Src1] not rel RF[Src2] PC PC + Offset si RF[Src1] rel RF[Src2] Dest Src1 Denominación No-op Clear Sstat Rstat Src2 Src2 Offset Acción Nada RF[Dest] 0 Status[Dest] 1 Status[Dest] 0 Dest Dest Dest Esquema del procesador RISC: Lógica de decod. RF Reg. Control3 IR Reg. Destino3 Reg. Desplaz.3 A B 3 Selector Memoria de Instrucciones ALSU Selector Reg. Desplaz.4 PC Reg. Control4 Reg. Destino4 Status AR DR Selector In Selector +1 Memoria de Datos + Out 4 0