Técnica 2 (Procesador con predicción de saltos)

Anuncio

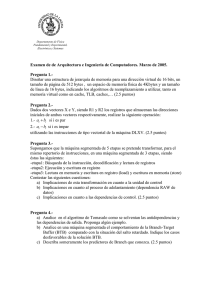

Práctica 1 (AC) – Modelado de la arquitectura MIPS con técnicas de Paralelismo de Instrucciones Ejercicio 3 - Técnica 2 – Procesador “DLX32btb” Objetivo de Diseño Diseñar e implementar un procesador con Unidad de Predicción de Saltos en el que se incluye una BTB para la determinación de la dirección del destino del salto, así como un predictor de saltos condicionales de tipo (2,2). El principal objetivo de esta técnica consiste en disminuir el número de ciclos de penalización producidos por las dependencias de control ocasionadas por las instrucciones de salto, tanto condicionales como incondicionales, cuya dirección destino del salto se codifica en el campo inmediato del formato de instrucción. En particular, la BTB anticipará la dirección destino del salto para las instrucciones: J, JAL, TRAP, BEQZ. Características Generales del Procesador DLX32btb En la Figura T2-1 se muestran los cambios más relevantes que son necesarios introducir en el procesador DLX32p para implementar la Técnica 2. A continuación, se describen los nuevos elementos microarquitecturales de las Etapas IF e ID. MUX2_BTB DLX32btb NPC_ID CONTROL BTB IPC IF/ID RS1 Reg File 4 Condición? NPC_BTB PC+4 (Técnica 2) Zero MUX2 PC Adder PC IPC BTB PC_ID Salto_ID NPC NPC_ID PC Instr Inm Adder Cache Instruccciones NPC PC_ID Salto_ID COP Figura T2-1. Microarquitectura del Procesador DLX32btb Etapa IF Al multiplexor de selección (MUX2) del nuevo valor de PC (IPC) se le añade dos entradas que corresponden a una de las salidas del módulo BTB (NPC_BTB), y la dirección de la 3 Práctica 1 (AC) – Modelado de la arquitectura MIPS con técnicas de Paralelismo de Instrucciones siguiente instrucción cuando exista fallo de predicción en la BTB en la que se consideraba que el salto se tomaba. El módulo BTB detecta la existencia de una instrucción de salto (condicional o incondicional) y predice tanto la dirección PC de la instrucción situada en el destino del salto como si el salto se va a tomar o no cuando el salto es de tipo condicional. El módulo BTB requiere un módulo de control denominado “Control BTB” que gestionará tanto su contenido como la selección de la salida del multiplexor MUX2 (MUX2_BTB[1..0]). El algoritmo de gestión lo denominamos “Algoritmo BTB” y se describe más adelante. Etapa ID En esta etapa es donde se resuelve el salto. Es decir, se calcula la condición de los saltos condicionales (Zero), así como se obtiene la dirección PC verdadera del destino del salto (Salto_ID) en el caso de que el salto se tome y se haya predecido que no se salta. En el caso de que la predicción que realizara la BTB en el ciclo anterior fuera incorrecta, se ha introducido una instrucción en la etapa IF que no debería haberse introducido. Por ello, en NPC_ID se guarda la dirección PC+4 relativa a la dirección (PC) de la instrucción de salto que se especula. NPC_ID sería el nuevo valor que se tendría que inicializar en PC al finalizar el ciclo en el que la instrucción de salto se encuentra en la etapa ID. Algoritmo BTB En la Figura T2-2 se puede observar el algoritmo de gestión del módulo BTB, de lo cual se encargará la unidad de control denominada “Control BTB”. A continuación se describen los distintos pasos del algoritmo asociándolos a las etapas de segmentación del procesador DLX32btb donde se puede encontrar una instrucción de salto. Enviar PC a Cache Instruc. y BTB Algoritmo BTB IF NO Inicializar PC = PC + 4 NO Predicción correcta: actualizar BTB y Predictor (2,2) ¿Salto tomado? SI ¿Está en BTB? Inicializar PC dependiendo de Especulación SI Predicción incorrecta: actualizar BTB, actualizar Predictor (2,2) en saltos condicionales + búsqueda instrucción correcta + eliminar IF NO Predicción incorrecta: eliminar IF + actualiza Predictor (2,2) + búsqueda instrucción correcta ¿Especulación Correcta? SI Predicción correcta: actualizar Predictor (2,2) en saltos condicionales Figura T2-2. Algoritmo de gestión del módulo BTB 4 ID Práctica 1 (AC) – Modelado de la arquitectura MIPS con técnicas de Paralelismo de Instrucciones Etapa IF: el PC actual se utiliza para direccionar la BTB. Si se detecta que ha entrado en el cauce una instrucción de salto (J, JAL, o BEQZ) y se encuentra caracterizada en la BTB (Hit=1), se analiza su predicción (P). Si P=1, la predicción establece que el salto condicional va a ser tomado y el PC en el próximo ciclo de reloj se inicializa con la dirección destino incluida en la BTB para ese salto. Si P=0, la predicción establece lo contrario. En este caso, el PC se inicializa con el valor “PC+4”. Etapa ID: durante esta etapa se analiza si el salto se toma o no a través de su código de operación y la condición de salto. En el caso de que se haya acertado en la predicción o si el salto no se encontraba en la BTB pero es Salto No Tomado, no existe penalización de ciclos de reloj. La instrucción que está actualmente en IF se está ejecutando correctamente. En el caso de que la predicción no sea correcta, o el salto no esté en la BTB y sea Salto Tomado, la instrucción que está en IF se está ejecutando incorrectamente. En caso de fallo de predicción, es en este ciclo donde se elimina la instrucción que se ejecutó en el ciclo anterior en la etapa IF, e ir a buscar la instrucción correcta. Adicionalmente, se debe actualizar la BTB (dirección destino y predicción). Módulo de Control de la BTB En la Figura T2-3 se puede observar detalladamente la interconexión entre Control BTB y el módulo BTB. clk MUX2_BTB Interconexión BTB y su control WE_BTB clk Res_Salto_ID Corr Hit Zero CONTROL BTB Hit P P COP BTB WE_Pre Registro Desplazamiento 2 bits Figura T2-3. Interconexión de los módulos BTB y Control BTB 5 Práctica 1 (AC) – Modelado de la arquitectura MIPS con técnicas de Paralelismo de Instrucciones El módulo Control BTB debe disponer de un Registro de Desplazamiento de 2 bits donde se almacene si los dos últimos saltos fueron tomados o no tomados. Estos 2 bits (Corr) se utilizan para seleccionar una de las cuatro posibles predicciones que se ofrecen para un salto determinado dentro del Predictor (2,2) que se encuentra en la BTB. El registro de desplazamiento se actualiza cuando el salto se encuentre en la Etapa EX. Por otro lado, el módulo de control genera las siguientes señales de salida: ⎯ WE_Pre: habilita la escritura en el Predictor (2,2) ⎯ WE_BTB: habilita la escritura en los restante campos de la BTB ⎯ Res_Salto_ID: indica si el salto fue realmente tomado o no en la etapa ID ⎯ MUX2_BTB: control de MUX2 Las señales de entrada al módulo de control son la siguientes: ⎯ clk: permite capturar los eventos producidos en la etapa ID del salto para que en el siguiente ciclo de reloj se pueda inicializar la BTB con la información correspondiente. Como se puede observar, la BTB también requiere la señal “clk”. Esto es debido a que se necesita para las escrituras en los campos de la BTB correspondientes. ⎯ COP: código de operación de la instrucción que se encuentra en la etapa ID. Dependiendo de si el salto es condicional o incondicional, se actualizan uno u otro campo. ⎯ Zero: indica la condición del salto en la etapa ID ⎯ Hit: Si Hit=1, indica que la instrucción que se encuentra actualmente en la Etapa IF es un salto y se encuentra caracterizado en la BTB. Si Hit=0, el salto no está en la BTB. ⎯ P: valor de la predicción del salto. P=1 corresponde a Salto Tomado, y P=0 corresponde a Salto No Tomado. En los saltos incondicionales que se encuentren en la BTB, ocurre que siempre P=1. Organización Interna de la BTB Etiquetas WE_BTB Bit Validez BTB BTB Res_Salto_ID T(1)/NT(0) Direcciones Destino J? Predictor (2,2) PC / PC_ID WE_Pre Etiqueta - Indice Corr Escritura Lectura =? clk Salto_ID Hit NPC_BTB Incondicional/ Predicción Condicional T(1)/NT(0) (1/0) J OR Acierto/Fallo (1/0) P Salta/NoSalta (1/0) Figura T2-4. Organización interna del módulo BTB 6 Práctica 1 (AC) – Modelado de la arquitectura MIPS con técnicas de Paralelismo de Instrucciones En la Figura T2-4 se observa la organización interna de la BTB. Supondremos que para la Práctica 1, existen 4 entradas. Su organización interna es parecida a una memoria cache de correspondencia directa. Se diferencian 4 campos: ⎯ Bit de Validez (1 bit): indica que la información contenida en la línea corresponde a algún salto que ya se ha ejecutado previamente. ⎯ Etiquetas (28 bits): aquí se guardan los 28 bits más significativos de la dirección de la memoria cache de instrucciones donde se encuentra la instrucción de salto. Esta etiqueta se compara con el campo Etiqueta del PC actual. En el caso de que coincidan, se produce un acierto (Hit=1). En caso contrario Hit=0. ⎯ Direcciones Destino (30 bits): aquí se guarda la dirección destino del salto, donde se encuentra almacenada la instrucción que se debe introducir en el cauce en el ciclo siguiente al de la introducción de la dirección de salto. ⎯ J? (1 bit): si J?=1, el salto es incondicional (JR, JAL, TRAP, J etc.). Si J?=0, el salto es condicional ⎯ Predictor (2,2): indica una predicción de si el salto condicional va a ser Tomado o No Tomado. Para cada entrada de la BTB, existe 4 posibles predicciones de 2 bits. La selección de una entre las cuatro posibles viene determinada por el contenido del Registro de Desplazamiento de 2 bits (Corr) que se encuentra en el módulo Control BTB. Los 2 bits asociados a cada predicción corresponden a un Contador Saturado, el cual aumenta o disminuye dependiendo de si la ejecución actual del salto es Tomado (el contador saturado aumenta en 1) o No Tomado (el contador saturado disminuye en 1). En la Figura T2-5 se puede observar detalladamente la organización interna del Predictor (2,2) de Saltos Condicionales. Se diferencian los cuatro conjunto de predictores para cada entrada de la BTB. Para generar la predicción de 1 bit “Predicción T(1)/NT(0)”, los dos bits de los correspondientes contadores seleccionados a través de “Indice” se pasan a través de una “Tabla 2:1”. Posteriormente, se selecciona a través de “Corr” para luego combinarse con “J?”. 7 Práctica 1 (AC) – Modelado de la arquitectura MIPS con técnicas de Paralelismo de Instrucciones Predictor (2,2) de Saltos Condicionales Res_Salto_ID T(1)/NT(0) Predictor (2,2) Res_Salto_ID T(1)/NT(0) WE_Pre Indice Corr Predicción T(1)/NT(0) WE_Pre Indice Corr clk WE_Pre Indice Tabla 2:1 clk Res_Salto_ID 1(+1)/0(-1) 00 NT 00 NT 00 NT 00 NT 01 NT 01 NT 01 NT 01 NT 10 T 10 T 10 T 10 T 11 T 11 T 11 T 11 T Corr Contador Saturado 2-bits MUX Predicción T(1)/NT(0) Figura T2-5. Organización interna del Predictor (2,2) En el proceso de escritura, cuando se produce la inicialización de cualquiera de los campos del Predictor (2,2), se involucran las siguientes señales: ⎯ ⎯ ⎯ ⎯ clk: uno de los flancos activa la escritura en los contadores WE_Pre: indica que se produzca la escritura Indice: selecciona un conjunto de 4 predictores Corr: de los 4 predictores que selecciona Indice, esta señal de 2 bit selecciona uno de ellos ⎯ Res_Salto_ID: da el valor del resultado del salto actual que es obtenido cuando el salto condicional se encuentra en la etapa ID 8