Diseño de un Power On Reset con brown

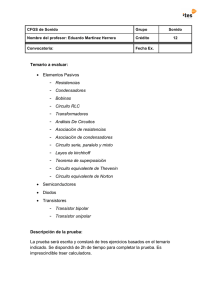

Anuncio