Solución de encapsulado para chips fotónicos en Silicio con

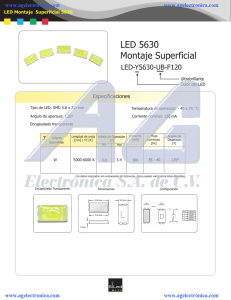

Anuncio