Diseño combinacional (Parte #2) Mapas de Karnaugh

Anuncio

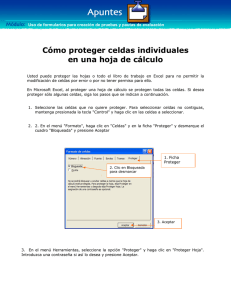

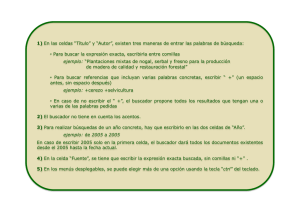

Departamento de Electrónica Electrónica Digital Diseño combinacional (Parte #2) Mapas de Karnaugh Facultad de Ingeniería Bioingeniería Universidad Nacional de Entre Ríos Procedimiento de diseño de un circuito combinacional Determinación de la función lógica 1. Forma canónica de suma de productos Expresión algebraica de una función lógica como la suma de los minitérminos de la función. • Considera únicamente las combinaciones de entrada que hacen 1 la función • Cada variable aparece complementada si su valor es 0 y sin complementar si es 1 2. Forma canónica de producto de sumas Expresión algebraica de una función lógica como el producto de los maxitérminos de la función. • Considera únicamente las combinaciones de entrada que hacen 0 la función (salida) • Cada variable aparece complementada si su valor es 1 y sin complementar si es 0 Simplificación Simplificación por mapas de Karnaugh (mapas K) Método gráfico para simplificar funciones Es una representación matricial de una tabla de verdad: • una celda del mapa = una fila de la tabla de verdad Muy práctico para funciones de no más de 4 ó 5 variables Ejemplo de mapa de 2 variables B A 0 0 1 1 0 2 1 3 Principales características del mapa K Cada celda se corresponde con un minitérmino ó maxitérmino de la función En cada celda se escribe el valor de la salida de la función lógica para ese minitérmino/maxitérmino. Cada celda difiere de la adyacente en solo una variable. La numeración de las filas/columnas es en código Gray Las filas/columnas externas son adyacentes entre sí Ejemplo de mapa de 4 variables numeración en código continuo variables de entrada DC BA 00 00 número de minitérmino 01 celdas adyacentes 11 10 celdas adyacentes 01 11 10 0 4 12 8 1 5 13 9 3 7 15 11 2 6 14 10 Reglas de aplicación 1. Agrupar todas las celdas con el mismo valor, en uno o más grupos de celdas adyacentes 2. La cantidad de celdas en un grupo debe ser potencia de 2 (2, 4, 8) 3. Maximizar la cantidad de celdas en cada grupo 4. Minimizar la cantidad de grupos 5. Superponer grupos siempre que sea posible (una celda puede estar en uno o más grupos), si eso conduce a cumplir 2, 3 y 4. Fundamento del método En celdas adyacentes, sólo cambia el valor de una de las variables entre los dos términos representado por cada celda aplicando álgebra de Boole se elimina la variable que cambia de valor. C B A Z 0 0 0 1 0 0 1 0 0 1 0 1 0 1 1 0 1 0 0 1 1 0 1 1 1 1 0 0 1 1 1 0 Z1 = A’B’C’ + A’BC’ = A’C’ (B’ + B) = A’C’ Z2 = A’CB’ + ACB’ = CB’ (A’ + A) = CB’ Z = Z1 + Z2 = A’C’ + CB’ CB A 00 01 11 10 0 1 1 1 0 0 0 1 Z =A’C’ + CB’ 0 1 Simplificación por unos lógicos (mapa K de minitérminos) Agrupar las celdas de valor 1 (minitérminos) Cada grupo representa a un término producto Un grupo de 2k celdas elimina k variables del término resultante Grupo de 2 celdas: elimina 1 variable Grupo de 4 celdas: elimina 2 variables Grupo de 8 celdas: elimina 3 variables A = 0/1, B = 1, A se elimina A = 1, B = 0/1, B se elimina B A 0 1 0 2 0 1 1 1 1 1 3 Z=A+B BIEN B A 0 1 0 2 0 1 1 1 1 1 3 Z = A + A’ B = A + B MAL paso adicional Ejemplos CB A 00 01 11 10 MAL CB A 00 01 11 10 0 1 1 1 0 1 1 1 2 3 0 0 6 7 1 0 0 1 1 1 1 1 1 Z = C’ + A’B’C = C’ + A’B’ 4 5 CB A 00 01 11 10 BIEN 0 1 1 1 1 1 1 Z = C’ + A’B’ CB A 00 01 11 10 CB A 00 01 11 10 0 1 1 1 0 1 1 1 2 3 1 1 6 7 0 0 4 0 1 1 1 1 1 1 1 MAL Z = C’ + BC 5 CB A 00 01 11 10 0 1 1 1 1 1 1 1 MAL CB A 00 01 11 10 0 1 1 1 1 1 1 1 Z = C’ + B BIEN DC BA 00 01 11 10 0 4 12 8 00 1 01 11 1 10 1 1 3 1 2 5 13 1 1 7 15 1 6 DC BA 00 01 11 10 0 4 12 8 00 1 9 01 11 11 1 14 1 10 10 1 3 1 1 2 DC BA 00 01 11 10 0 4 12 8 00 1 1 11 1 10 1 1 3 2 1 5 13 7 15 6 14 13 9 15 11 14 10 1 1 7 1 6 1 • Identificar primero las celdas que solo tienen una posibilidad de agrupación (y agruparlas). BIEN MAL 01 1 5 1 9 11 10 1 DC BA 00 01 11 10 0 4 12 8 00 1 1 01 1 11 1 10 1 1 3 2 1 5 13 7 15 6 14 1 9 11 10 1 • Continuar con el resto de las celdas. Más ejemplos DC BA 00 01 11 10 0 4 12 8 00 1 1 01 11 10 1 1 5 13 9 15 11 14 10 1 3 1 7 1 2 1 6 1 DC BA 00 01 11 10 0 4 12 8 00 1 1 1 1 5 1 3 1 2 01 1 1 11 10 13 9 7 15 11 6 14 10 1 Caso especial DC BA 00 01 11 10 0 4 12 8 00 1 1 1 1 01 11 10 DC BA 00 01 11 10 0 4 12 8 00 1 1 1 5 13 9 01 3 7 15 11 11 1 1 1 2 6 14 10 Z = B’D’ + A’B’ + ABC’D 10 1 1 5 13 9 3 7 15 11 2 6 14 10 1 Z = A’C’ = A’B’C’D’ + A’B’C’D + A’BC’D’ + A’BC’D = A’B’C’ + A’BC’ = … = A’C’ Simplificación por ceros lógicos (mapa K de maxitérminos) Agrupar las celdas de valor 0 lógico. Cada grupo representa un término suma. Un grupo de 2k celdas elimina k variables del término resultante. A = 0/1, se elimina B = 0, C = 1, se complementa CB A 00 01 11 10 0 1 1 1 0 1 1 1 2 3 1 1 6 7 0 0 4 5 ZM = (C’ + B) Si se agrupara por minitérminos: CB A 00 01 11 10 0 1 1 1 0 1 1 1 2 3 1 1 6 7 0 0 4 5 Zm = C’ + B Ejemplos DC BA 00 01 11 10 00 01 11 10 0 4 12 1 5 13 0 0 3 0 7 0 0 2 0 6 0 0 00 8 9 15 11 14 10 Z = (B’ + C’).(D’ + C) 00 0 01 0 11 0 10 0 01 0 11 4 12 1 5 13 3 7 15 2 6 14 Z=C 00 10 0 0 8 9 11 0 10 0 00 01 11 10 01 0 11 4 10 12 8 0 1 5 13 9 0 3 2 0 0 7 6 15 11 14 10 0 0 0 0 Funciones con combinaciones indiferentes (no importa - don’t care) Combinaciones de entrada para las que no importa el valor de la salida. – Porque no se ha especificado el comportamiento del circuito – Porque son imposibles En la tabla de verdad y en los mapas K, la salida para estas combinaciones se indica con una letra X o d. En la simplificación por mapas K, estas celdas se toman como si tuvieran valor 1 ó 0, según conveniencia. Usarlas para maximizar el tamaño de los grupos No agrupar celdas que solamente contengan X Implicancias del uso de X en un diseño. minitérminos maxitérminos DC BA 00 01 11 10 0 4 12 8 00 X 01 DC BA 00 01 11 10 0 4 12 8 00 0 0 x 0 1 5 3 7 1 1 2 6 1 x 01 0 x 11 x 1 10 0 x 13 9 15 11 14 10 1 x MAL 11 10 1 X 3 X 1 2 X 5 13 9 15 11 14 10 1 X 7 1 1 6 1 X DC BA 00 01 11 10 0 4 12 8 00 X BIEN 01 11 10 1 X 3 X 1 2 X 5 13 9 15 11 14 10 1 X 7 1 1 6 1 X DC BA 00 01 11 10 0 4 12 8 00 0 0 X 0 1 5 13 3 7 15 2 6 14 01 0 X 11 X 10 0 X X 9 11 10 X DC BA 00 01 11 10 0 4 12 8 00 0 0 X 0 1 5 13 3 7 15 2 6 14 01 0 X 11 X 10 0 X X 9 11 10 X Ejemplo: detector de números BCD pares DC BA 00 01 11 10 0 4 12 8 00 1 1 1 01 11 10 1 5 13 9 3 7 15 11 2 6 14 10 1 1 Z = D/A/ + A/B/C/ #compuertas: 7 #CIs: 3 (1 INV, 1 AND 3i, 1 OR 2i) Z = [(D+A)/ + (A+B+C)/]// (todo NOR) #compuertas: 4 #CI: 2 (1 NOR 2i, 1NOR 3i) Usando las condiciones no importa: DC BA 00 01 11 10 0 4 12 8 00 1 1 X 1 01 11 10 1 5 3 7 X X 2 6 X X 1 1 13 9 15 11 14 10 X Z = A’ SW: KarnaughMap Ejemplo de diseño #1: circuito para encender un display de 7 segmentos a f g b e d c ¿Qué código de entrada usaría el circuito? ¿Cuántas E y S tendría el circuito? 4 (BCD) Circuito combinacional 7 Diseño Diseño 1. Número de entradas y salidas Entradas: 4 - código BCD (ALSB, B, C, D) Salidas: 7 (a, b, ...,g) Función de múltiples salidas 3. Obtención de las funciones 7 funciones 7 mapas de 4 variables Criterio de diseño: ¿Qué desventaja tiene usar X en este caso? ¿Qué valor le daría a las X? 2. Tabla de verdad Diseño Ejemplo de diseño #2: conversión electrónica de binario a Gray Entradas: 4 (binario natural) Salidas: 4 (Gray) B3B2 B1B0 00 01 11 10 00 01 11 10 0 4 1 5 3 7 1 1 2 6 1 1 B3B2 00 B1B0 12 8 13 9 01 15 11 11 14 10 10 1 1 1 1 G3 = B3 00 01 0 1 1 1 11 4 12 5 13 10 1 1 3 1 7 15 1 2 1 6 14 1 8 9 11 10 G2 = B3B2/+ B3/B2 = B3 B2 Diseño B1 G1 B2 G2 B3 G3 Conversor binario-Gray de 3 bits Generalizando para n bits: Gn = Bn Gi = Bi xor Bi+1 para i entre 1 y n-1 Mapas K de 5 y 6 variables 30/04/2013 Tips finales acerca del diseño combinacional Más de 6 variables de entrada: no se puede usar mapas K La minimización es importante… pero más lo es el diseño correcto! Algoritmo de Quine-McCluskey • Funciones de hasta 8-12 variables Programas heurísticos (p.e., Espresso, Minilog) • Usados en casos de problemas grandes Programas para manipular las expresiones y minimizar o PALASM, ABEL, CUPL (para PLDs Programmable Logic Devices) o VHDL, Verilog, para ASICs Application-Specific IC) FIN