PRACTICA N0.3

Anuncio

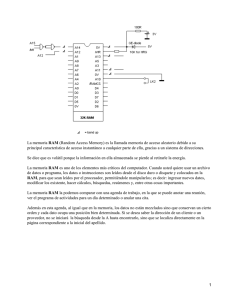

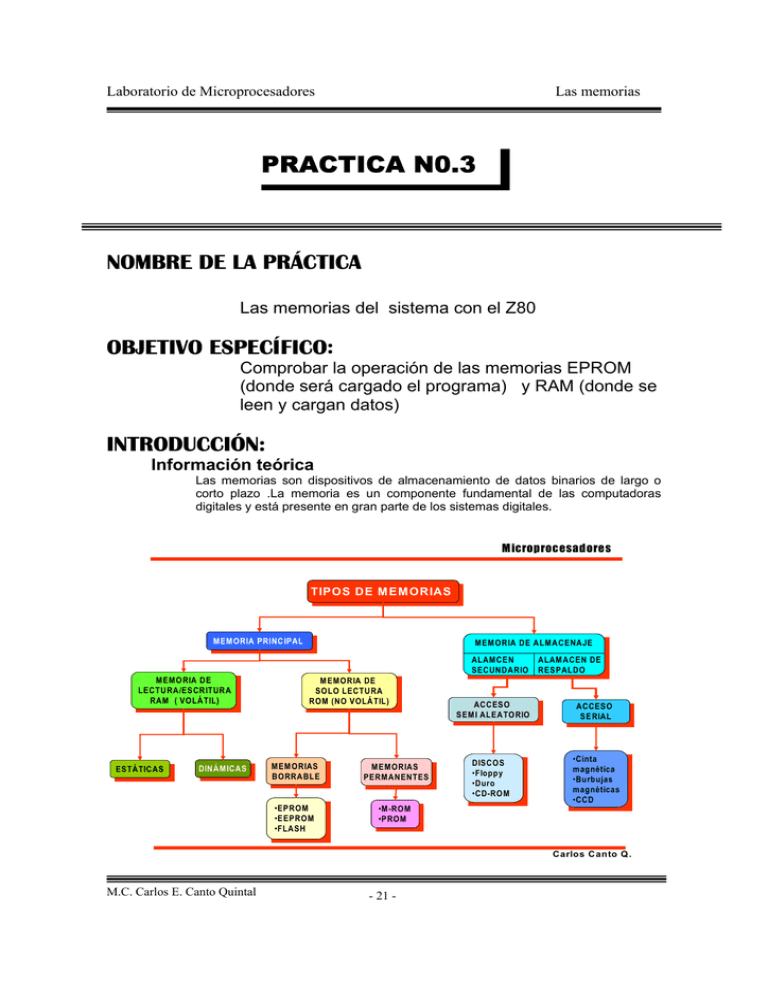

Laboratorio de Microprocesadores Las memorias PRACTICA N0.3 NOMBRE DE LA PRÁCTICA Las memorias del sistema con el Z80 OBJETIVO ESPECÍFICO: Comprobar la operación de las memorias EPROM (donde será cargado el programa) y RAM (donde se leen y cargan datos) INTRODUCCIÓN: Información teórica Las memorias son dispositivos de almacenamiento de datos binarios de largo o corto plazo .La memoria es un componente fundamental de las computadoras digitales y está presente en gran parte de los sistemas digitales. M icroprocesadores TIPOS TIPOSDE DEMMEM EMORIAS ORIAS MEMORIA M EMORIAPRINCIPAL PRINCIPAL MEMORIA DE ALMACENAJE ALAMCE N SECUNDARIO MEMORIA MEM ORIADE DE LECTURA/ESCRITURA LECTURA/ESCRITURA RAM RAM ( (VOLÁTIL) VOLÁTIL) ESTÁTICAS ESTÁTICAS DINÁMICAS DINÁMICAS MMEM EMORIA ORIADE DE SOLO SOLOLECTURA LECTURA ROM ROM(NO (NOVOLÁTIL) VOLÁTIL) MEMORIAS MEM ORIAS BORRABLE BORRABLE MEMORIAS M EMORIAS PERMANENTES PERMANENTES •EPROM •EPROM •EEPROM •EEPROM •FLASH •FLASH •M -ROM •M-ROM •PROM •PROM ALAM ACEN DE RESPALDO ACCESO ACCESO SEM I ALEATORIO SEMI ALEATORIO ACCESO ACCESO SERIAL SERIAL DISCOS DISCOS •Floppy •Floppy •Duro •Duro •CD-ROM •CD-ROM •Cinta •Cinta magnética magnética •Burbujas •Burbujas magnéticas magnéticas •CCD •CCD C arlos C anto Q . M.C. Carlos E. Canto Quintal - 21 - Laboratorio de Microprocesadores Las memorias MEMORIAS DE ACCESO ALEATORIO Las memorias de Acceso Aleatorio son conocidas como memorias RAM de sus siglas en inglés Random Access Memories. Se caracterizan por ser memorias de lectura/escritura y contienen un conjunto de variables de dirección que permiten seleccionar cualquier dirección de memoria de forma directa e independiente de la posición en la que se encuentre. Estas memorias son volátiles, es decir, que se pierde la información cuando no hay energía y se clasifican en dos categorías básicas: la RAM estática y la RAM dinámica, las cuales se describen en las siguientes dos secciones. MEMORIA RAM ESTÁTICA Este tipo de memoria conocida como SRAM (Static Random Access Memory) se compone de celdas conformadas por flip-flops construidos generalmente con transistores MOSFET, aunque también existen algunas memorias pequeñas construidas con transistores bipolares. Estructura de una celda de memoria SRAM MEMORIA RAM DINÁMICA Este tipo de memoria conocida como DRAM (Dinamic Random Access Memories), a diferencia de la memoria estática se compone de celdas de memoria construidas con condensadores. Las celdas de memoria son de fabricación más sencillas en comparación a las celdas a base de transistores, lo cual permite construir memorias de gran capacidad. Celda de memoria de una DRAM La operación de la celda es similar a la de un interruptor, cuando el estado en la fila se encuentra en alto, el transistor entra en saturación y el dato presente en el bus interno de la memoria (columna) se almacena en el condensador, durante una operación de escritura y se extrae en una operación de lectura. El inconveniente que tiene este tipo de memorias consiste en que hay que recargar la información almacenada en las celdas, por lo cual estas celdas requieren de circuitería adicional para cumplir esta función. Sistema lectura, escritura y recarga de una celda DRAM M.C. Carlos E. Canto Quintal - 22 - Laboratorio de Microprocesadores Memoria SRAM Las memorias Ventajas Desventajas La velocidad de acceso es alta. Para retener los datos solo necesita estar energizada. Menor capacidad, debido a que cada celda de almacenamiento requiere mas transistores. Mayor costo por bit. Son mas fáciles de diseñar. Mayor consumo de Potencia. DRAM Mayor densidad y capacidad. La velocidad de acceso es bajar. Menor costo por bit. Necesita recargar de la información. almacenada para retenerla. Menor consumo de potencia. Diseño complejo. . MEMORIA ROM (READ ONLY MEMORY) O MEMORIA ROM DE MÁSCARA Las memorias de solo lectura son conocidas como memorias ROM de la sigla en inglés Read Only Memories. Se caracterizan por ser memorias de lectura y contienen celdas de memoria no volátiles, es decir que la información almacenada se conserva sin necesidad de energía. Este tipo de memoria se emplea para almacenar información de forma permanente o información que no cambie con mucha frecuencia. Se programan mediante máscaras. Es decir, el contenido de las celdas de memoria se almacena durante el proceso de fabricación para mantenerse después de forma irrevocable. Desde el instante en que el fabricante grabo las instrucciones en el Chip, por lo tanto la escritura de este tipo de memorias ocurre una sola vez y queda grabado su contenido aunque se le retire la energía. Se usa para almacenar información vital para el funcionamiento del sistema: en la gestión del proceso de arranque, el chequeo inicial del sistema, carga del sistema operativo y diversas rutinas de control de dispositivos de entrada/salida suelen ser las tareas encargadas a los programas grabados en ROM. Estos programas forman la llamada BIOS (Basic Input Output System). La memoria ROM constituye lo que se ha venido llamando Firmware, es decir, el software metido físicamente en hardware. El elevado coste del diseño de la máscara sólo hace aconsejable el empleo de los microcontroladores con este tipo de memoria cuando se precisan cantidades superiores a varios miles de unidades. Las características fundamentales de las memorias ROM son: 1. Alta densidad: la estructura de la celda básica es muy sencilla y permite altas integraciones. 2. No volátiles: el contenido de la memoria permanece si se quita la alimentación. 3. Costo: dado que la programación se realiza a nivel de máscaras durante el proceso de fabricación, resultan baratas en grandes tiradas, de modo que el coste de fabricación se reparte en muchas unidades y el coste unitario es baja. 4. Sólo lectura: únicamente son programables a nivel de máscara durante su fabricación. Su contenido, una vez fabricada, no se puede modificar. Hay muchos tipos de ROM: M.C. Carlos E. Canto Quintal - 23 - Laboratorio de Microprocesadores Las memorias Una ROM puede estar fabricada tanto en tecnología bipolar como MOS. MEMORIA PROM (PROGRAMMABLE READ ONLY MEMORIES) Una alternativa para proyectos pequeños es el uso de una de las memorias de sólo lectura programables o PROM. Permiten que el usuario mismo pueda programar el dispositivo, ahorrándose el alto costo de la producción de la máscara Sus contenidos no se construyen, como la ROM, directamente en el proceso de fabricación, sino que se tiene la posibilidad de que el usuario las pueda programar. El proceso de programación es destructivo: una vez grabada, es como si fuese una ROM normal. Las prestaciones de las memorias PROM son similares a las anteriores, con la única salvedad del proceso de programación. La escritura de la memoria PROM tiene lugar fundiendo los fusibles necesarios por lo que la memoria PROM solo puede ser programada una vez. MEMORIA EPROM (ERASABLE PROGRAMMABLE READ ONLY MEMORIES) Este tipo de memoria es similar a la PROM con la diferencia que la información se puede borrar y volver a grabar varias veces. La programación se efectúa aplicando a un pin especial de la memoria una tensión entre 10 y 25 Voltios durante aproximadamente 50 ms, según el dispositivo, al mismo tiempo se direcciona la posición de memoria y se pone la información a las entradas de datos. Este proceso puede tardar varios minutos dependiendo de la capacidad de memoria. La memoria EPROM se compone de un arreglo de transistores MOSFET de Canal N de compuerta aislada. Una vez grabada una EPROM con la información pertinente, por medio de un dispositivo programador de memorias, la misma es instalada en el sistema correspondiente donde efectivamente será utilizada como dispositivo de lectura solamente. Eventualmente, ante la necesidad de realizar alguna modificación en la información contenida o bien para ser utilizada en otra aplicación, la EPROM es retirada del sistema, borrada mediante la exposición a luz ultravioleta con una longitud de onda de 2537 Angstroms (unidad de longitud por la cual 1 A = 10-10 m), programada con los M.C. Carlos E. Canto Quintal - 24 - Laboratorio de Microprocesadores Las memorias nuevos datos, y vuelta a instalar para volver a comportarse como una memoria de lectura solamente. Para poder ser expuesta a al luz UV, para su borrado, está encapsulada con una ventana transparente de cuarzo sobre la pastilla de la EPROM. Una EPROM no puede ser borrada parcial o selectivamente; de ahí que por más pequeña que sea la eventual modificación a realizar en su contenido, inevitablemente se deberá borrar y reprogramar en su totalidad. Los tiempos medios de borrado de una EPROM, por exposición a la luz ultravioleta, oscilan entre 10 y 30 minutos. El microprocesador no puede cambiar el contenido de la memoria ROM. Lámpara Lámparade deLuz Luz Ultravioleta Ultravioletadel deltipo tipo germicida germicida λ=2537 ηm (Ultravioleta) Dado que cualquier sistema microprocesador requiere de al menos un mínimo de memoria no volátil donde almacenar ya sea un sistema operativo, un programa de aplicación, un lenguaje intérprete, o una simple rutina de "upload", es necesario utilizar un dispositivo que preserve su información de manera al menos semi-permanente. Y aquí es donde comienzan a brillar las EPROMs. La familia 2700 Los dispositivos EPROM de la familia 2700 contienen celdas de almacenamiento de bits configuradas como bytes direccionables individualmente. Habitualmente esta organización interna suele denominarse como 2K x 8 para el caso de una 2716, 8k x 8 para una 2764, etc. Por razones de compatibilidad (tanto con dispositivos anteriores como con dispositivos futuros), la gran mayoría de las EPROMs se ajustan a distribuciones de terminales o "pin-outs" estándar. Para el caso mas usual, que es el encapsulado DIP (Dual In-Line Package) de 28 pines, el estándar utilizado es el JEDEC-28. Si bien en la actualidad parece haberse uniformado razonablemente, las tensiones de programación varían en función tanto del dispositivo, como del fabricante; así nos encontramos con tensiones de programación (Vpp) de 12,5V, 13V, 21V y 25V. Lo mismo sucede con otros parámetros importantes que intervienen en el proceso de grabación de un EPROM, como es el caso de la duración de dicho pulso de programación y los niveles lógicos que determinan distintos modos de operación. MEMORIA EEPROM (ELECTRICAL ERASABLE PROGRAMMABLE READ ONLY MEMORY) La memoria EEPROM es programable y borrable eléctricamente Actualmente estas memorias se construyen con transistores de tecnología MOS (Metal Oxide Silice) y MNOS (Metal Nitride-Oxide Silicon). Las celdas de memoria en las EEPROM son similares a las celdas EPROM y la diferencia básica se encuentra en la capa aislante alrededor de cada compuesta flotante, la cual es más delgada y no es fotosensible. M.C. Carlos E. Canto Quintal - 25 - Laboratorio de Microprocesadores Las memorias Se programan de forma casi idéntica pero tienen la posibilidad de ser borradas eléctricamente. Esta característica permite que puedan ser programadas y borradas “en el circuito”. La programación de estas memorias es similar a la programación de la EPROM, la cual se realiza por aplicación de una tensión de 21 Voltios a la compuerta aislada MOSFET de cada transistor, dejando de esta forma una carga eléctrica, que es suficiente para encender los transistores y almacenar la información. El borrado de la memoria se efectúa aplicando tensiones negativas sobre las compuertas para liberar la carga eléctrica almacenada en ellas. Las memorias EEPROM son memorias no volátiles y eléctricamente borrables a nivel de bytes. La posibilidad de programar y borrar las memorias a nivel de bytes supone una gran flexibilidad, pero también una celda de memoria más compleja. Además del transistor de compuerta flotante, es preciso un segundo transistor de selección. El tener 2 transistores por celda hace que las memorias EEPROM sean de baja densidad y mayor coste. La programación requiere de tiempos que oscilan entre 157 µ s y 625 µ s=byte. En cuanto a la forma de referenciar los circuitos, estas memorias suelen comenzar con el prefijo 28, de forma que la 2864 indica una memoria EEPROM de 64Kbytes, equivalente en cuanto a patillaje y modo de operación de lectura a la UVPROM 2764. Una ventaja adicional de este tipo de memorias radica en que no necesitan de una alta tensión de grabado, sirven los 5 voltios de la tensión de alimentación habitual. Características Técnicas Referencia 28C64A Tipo EEPROM CMOS Capacidad (bits) 8192 X 8 Tipo de salida 5V Tiempos de Acceso 120/150/200 ns Encapsulado DIL-28 y PLCC-32 Ventajas de la EEPROM: La programación y el borrado pueden realizarse sin la necesidad de una fuente de luz UV y unidad programadora de PROM, además de poder hacerse en el mismo circuito gracias a que el mecanismo de transporte de cargas, requiere corrientes muy bajas. Las palabras almacenadas en memoria se pueden borrar de forma individual. Para borra la información no se requiere luz ultravioleta. Las memorias EEPROM no requieren programador. De manera individual puedes borrar y reprogramar eléctricamente grupos de caracteres o palabras en el arreglo de la memoria. El tiempo de borrado total se reduce a 10ms en circuito donde su antepasado inmediato requería media hora bajo luz ultravioleta externa. El tiempo de programación depende de un pulso por cada palabra de datos de 10 ms, versus los 50 ms empleados por una ROM programable y borrable. Se pueden reescribir aproximadamente unas 1000 veces sin que se observen problemas para almacenar la información. Para reescribir no se necesita hacer un borrado previo. Aplicaciones de las Memorias EEPROM Encontramos este tipo de memorias en aquellas aplicaciones en las que el usuario M.C. Carlos E. Canto Quintal - 26 - Laboratorio de Microprocesadores Las memorias necesita almacenar de forma permanente algún tipo de información; por ejemplo en los receptores de TV para memorizar los ajustes o los canales de recepción. MEMORIA FLASH La memoria FLASH es similar a la EEPROM, es decir que se puede programar y borrar eléctricamente, son de alta densidad (gran capacidad de almacenamiento de bits). Alta densidad significa que se puede empaquetar en una pequeña superficie del chip, gran cantidad de celdas, lo que implica que cuanto mayor sea la densidad, más bits se pueden almacenar en un chip de tamaño determinado. Se caracteriza por tener alta capacidad para almacenar información y es de fabricación sencilla, lo que permite fabricar modelos de capacidad equivalente a las EPROM a menor costo que las EEPROM. Las operaciones básicas de una memoria Flash son la programación, la lectura y borrado. La programación se efectúa con la aplicación de una tensión (generalmente de 12V o 12.75 V) a cada una de las compuertas de control, correspondiente a las celdas en las que se desean almacenar 0’s. Para almacenar 1’s no es necesario aplicar tensión a las compuertas debido a que el estado por defecto de las celdas de memoria es 1. La lectura se efectúa aplicando una tensión positiva a la compuerta de control de la celda de memoria, en cuyo caso el estado lógico almacenado se deduce con base en el cambio de estado del transistor: Si hay un 1 almacenado, la tensión aplicada será lo suficiente para encender el transistor y hacer circular corriente del drenador hacia la fuente. Si hay un 0 almacenado, la tensión aplicada no encenderá el transistor debido a que la carga eléctrica almacenada en la compuerta aislada. Para determinar si el dato almacenado en la celda es un 1 ó un 0, se detecta la corriente circulando por el transistor en el momento que se aplica la tensión en la compuerta de control. El borrado consiste en la liberación de las cargas eléctricas almacenadas en las compuertas aisladas de los transistores. Este proceso consiste en la aplicación de una tensión lo suficientemente negativa que desplaza las cargas como se indica en la figura. APLICACIONES DE LA MEMORIA FLASH Actualmente, los usos de Memoria Flash se están incrementando rápidamente. Ya sean cámaras digitales, Asistentes Digitales Portátiles, reproductores de música digital o teléfonos celulares, todos necesitan una forma fácil y confiable de almacenar y transportar información vital. Se utilizan en la fabricación de BIOS para computadoras. , generalmente conocidos como FLASH-BIOS. La ventaja de esta tecnología es que permite actualizar el bios con un software proporcionado por el fabricante, sin necesidad de desmontar el chip del circuito final, ni usar aparatos especiales. Por esto la Memoria Flash se ha convertido en poco tiempo en una de las más populares tecnologías de almacenamiento de datos. Es más flexible que un diskette y puede almacenar hasta gigabytes de información. Es mucho más rápida que un disco duro, y a diferencia de la memoria RAM, la Memoria Flash puede retener datos aun cuando el equipo se ha apagado. EJEMPLO DE MEMORIA FLASH - 27F256 M.C. Carlos E. Canto Quintal - 27 - Laboratorio de Microprocesadores Las memorias Características Técnicas Referencia 28F256 Tipo FLASH EEPROM Capacidad (bits) 32768 X 8 Tipo de salida (5V) (Vp=12.5V) Tiem pos de Acceso 90/100/120/150 ns Encapsulado DIL-28 La capacidad de esta memoria es de 32K X 8 y como memoria Flash tiene la característica particular de ser borrada en un tiempo muy corto (1 seg.). El tiempo de programación por byte es de 100 ns y el tiempo de retención de la información es de aproximadamente 10 años DIFERENCIA ENTRE MEMORIAS EEPROM Y EPROM FLASH La diferencia de las memorias flash y las EEPROM reside en su velocidad: Son más rápidas en términos de programación y borrado, aunque también necesitan de una tensión de grabado del orden de 12 voltios. Otra diferencia la encontramos en que en las EEPROM se puede borrar de forma selectiva cualquier byte, mientras que en las memorias FLASH sólo admite el borrado total de la misma. Por otra parte esta memorias son bastante más baratas que las EEPROM, debido a que utilizan una tecnología más sencilla y se fabrican con grandes capacidades de almacenamiento. Un dato puede ser significativo: el tiempo de borrado de un byte es del orden de 100 µ seg. TABLA COMPARATIVA ENTRE MEMORIAS MEMORIAS USADAS EN ESTA PRÁCTICA: LA MEMORIA RAM 6116 M.C. Carlos E. Canto Quintal - 28 - Laboratorio de Microprocesadores Las memorias CARACTERÍSTICAS 24 terminales. fabricada con la tecnología CMOS, Organización de la memoria: 2048 X 8 Alta velocidad: tiempo de acceso 150 nseg. Baja potencia en estado inactivo: 10 uW Baja potencia en estado activo: 160 mW RAM completamente estática: No requiere reloj para su funcionamiento Temperatura de operación: 0.75 grados centígrados Temperatura de almacenamiento: De -55 a +125 grados centígrados. Potencia de disipación: 1 Watts Todas sus entradas y salidas son compatibles directamente con la tecnología TTL Es directamente compatible con las memorias de 16K estándar, tipo RAM 6132 LA MEMORIA EPROM 2716 Microprocesadores Configuración de terminales y símbolo lógico de la memoria estática R/W CMOS 6116 PINS DEL CHIP CE WE OE A10 Bus de direcciones A7 1 A6 2 24 Vcc 23 A8 A5 3 A4 4 22 A9 21 WE 20 OE A3 5 A2 6 CMOS 6116 A1 7 17 DQ7 16 DQ6 A0 8 DQ0 9 A0 CS WE OE 1 x x TRI-STATE 1 1 1 TRI-STATE 0 0 1 ENTRADA 0 1 0 SALIDA 15 DQ5 DQ1 10 DQ2 11 Vss 12 Datos E/S 19 A10 18 CE 14 DQ4 13 DQ3 Nombre de los terminales BUS DE DATOS A0-A10 Entradas de Direcciones VCC Potencia(+5) CE Chip Enable WE Write Enable VSS Ground OE Output Enable DQ0-DQ7 Data In/Data Out Carlos Canto Q. CARACTERÍSTICAS Tecnología CMOS de canal N. 24 terminales Tiempo de acceso menor que 250 nseg. Bajo consumo de potencia : M.C. Carlos E. Canto Quintal - 29 - Laboratorio de Microprocesadores Las memorias Disipación en estado activo: 525 mW máx. Disipación en estado inactivo: 132 mW máx. Fuente de alimentación de +5 Volts Entradas y salidas compatibles con la tecnología TTL Capacidad de colocarse en tercer estado. Características Técnicas Referencia 27C16B Tipo EPROM CMOS Capacidad (bits) 2048 X 8 Tipo de salida (5V) (Vp=12.75V) Tiempos de Acceso 150/250 ns Encapsulado DIL-24 DESCRIPCIÓN DE LAS TERMINALES A0-A10: Lineas de direcciones D0-D7: Salida de datos (CE)' Habilitador de la pastilla (OE)' Habilitador de salidas PGM Condición de programación Vcc Voltaje de alimentación +5.0 Volts Vss Terminal de tierra 0.0 Volts • Vpp Voltaje de programación • NC No conexión OPERACIÓN DE LECTURA Para leer la memoria, la terminal Vpp se conecta a Vcc para inhibir con esto la programación, las entradas (OE)' y (CE)' se colocan a tierra y con estas simples conexiones se puede leer la memoria, los datos estarán sobre las terminales D0 - D7, quienes indican el dato direccionado por las terminales A0 - A10, cuya capacidad es de (2K X 8), 2048 localidades de 8 bits cada una. MODO DE PROGRAMACIÓN Para programar la memoria se requieren las siguientes conexiones: En la terminal 18 (CE/PGM) se debe depositar un pulso con una duración Tw = 45 mseg aproximadamente, dicho pulso podrá aplicársele con un monoestable. La terminal 20 (OE)’ que es el habilitador de salidas se conecta a +5.0 Volts (la alimentación). La terminal 21 (VPP), voltaje de programación se conecta a un voltaje fijo de +25.0 Volts, la memoria normalmente cuando no esta grabada contiene "unos", por lo tanto en la operación de grabación se procede a depositar ceros. Se requiere un capacitor de 0.1 uF dispuesto entre +Vcc y GND para suprimir los estados transitorios de tensión que puedan dañar al dispositivo EPROM 2716. Se pueden programar varias EPROM 2716 en paralelo con la misma información, debido a la simplicidad de los requerimientos de programación. CORRELACIÓN CON TEMAS DEL PROGRAMA VIGENTE: Con esta práctica se cubre algunos de los aspectos de la unidad I: Microprocesadores de 8 Bits. M.C. Carlos E. Canto Quintal - 30 - Laboratorio de Microprocesadores Las memorias MATERIAL Y EQUIPO UTILIZADO: 1 memoria EPROM 27XXX (la disponible) 1 memoria RAM 2016,6116 o la disponible 1 Push Button NA 10 resistencias de 2.2 KΩ 2 LEDS 2 resistencias de 220Ω 1 protoboard 1 Fuente de cd de 5 volts regulada 1 Analizador lógico ( o en su defecto osciloscopio multicanal) Cámara METODOLOGÍA (DESARROLLO DE LA PRÁCTICA): I.-Implemente el circuito mostrado en la figura de abajo en un protoboard, tomando en cuenta la distribución planeada para la realización del sistema completo. Microprocesadores PRÁCTICA N° 3: LAS MEMORIAS EPROM Y RAM Bus de Datos (D0-D7) RESET RESET YYRELOJ RELOJ Z80 +5V 220Ω Mem error 220Ω RST CLK ½ 74LS32 MEMWR WR MREQ Mem OK MEMRD RD EPROM EPROM 2716 2716 RAM RAM 6116 6116 WR OE RD CE CE HALT IORQ A11 1/4 74LS244 A B A11 C G2A 74LS14 A0-A10 A0-A10 Bus de Direcciones (A0-A15) Manera simplificada para decodificar direcciones de memoria Carlos Canto Q. El Mapa de Memoria a realizar con el sistema se muestra en la siguiente figura: M.C. Carlos E. Canto Quintal - 31 - Laboratorio de Microprocesadores Las memorias M ic r o p r o c e s a d or e s M A P A D E M E M O R IA P R O P U E S T O P A R A E L D E L S IS T E M A FFFFH SSININMMEEMMOORRIAIA 1000H 0F F F H RRAAMM 66111166 0800H 07F F H EEPPRROOMM 22771166 0000H C a rlo s C a n to Q . PRACTICA NUM. 3 CONEXIÓN DE LAS MEMORIAS EPROM AL SISTEMA Y RAM BUS DE DATOS D0-D7 BUS DE DIRECCIONES A0-A15 A0-A10 24 A11-A15 +5V +5V 16 A11 A12 A13 Z80 A14 A15 +5V RD MREQ WR 1 2 3 4 5 6 8 VCC Y0 Y1 Y2 Y3 74LS138 Y4 Y5 Y6 G2A Y7 G2B G1 GND A B C 15 14 13 12 11 10 9 7 8 7 6 5 4 3 2 1 23 22 19 21 18 20 12 4 5 1 2 +5V +5V VCC A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 VPP 2716 O0 O1 O2 O3 O4 O5 O6 O7 9 10 11 13 14 15 16 17 24 8 7 6 5 4 3 2 1 23 22 19 18 20 21 CE OE 12 GND 6 MEMRD 3 MEMW A15 A14 A13 A12 A11 A10 A9 A8 74LS32 SI A11=0 SI A11=1 SELECCIONA 2716 SELECCIONA 2016 0 0 0 0 0 X X SELECCIÓN DE CHIP VCC A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 2016 D0 D1 D2 D3 D4 D5 D6 D7 9 10 11 13 14 15 16 17 CE OE WE GND A7 A6 A5 A4 A3 X X X X X A2 A1 X X A0 X X SELECCIÓN DE LOCALIDAD DE MEMORIA C.CANTO II.- Implemente un programa para generar un retardo con una duración de 1 minuto aproximadamente ( tome el diagrama de flujo mostrado abajo, como ejemplo). Ensamble su programa a mano usando la tabla de instrucciones del manual del Z80. M.C. Carlos E. Canto Quintal - 32 - Laboratorio de Microprocesadores Las memorias Una vez ensamblado cárguelo, tecleándolo en el buffer del programador de memorias para después cargarlo en la EPROM Coloque la EPROM programada a su sistema, no olvide desenergizarlo previamente. M ICROPRO CESADORES Rutina generadora de retardos DELAY DELAY Cont2 Cont2ÅÅNN22 Cont1 Cont1ÅÅNN11 Cont1 Cont1ÅÅcont1-1 cont1-1 No Cont1=0 Cont1 =0 ?? si Cont2 Cont2ÅÅcont2-1 cont2-1 No Cont2=0 Cont2=0 ?? si Ret Ret Carlos Canto Q. Ejecute el programa y compruebe la duración del retardo, con un cronómetro, midiendo el tiempo transcurrido entre que se le aplica un RESET al Z80 y el que se prenda el LED en la salida HALT. III.- implemente un programa para realizar una prueba de integridad de la memoria RAM. Esta prueba consiste en escribir un patrón conocido (normalmente AAh, ya que consta de 0 y 1 alternados) a cada localidad de memoria y leerla de nuevo, comparar la lectura con el patrón previamente escrito a la memoria, si coinciden, realizar lo mismo a la siguiente localidad, y repetir hasta que se termine con todas las localidades, si en todos los casos lo que se lee es igual al patrón que se escribió entonces la memoria está en buenas condiciones y se debe prender el LED en HALT’. Si al hacer la lectura de alguna localidad no coincide con el patrón escrito, nos indica que la memoria está dañada y se debe prender el LED en IORQ’ (basarse en el diagrama de flujo mostrado abajo). Como lo más probable es que la memoria esté en buenas condiciones, se sugiere simular una falla de la memoria, quitándole la alimentación a la RAM y después correr el programa de nuevo y así corroborar que el programa detecta la falla de la RAM. M.C. Carlos E. Canto Quintal - 33 - Laboratorio de Microprocesadores Las memorias Calcule el tiempo que toma su microprocesador en hacer la prueba de la RAM completa. Ensamble su programa a mano usando la tabla de instrucciones del MICROPROCESADORES Rutina para checar la memoria RAM Ram_test Ram_test HLÅ HLÅDirección Direccióninicial inicial AÅpatrón AÅpatrónde deprueba prueba (HL) (HL)ÅÅAA AA ÅÅ(HL) (HL) HL HL ÅÅHL-1 HL-1 Es Es A= A= patrón patrón de de prueba prueba ?? No si No Es Esúltima última localidad localidadRAM RAM ?? si Halt Halt Output Output Carlos Canto Q. manual del Z80. Una vez ensamblado cárguelo, tecleándolo en el buffer del programador de memorias para después cargarlo en la EPROM SUGERENCIA DIDÁCTICA: Ejercicio 1 Diseñar un banco de memorias de 32 Kbytes de RAM y 32 Kbytes de ROM para un microprocesador Z80. Se dispone de chips de 4K *8 de RAM y de 16 K * 8 de ROM Ejercicio 2 Construir el mapa de memoria para la decodificación implementada en la figura. ¿En que direcciones se acceden al primer byte de cada memoria que componen los 64K? Ejercicio 3 Diseñar la decodificación de un sistema que conste de 32K de ROM y 16K de RAM. Para la RAM se dispone de 2 chips de 8K*8 cada uno mientras que la ROM M.C. Carlos E. Canto Quintal - 34 - Laboratorio de Microprocesadores Las memorias es un solo chip de 32K*8. Se pretende que la RAM esté en lo más alto del mapa de m e m o r i a m i e n t r a s q ue la ROM esté al principio. El resto del espacio de memoria deberá ser mapeado para cada una de las posibilidades que se muestran en las figuras. REPORTE: I.- Llene la tabla de abajo con el programa para generar retardo. Usando el menú de instrucciones del manual del Z80, ensamble a mano su programa y repórtelo en la tabla, no olvide los comentarios. II.- reporte los cálculos realizados para ajustar el tiempo de retardo a 1 minuto, así como el tiempo real obtenido con el cronómetro. Dirección de memoria 0000 Etiqueta Mnemónico Código de Operación 0001 0002 0003 0004 0005 0006 0007 0008 0009 000A 000B 000C M.C. Carlos E. Canto Quintal - 35 - Ciclos de Reloj (T) Comentarios Laboratorio de Microprocesadores Las memorias TIEMPO CALCULADO TIEMPO CRONOMETRADO III.- complete la tabla de abajo con el programa de prueba de la RAM , ensamblando a mano . Reporte también el tiempo calculado para realizar la prueba de la RAM TIEMPO CALCULADO PARA CHEQUEO COMPLETO DE LA RAM Dirección de memoria 0000 0001 Etiqueta Mnemónico Código de Operación 0002 0003 0004 0005 0006 0007 0008 0009 000A 000B 000C 000D 000E 000F 0010 0011 0012 0013 0014 0015 0016 0017 0018 0019 M.C. Carlos E. Canto Quintal - 36 - Ciclos de Reloj (T) Comentarios Laboratorio de Microprocesadores Las memorias BIBLIOGRAFÍA: • • Manual de Zilog Ramesh S. Gaonkar The Z80 Microprocessor: Architecture, Interfacing, Programming, and Design M.C. Carlos E. Canto Quintal - 37 -