Paginación - Universidad Tecnológica Nacional

Anuncio

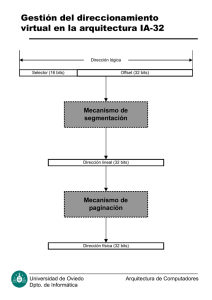

Paginación Técnicas Digitales III Ing. Gustavo Nudelman 2013 Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Paginación - Introducción La paginación permite que la direcciones a las que hace referencia un código de programa, sean reubicadas en direcciones físicas especificas utilizando bloques de tamaño fijo (Páginas físicas). • Esta reubicación se hace por medio de tablas • Por razones de eficiencia, no se trata de una única tabla sino de una estructura Jerárquica de n tablas o niveles de paginación • Una vez que se dispone de la estructura de tablas se enciende el bit PG de CR0 para activar la unidad de paginación. • Las Arquitecturas x86 permiten paginas de 4k, 2M y 4M. Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Estructura de la MMU Sel:Offset Unidad de Segmentación Dir Lienal BIT PG 0 Dir. Física 1 Unidad de Paginación • Por simplicidad, si activamos PG es conveniente que la unidad de segmentación trabaje con el modo FLAT Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Paginación 4k - Introducción • Las páginas son contiguas y a diferencia de los segmentos no se solapan. • Los sistemas operativos como Unix desde su concepción, trabajan con este modelo de memoria • Trabajar con tamaños fijos provee una ventaja para la administración de memoria virtual • En los primeros procesadores (hasta el Pentium Pro), el tamaño de página es fijo: 4Kbytes. • A partir del Pentium Pro cada tarea puede optar por tener páginas de 4 Kbytes, 2 Mbytes, o 4 Mbytes. • El máximo tamaño de un espacio lineal en IA32 es 4 GB, sin embargo con la unidad de paginación podremos administrar mas memoria física Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Tabla de paginas • Se trata de una tabla de descriptores de página • Se requieren 20 bits para la dirección base ya que las páginas no se solapan y no se necesita especificar el limite ya que son de tamaño fijo • Descriptores de 4 bytes. • En cada entrada se almacena el número de frame físico donde se almacena la página y algunos bits de control. • En Intel se dedican los 20 primeros bits a almacenar el número de frame y los 12 restantes a guardar información de control. • Con 20 bits podemos direccionar 1M descriptores siendo una tabla de 4MB Poco práctico Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Paginación de memoria en 2 niveles 12 Atributos Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Entrada del directorio de página (PDE) • • • • • • • • • • • Page-Table base Addres: Apunta a la base de la tabla. Solo se necesitan 20 bits para acceder a la base de la tabla de páginas que puede estar en cualquier múltiplo de 4K del espacio lineal. Avail: Disponible para el programador de sistemas G (Global): Controla el comportamiento del TLB cuando CR3 es recargado. Debe ser 0 para paginación de 4k. PS (Page size): 0 para 4K y 1 para 4MB AVL: Reservado – Siempre 0 A (Accessed): Se pone en 1 cada vez que se realiza una lectura o escritura PCD (Page Cache Disabled): si es 1 lo apuntado por el PDE correspondiente no será “cacheado”. No usar para I/O mapeado en memoria. PWT (Page Write Through): Política de gestión de cache U/S (User/Supervisor): Si es 1 puede ser accedida por niveles 0,1,2 y 3. Si es 0 solo puede ser accedida por niveles 0, 1 y 2 R/W: 0=Read Only 1=Readable & Writable P (Presente): La página esta presente en memoria, de lo contrario provocará una excepción 14 (La dirección lineal queda en CR2) Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Entrada de tabla de página • Page-Table base Address: Apunta a la base del frame de la página. • Page Attribute Table index: Soportado a partir de pentium III. Debe permanecer en 0 • D (Dirty): El procesador lo cambia a 1 si la pagina apuntada por el descriptor fue escrita. Y permanece en 1 hasta que sea puesto a 0 por el software. Se lo utiliza para indicar que ha sido modificado y difiere de las paginas en el espacio de swap. • El resto de los atributos son análogos al descriptor de tabla pero a nivel de página. Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Protección a nivel de páginas • Se combina con la protección a nivel de segmento aportando granularidad al sistema de protección dentro de un mismo segmento • Siempre se evalúa primero la protección a nivel de segmento • Los CPLs 0,1,2 del segmento se mapean en el nivel supervisor de las páginas mientras que el nivel 3 se corresponde con el nivel usuario. • En modo supervisor se accede a todas las páginas mientras que en nivel usuario solamente a las que poseen en su descriptor el bit U/S=1 • La protección a nivel de página no pisa la protección a nivel de segmento. Los permisos de escritura en las páginas no funcionaran si no existe el permiso a nivel de segmento. • La excepción por excelencia del sistema de protección de páginas es la 0Eh Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Combinación de protección a nivel de directorio y página Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Registros de control asociados Apunta a la base del directorio de Páginas Activa la Paginación Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Segmentación y Paginación CR3 Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Paginación Resumen • Nos permite dividir la memoria en bloques de tamaño fijo llamados páginas cada una con atributos propios • Permite virtualizar el espacio lineal permitiendo que diferentes aplicaciones trabajen en zonas diferentes aunque las mismas se refieran al mismo espacio lineal. • Si el sistema de paginación hace coincidir la dirección lineal con la dirección física, decimos que se trata de “Identity mapping” • Las tablas de correspondencia de la páginas mas frecuentemente utilizadas se almacenan en una memoria cache del propio procesador llamada TLB (Translation Lookaside Buffers) Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Lab 1. Programa “Hello World” con 2 páginas 2. Comando de Bochs “Info Tab” 3. Direcivas %rep y %assign. 4. Ejercicio teórico Subtitulo o nombre del capitulo Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Universidad Tecnológica Nacional Ejercicio teórico Subtitulo o nombre del capitulo Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Universidad Tecnológica Nacional Universidad Tecnológica Nacional - Facultad Regional Buenos Aires • Analicemos la dirección Lineal ds:esi = 23h:9F0A02EBh 5 descriptor de la GDT con RPL 11 1001111100 0010100000 27Ch 0A0h 001011101011 2EBhh Universidad Tecnológica Nacional - Facultad Regional Buenos Aires • Según el enunciado, CR3=0000F000h 0000F 000 4096 Bytes El DTP está ubicado en la pagina 15 del espacio físico La Base_DTP=F000h Universidad Tecnológica Nacional - Facultad Regional Buenos Aires • Recordando el directorio de página obtenido El inicio de la tabla de páginas se encuentra dentro del descriptor que esta en Base_DTP+ (n*4) F000 + (27C*4)=0xF9F0 Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Recordemos que PTBAn debe apuntar a la base de la tabla de páginas, y como sabemos que esta esta en 10000h (4K luego del Directorio) PTBAn debe ser 10h ya que 10h*PageSize =10000h Universidad Tecnológica Nacional - Facultad Regional Buenos Aires • Recordando la tabla obtenida. El descriptor de página se encuentra en Base_TP+ (n*4) 10000h + (0xA0*4)=0x10280 Evoluciones y extensiones del sistema de paginación en IA32 Subtitulo o nombre del capitulo Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Universidad Tecnológica Nacional Paginación en 4MB - PSE El bit 4 del registro CR4 (page size extensions) habilita la posibilidad de combinar páginas de 4K y 4MB. Directorio de tabla de páginas Pages directory entries (PDE) 1 = 4MB 0 = 4KB Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Paginación de memoria con PSE-36 • Desde Pentium Pro se advirtió que 4GB de memoria física serian insuficientes. • Se implementa PSE-36 con el Pentium III, donde utilizando PSE permite extender las líneas físicas de direccionamiento a 36 bits en procesadores de 32 bits • Se puede verificar la existencia de PSE con la instrucción CPUID • En procesadores de 64 bits, y utilizando legacy mode, las líneas físicas se extienden a 40 bits en. • Tanto en IA32 como en legacy mode mediante a un esquema de paginación se puede direccionar mas memoria física manteniendo un esquema de direcciones lineales de 32 bits. • Se pueden utilizar y combinar en un mismo sistema páginas de 4K y de 4M. Esto se dictamina por entrada de directorio según sea el valor del bit 7 (PDE.PS) Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Descriptores de directorio de página con PSE-36 • • PDE en procesadores de 32 bit utilizando la extensión a 36 bits PDE en Legacy mode para procesadores de 64 bits Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Physical Adress extension (PAE) • Este modo de extender el direccionamiento físico a partir de un direccionamiento lineal de 32 bits aparece con el Pentium pro. (Verificar extensión PAE con CPUID) • Se debe habilitar el bit 5 del registro CR4 (una vez habilitada la paginación) • Permite la extensión del direccionamiento físico a 36 bits en IA32, y a 48 bits en modo IA32e • Utiliza descriptores de 64 bits • Utiliza una estructura donde a diferencia de los casos anteriores, el directorio de tablas no esta apuntado por CR3 sino por otra tabla llamada “page directory pointer table” PDE y PTE son de 9 bits • Trabaja con páginas de 4K o 2MB Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Registros de control asociados Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Paginación en 4K con PAE (dirección lineal de 32 bits) Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Paginación en 4K con PAE Descriptores PDPTE PDE PTE Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Paginación en 2MB con PAE (dirección lineal de 32 bits) Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Paginación en 2MB con PAE Descriptores PDPTE PDE Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Paginación de memoria en 4K con PAE 24 bits Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Paginación de memoria en 2M con PAE 24 bits Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Paginación con PAE - Resumen • Permite extender el direccionamiento de memoria física manteniendo espacios lineales de 32 bits. • Esto es gracias a que los descriptores de las tablas son de 64 bits. • También tenemos un nuevo nivel o tabla llamado PDPT • Sin embargo bajo cualquier contexto dado de PAE, y donde CR3 apunta a una estructura jerárquica de n tablas podemos observar que no podemos manejar mas de 4GB. • Tengamos en cuenta que podemos cambiar CR3, generando un nuevo contexto de paginación con nuevas tablas que apunten a nuevas páginas. (Ahora cualquier dirección física de base de página es de 27 bits) Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Lab “Paginación con PAE” Subtitulo o nombre del capitulo Universidad Tecnológica Nacional - Facultad Regional Buenos Aires Universidad Tecnológica Nacional